# Parasitics and Current-Dispersion Modeling of AlGaN/GaN HEMTs Fabricated on Different Substrates using the Equivalent-Circuit Modeling Technique

Mohamad Alsabbagh, B.S.

Thesis submitted to the University of Ottawa in partial fulfillment of the requirements for the degree of

Master of Applied Science in Electrical Engineering

Ottawa-Carleton Institute for Electrical and Computer Engineering School of Electrical Engineering and Computer Sciences University of Ottawa

© Mohamad Alsabbagh, Ottawa, Canada, 2020

## Abstract

Electrical equivalent circuit modeling of active components is one of the most important approaches for modeling high-frequency high-power devices. Amongst the most used microwave devices, AlGaN/GaN HEMTs demonstrated their superior performance, making them highly suitable for 5G, wireless and satellite communications. Despite the remarkable performance of AlGaN/GaN HEMTs, these devices reside on substrates that invoke limitations on the operating-frequency, power-efficiency, and current dispersion phenomenon. Also, there is a limitation in present parameters extraction techniques being not able to consider both the substrate effect (Silicon, Silicon Carbide, and Diamond) and the asymmetrical GaN HEMT structure. In this thesis work, a single extrinsic parameters extraction technique using a single small-signal topology takes into account both the asymmetrical GaN HEMT structure and the different substrate types with their parasitic conduction will be developed and studied for the first time. Moreover, large-signal modeling using Quasi-Physical Zone Division technique has been applied to both GaN/D and GaN/SiC to model the isothermal-trapping free drain current, and combined with a new simple technique for comparing performance between active devices in terms of current-dispersion. The models were verified by simulating the smallsignal S-parameters, large-signal IV characteristics, and single-tone load-pull. High accuracy was achieved compared to the measurement data available in the technical literature and obtained from fabricated devices.

# Acknowledgments

I would like to thank Almighty Allah for giving me the strength, knowledge and the opportunity to do this research. A great deal of appreciation and respect goes to both my supervisor Professor Jeongwon Park and my co-supervisor Professor Mustapha Yagoub for their help, advice, and guidance in my thesis work. A special thanks to my family and close friends for their motivational and continuous support throughout the course of my studies. Last but not least, I would like to thank Professor Yuehang Xu from University of Electronic Science and Technology of China and Professor Anwar Jarndal from University of Sharjah for providing us with data necessary to complete this work. Also, University of Ottawa for allowing me the opportunity to study and do this research.

# Table of Contents

| Chapter   | 1: Introduction                                                      | 1   |

|-----------|----------------------------------------------------------------------|-----|

| 1.1       | Motivations                                                          | . 1 |

| 1.2       | Literature Review                                                    | . 3 |

| 1.3       | Objectives                                                           | . 6 |

| 1.4       | Original contributions                                               | . 8 |

| 1.5       | Outline                                                              | . 8 |

| Refere    | ences                                                                | 11  |

| Chapter 2 | 2: Technical Background                                              | 15  |

| 2.1       | Why GaN HEMT?                                                        | 15  |

| 2.2       | Fundamentals of GaN HEMT                                             | 17  |

| 2.2.      | 1 Heterojunctions                                                    | 17  |

| 2.2.      | 2 AlGaN/GaN as a heterojunction and the formation of 2DEG            | 18  |

| 2.2.      | 3 Polarization effects and AlGaN/GaN as a HEMT                       | 19  |

| 2.3       | Non-ideal effects of AlGaN/GaN HEMT                                  | 22  |

| 2.3.      | 1 Current Dispersion due to self-heating and charge-trapping effects | 23  |

| 2.3.      | 2 Parasitic effects in GaN HEMT                                      | 26  |

| 2.3.      | 3 Substrate choice                                                   | 29  |

| 2.4       | Typical characteristics and measurements                             | 32  |

| 2.4.      | 1 Two-port network parameters and their measurements                 | 32  |

| 2.4.      | 2 Static DC I-V characteristics and measurements                     | 37  |

| 2.4.      | 3 Pulsed DC I-V characteristics and measurements                     | 38  |

| 2.4.      | 4 Uncertainties in measurements                                      | 39  |

| 2.5       | Modeling approaches                                                  | 40  |

| 2.5.      | 1 Physical-based model                                               | 40  |

| 2.5.2        | Behavioral-based model                                  | 40           |

|--------------|---------------------------------------------------------|--------------|

| 2.5.3        | Equivalent Circuit-based model                          | 40           |

| 2.6 C        | onclusion                                               | 41           |

| Referenc     | es                                                      |              |

| Chapter 3: S | Small-Signal Modeling and Proposed Extraction Technique | 46           |

| 3.1 S        | mall-signal model topologies                            | 46           |

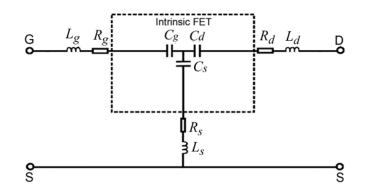

| 3.1.1        | Intrinsic Circuit                                       | 47           |

| 3.1.2        | Extrinsic Circuits                                      |              |

| 3.2 R        | F Performance metrics                                   | 51           |

| 3.3 E        | xtrinsic parameters extraction techniques               | 54           |

| 3.3.1        | Extraction using open, short and thru test structures   |              |

| 3.3.2        | Extraction using cold pinch-off and cold forward        | S-parameters |

| measurem     | ents                                                    | 56           |

| 3.4 P        | roposed extrinsic parameters extraction technique       | 56           |

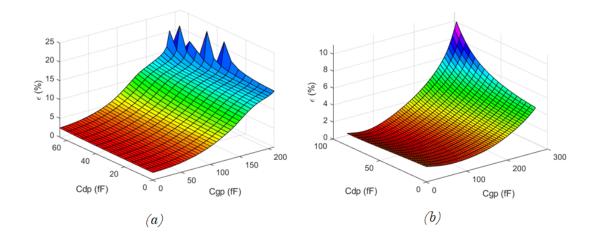

| 3.4.1        | Phase 1: $C_{gs}$ and $C_{ds}$ estimation               | 60           |

| 3.4.2        | Phase 2: Substrate model extraction                     | 64           |

| 3.5 P        | roposed optimization technique                          | 68           |

| 3.6 Ir       | trinsic parameters extraction                           | 72           |

| 3.7 R        | esults and discussion                                   | 73           |

| 3.7.1        | Extrinsic parameters extraction results                 | 73           |

| 3.7.2        | Intrinsic parameters extraction results                 | 77           |

| 3.8 A        | dditional model validations                             | 88           |

| 3.8.1        | GaN HEMT on Silicon substrate                           | 88           |

| 3.8.2        | Graphene-Based FET                                      |              |

| 3.9 C        | onclusion                                               | 100          |

| Referenc     | es                                                      |              |

| Chapter 4: Large-Signal Modeling |                                                     |  |

|----------------------------------|-----------------------------------------------------|--|

| 4.1                              | Large-signal model topologies                       |  |

| 4.1                              | .1 Quasi-Static Large-signal topology               |  |

| 4.1                              | .2 Non Quasi-Static Large-signal topology           |  |

| 4.1                              | .3 Proposed Large-signal topology                   |  |

| 4.2                              | Isothermal trapping-free drain current extraction   |  |

| 4.2                              | .1 Empirical model                                  |  |

| 4.2                              | .2 Surface Potential model                          |  |

| 4.2                              | .3 Quasi-Physical Zone Division model               |  |

| 4.3                              | Results of QPZD modeling technique                  |  |

| 4.4                              | Charge-trapping and self-heating modeling           |  |

| 4.5                              | Conclusion                                          |  |

| Refere                           | ences                                               |  |

| Chapter                          | 5: ADS model, Overall Results and Validations       |  |

| 5.1                              | ADS model                                           |  |

| 5.2                              | S-parameters simulations                            |  |

| 5.3                              | Static IV-characteristics                           |  |

| 5.4                              | Single-tone Load-pull simulations                   |  |

| 5.5                              | Single-tone input power-swept simulations           |  |

| 5.6                              | Conclusion                                          |  |

| Refere                           | ences                                               |  |

| Chapter                          | 6: Conclusions and Future Work                      |  |

| 6.1                              | Conclusions from the research results               |  |

| 6.2                              | Future work                                         |  |

| Appendi                          | ix I: Relationships Between S- Z- and Y- parameters |  |

# List of Figures

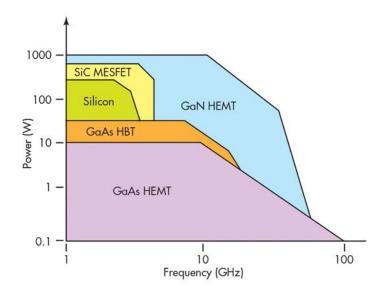

| 2.1  | Operating power and frequencies for different technologies [3]                                        | 16 |

|------|-------------------------------------------------------------------------------------------------------|----|

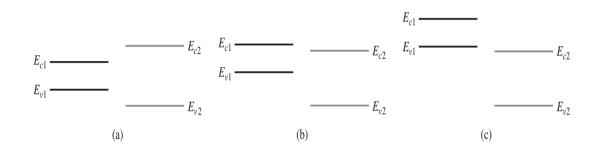

| 2.2  | Types of heterojunctions based on alignments: (a) Straddling, (b) Staggered                           |    |

|      | and (c) Broken Gap [2].                                                                               | 18 |

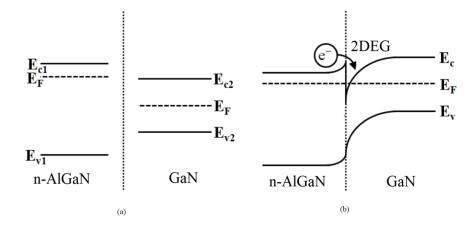

| 2.3  | AlGaN/GaN heterostructure energy band diagram (a) before equilibrium                                  |    |

|      | and (b) at equilibrium [4]                                                                            | 19 |

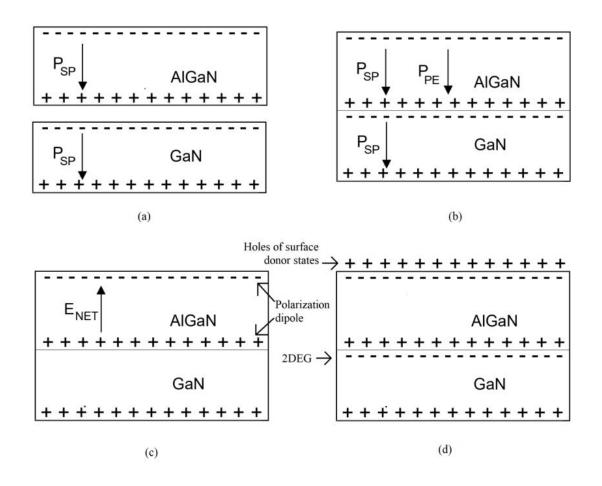

| 2.4  | Illustration of polarization effects on forming 2DEG in AlGaN/GaN                                     |    |

|      | heterojunction: (a) Spontaneous polarization before the heterojunction, (b)                           |    |

|      | The junction creates tensile stress and piezoelectric polarization, (c)                               |    |

|      | interface sheet charges interact to form the polarization dipole and $E_{\mbox{\scriptsize NET}}$ and |    |

|      | (d) The dipole and $E_{\text{NET}}$ form the 2DEG with electrons of surface donor                     |    |

|      | states [4]                                                                                            | 21 |

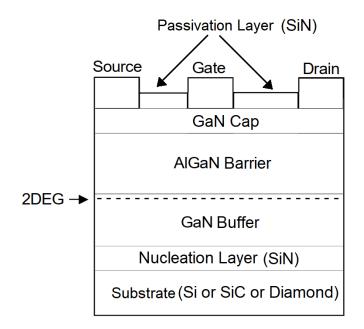

| 2.5  | Basic structure of AlGaN/GaN HEMT [5].                                                                | 22 |

| 2.6  | Energy band diagram of AlGaN/GaN HEMT with (a) $V_G = 0$ and (b) $V_G < 0$                            |    |

|      | [2]                                                                                                   | 22 |

| 2.7  | Static DC (non-pulsed) and Pulsed I-V measurements for arbitrary GaN                                  |    |

|      | HEMT [8]                                                                                              | 23 |

| 2.8  | Illustration of passivation layer inclusion in GaN HEMT: (a) trapped                                  |    |

|      | electrons on surface and reduction in 2DEG density and (b) passivation                                |    |

|      | layer preventing electron traps                                                                       | 25 |

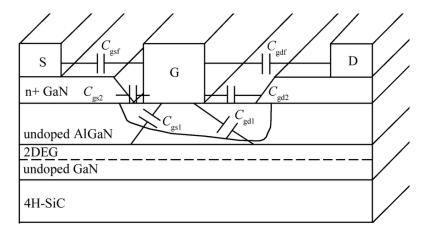

| 2.9  | Intrinsic capacitances of GaN HEMT [14].                                                              | 27 |

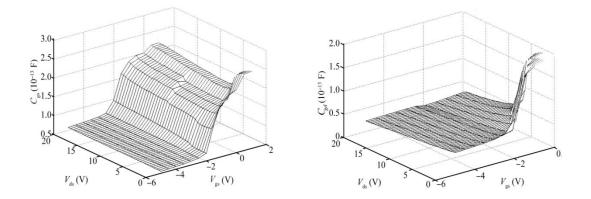

| 2.10 | Typical $C_{gs}$ and $C_{gd}$ plots under different bias conditions for GaN HEMT                      |    |

|      | [14]                                                                                                  | 28 |

| 2.11 | GaN HEMT full structure with all defined layers.                                                      | 30 |

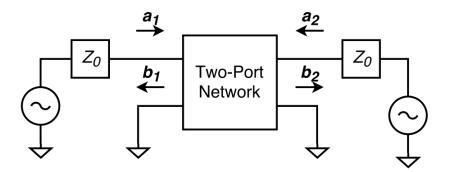

| 2.12 | Two-port network for S-parameter measurement [27].                                                    | 35 |

| 2.13 | Typical setup for measuring S-parameters [28].                                                        | 36 |

| 2.14 | Difference between device plane reference and measurement plane                                       |    |

|      | reference on accuracy of S-parameters measurements [29]                                               | 37 |

| 2.15 | Static DC I-V characteristics [4]                                                                     | 38 |

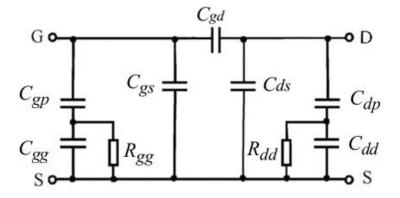

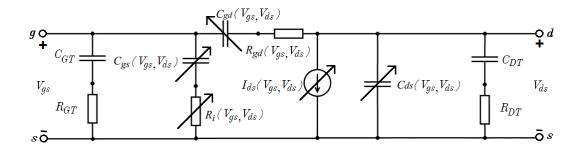

| 3.1  | Parasitic and conductive elements of GaN HEMT showing intrinsic (red)               |

|------|-------------------------------------------------------------------------------------|

|      | and extrinsic (blue) elements [1]47                                                 |

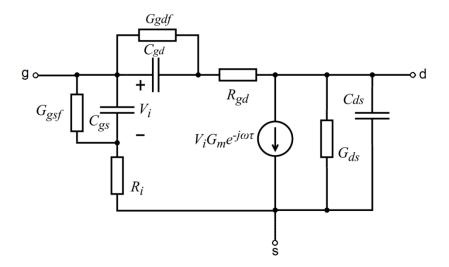

| 3.2  | Intrinsic small-signal model of GaN HEMT [2]48                                      |

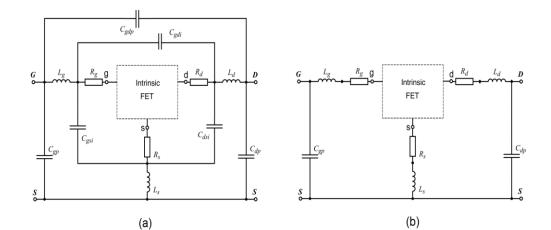

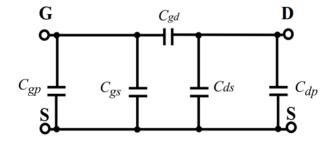

| 3.3  | Different circuit topologies for GaN HEMT (a) for large periphery gates             |

|      | with no substrate model, (b) GaN/SiC model for small devices with no                |

|      | substrate model, (c) model for small devices with substrate model (d)               |

|      | another configuration for substrate model and (e) N-RC substrate model              |

|      | [2]-[10]                                                                            |

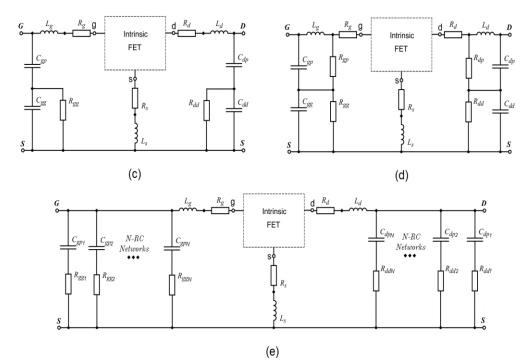

| 3.4  | Small-signal model for calculations of <i>f</i> <sub>t</sub>                        |

| 3.5  | Small-signal model for $f_{max}$ formulation                                        |

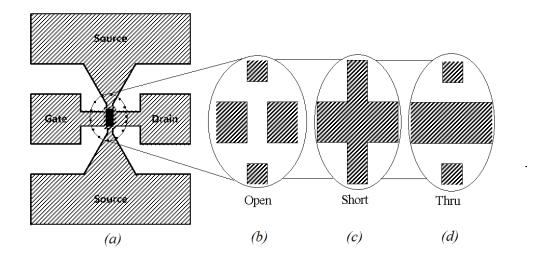

| 3.6  | Different test structures for GaN HEMT: (a) normal, (b) open, (c) short and         |

|      | (d) thru structures [12]55                                                          |

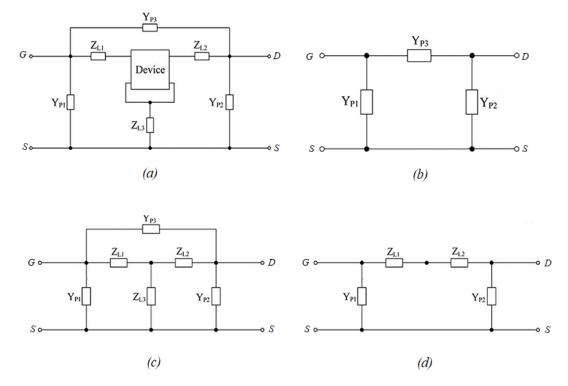

| 3.7  | Circuit models for test structures of GaN HEMT: (a) normal, (b) open, (c)           |

|      | short and (d) thru structures [13]                                                  |

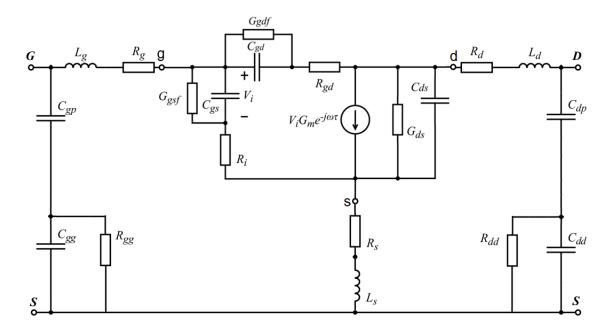

| 3.8  | Proposed equivalent circuit-small-signal model [2]                                  |

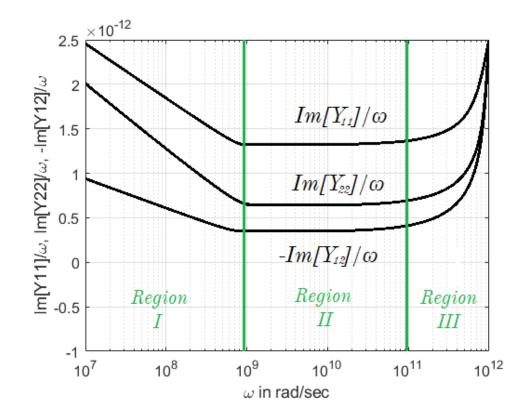

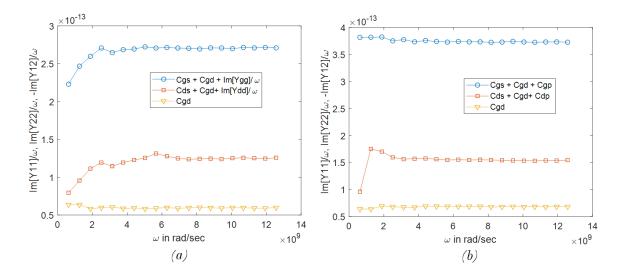

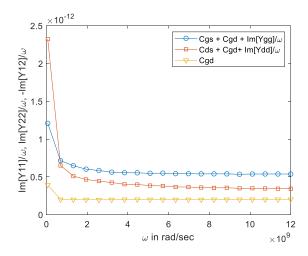

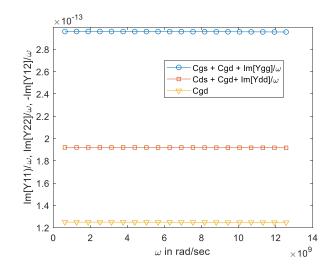

| 3.9  | Imaginary of Y over $\omega$ plot showing three different regions of interest       |

| 3.10 | GaN HEMT extrinsic network at Region I [23]60                                       |

| 3.11 | GaN HEMT extrinsic model at Region II [4].                                          |

| 3.12 | GaN HEMT at Region III after de-embedding the extrinsic capacitances62              |

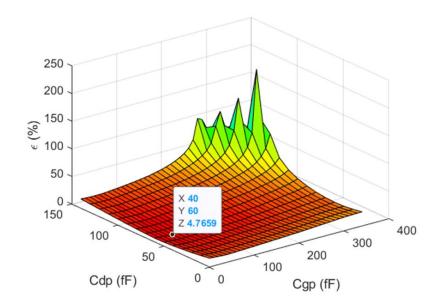

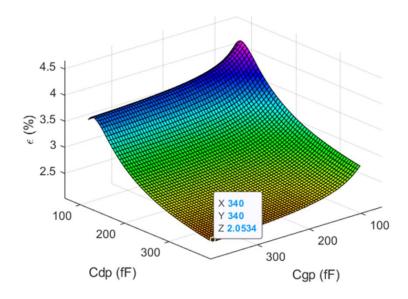

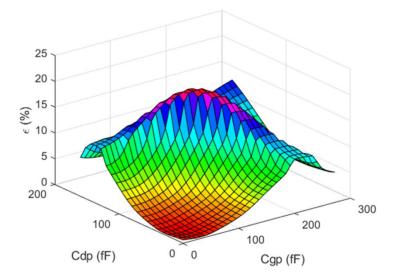

| 3.13 | $C_{gp}$ and $C_{dp}$ scanning plots to determine the minimum error for (a) GaN/D   |

|      | and (b) GaN/SiC64                                                                   |

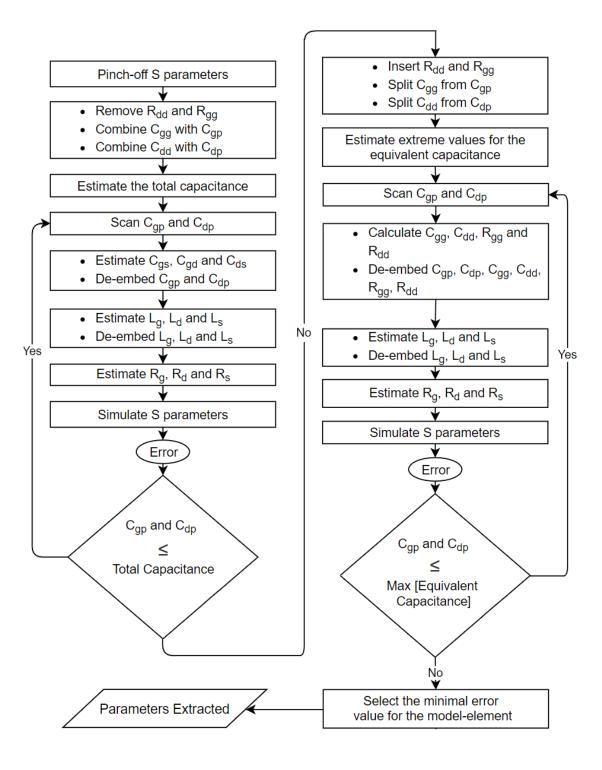

| 3.14 | Flow chart of the extrinsic parameters extraction technique                         |

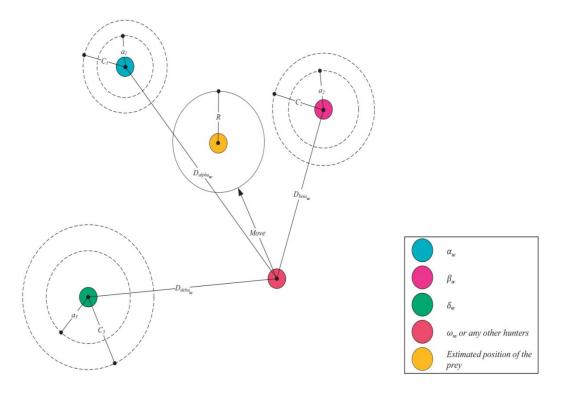

| 3.15 | Position Updates in GWO [25]70                                                      |

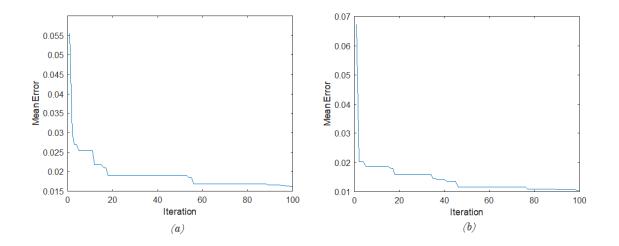

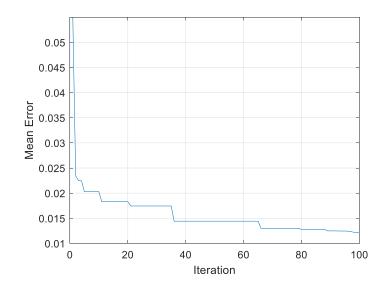

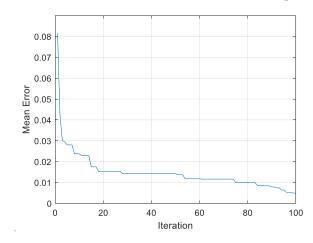

| 3.16 | Convergence of GWO for optimizing the (a) GaN/D and (b) GaN/SiC                     |

|      | parameters71                                                                        |

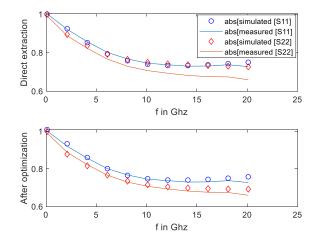

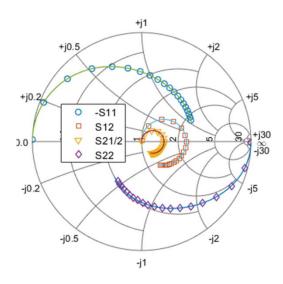

| 3.17 | Comparison between $S_{11}$ and $S_{22}$ for GaN/Si before and after optimization71 |

| 3.18 | Extrinsic capacitances and substrate parameters extraction for (a) GaN/D            |

|      | and (b) GaN/SiC74                                                                   |

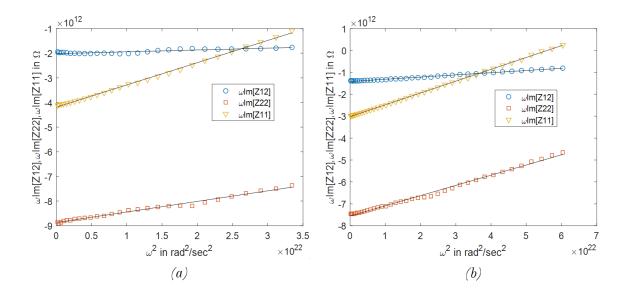

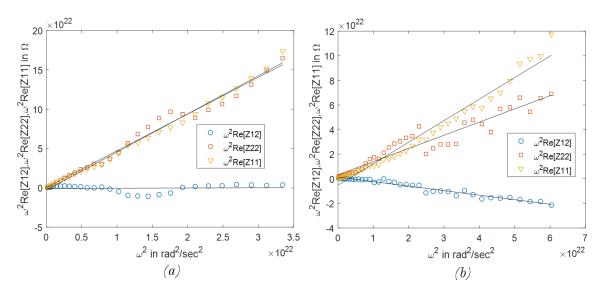

| 3.19 | Extrinsic inductances extraction for (a) GaN/D and (b) GaN/SiC75                    |

| 3.20 | Extrinsic series resistances extraction for (a) GaN/D and (b) GaN/SiC75             |

|      |                                                                                     |

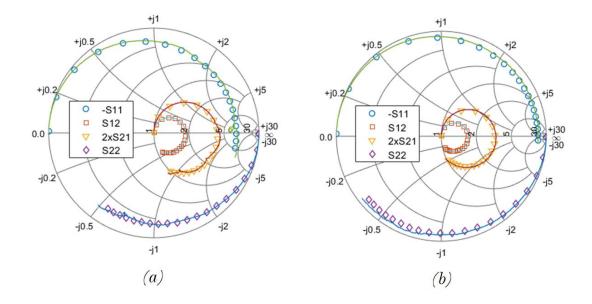

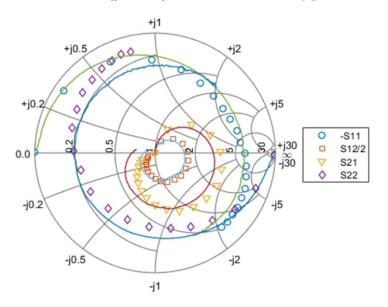

| 3.21 | Comparison between measurements (lines) and optimized S-parameters simulations (symbols) for the extrinsic network of (a) GaN/D and (b) |    |

|------|-----------------------------------------------------------------------------------------------------------------------------------------|----|

|      | GaN/SiC for frequencies from 0.1 to 40 GHz.                                                                                             | 77 |

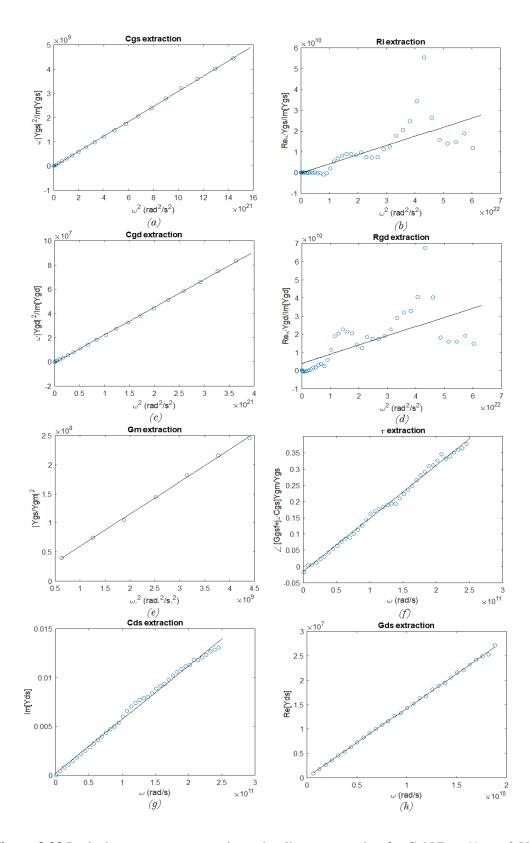

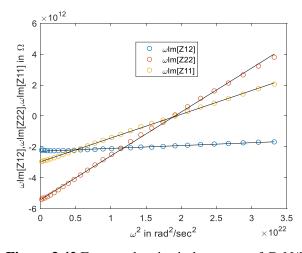

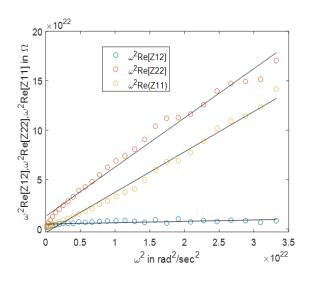

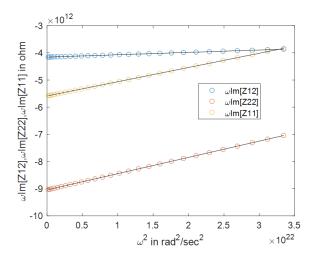

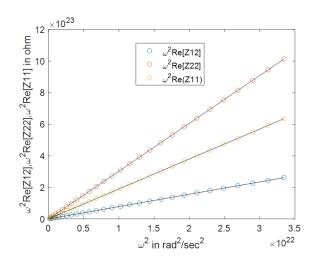

| 3.22 | Intrinsic parameters extraction using linear regression for GaN/D at $V_{GS}$ = -                                                       |    |

|      | 2 V and $V_{DS} = 20$ V showing (a) $C_{gs}$ , (b) $R_i$ , (c) $C_{gd}$ , (d) $R_{gd}$ , (e) $G_m$ , (f) $\tau$ , (g)                   |    |

|      | $C_{ds}$ and (h) $G_{ds}$ extraction                                                                                                    | 82 |

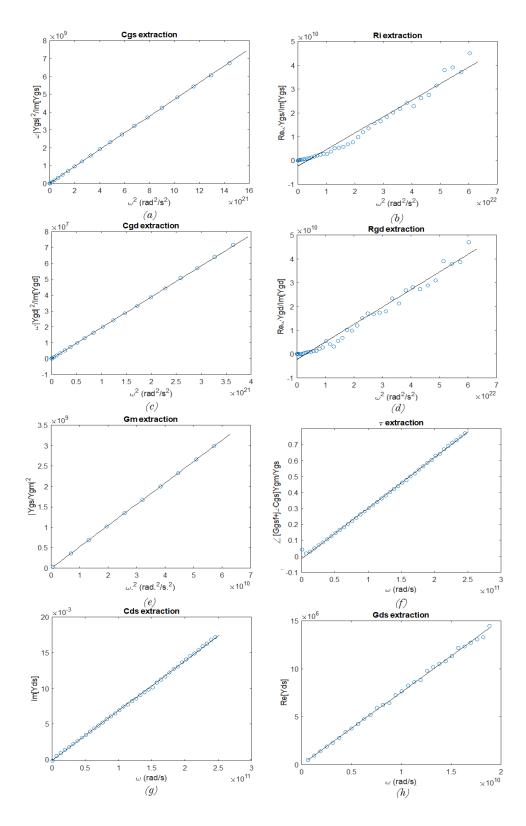

| 3.23 | Intrinsic parameters extraction using linear regression for GaN/SiC at $V_{GS}$ =                                                       |    |

|      | -1 V and $V_{DS} = 30$ V showing (a) $C_{gs}$ , (b) $R_i$ , (c) $C_{gd}$ , (d) $R_{gd}$ , (e) $G_m$ , (f) $\tau$ ,                      |    |

|      | (g) $C_{ds}$ and (h) $G_{ds}$ extraction.                                                                                               | 83 |

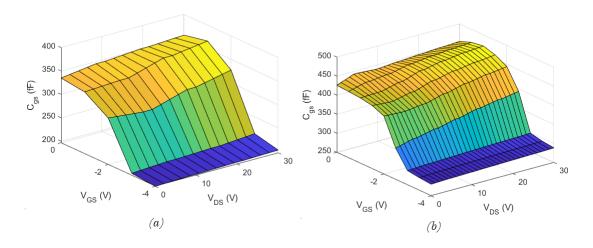

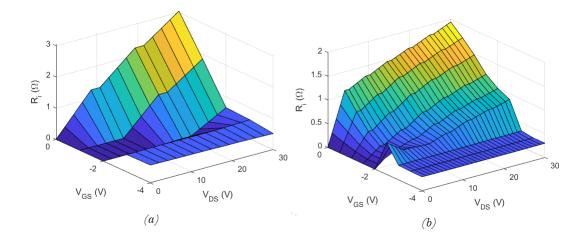

| 3.24 | $C_{gs}$ at multiple bias points for (a) GaN/D and (b) GaN/SiC.                                                                         | 84 |

| 3.25 | $R_i$ at multiple bias points for (a) GaN/D and (b) GaN/SiC                                                                             | 84 |

| 3.26 | $G_{gsf}$ at multiple bias points for (a) GaN/D and (b) GaN/SiC.                                                                        | 84 |

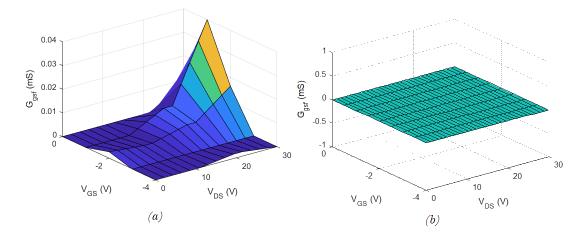

| 3.27 | $G_{gdf}$ at multiple bias points for (a) GaN/D and (b) GaN/SiC                                                                         | 85 |

| 3.28 | $C_{gd}$ at multiple bias points for (a) GaN/D and (b) GaN/SiC                                                                          | 85 |

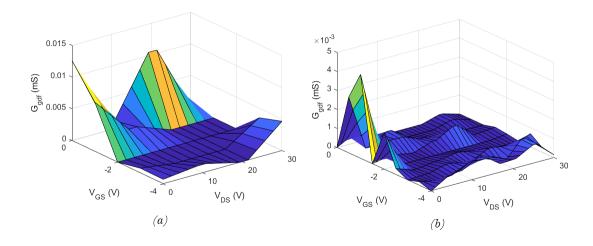

| 3.29 | $R_{gd}$ at multiple bias points for (a) GaN/D and (b) GaN/SiC.                                                                         | 85 |

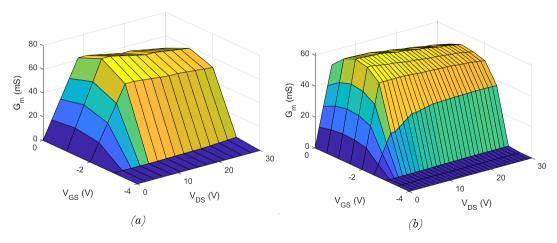

| 3.30 | $G_m$ at multiple bias points for (a) GaN/D and (b) GaN/SiC.                                                                            | 86 |

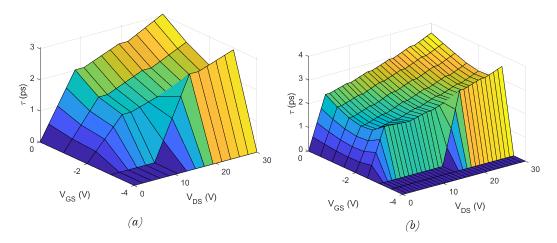

| 3.31 | $\tau$ at multiple bias points for (a) GaN/D and (b) GaN/SiC                                                                            | 86 |

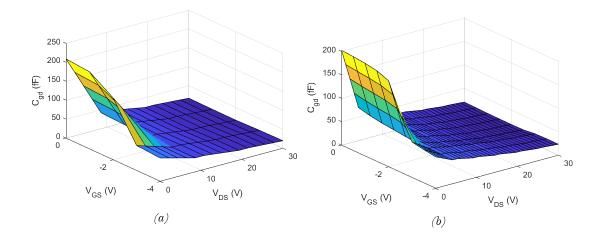

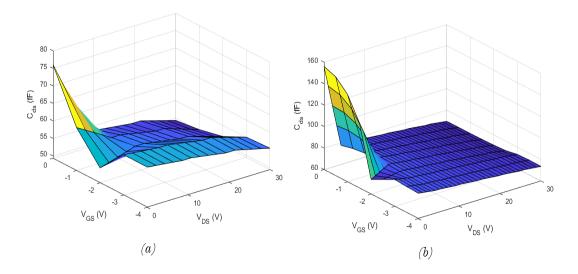

| 3.32 | $C_{ds}$ at multiple bias points for (a) GaN/D and (b) GaN/SiC.                                                                         | 86 |

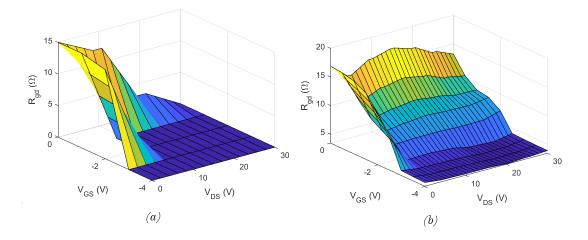

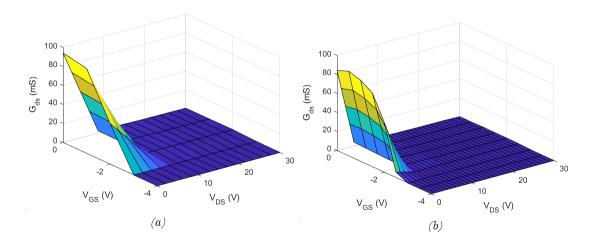

| 3.33 | $G_{ds}$ at multiple bias points for (a) GaN/D and (b) GaN/SiC.                                                                         | 87 |

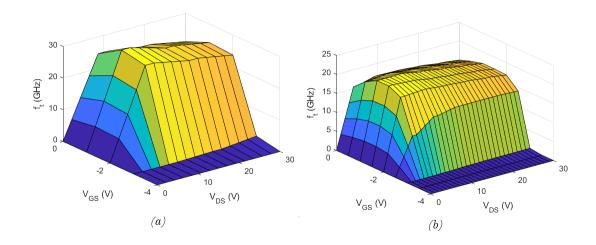

| 3.34 | $f_t$ at multiple bias points for (a) GaN/D and (b) GaN/SiC.                                                                            | 87 |

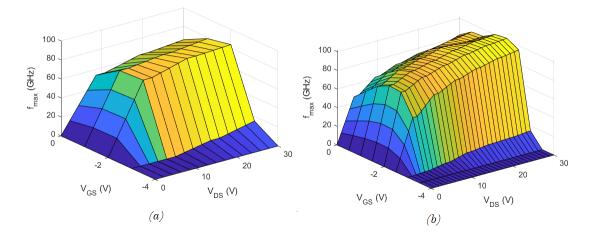

| 3.35 | $f_{max}$ at multiple bias points for (a) GaN/D and (b) GaN/SiC                                                                         | 87 |

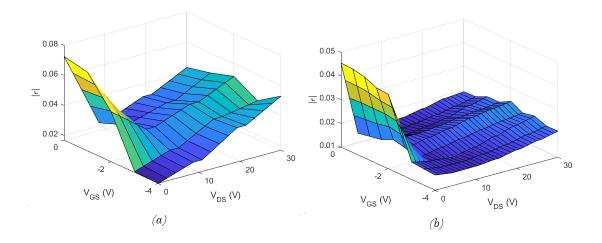

| 3.36 | $ \varepsilon $ at multiple bias points for (a) GaN/D and (b) GaN/SiC                                                                   | 88 |

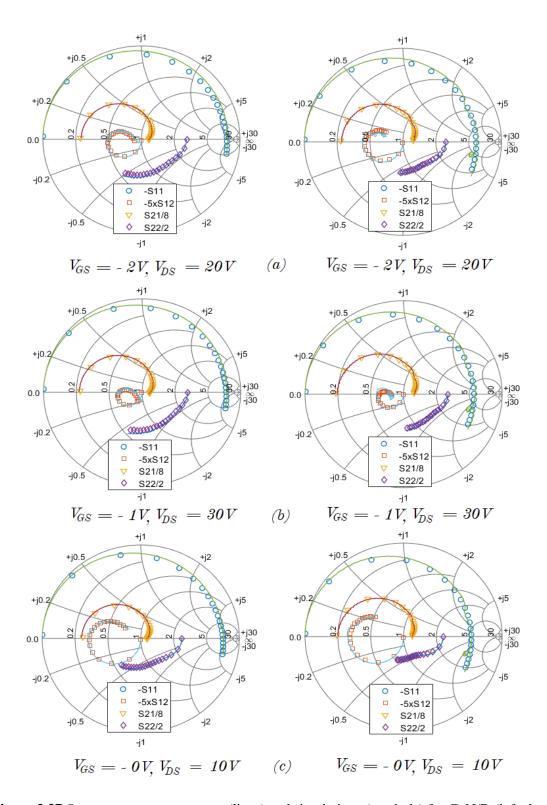

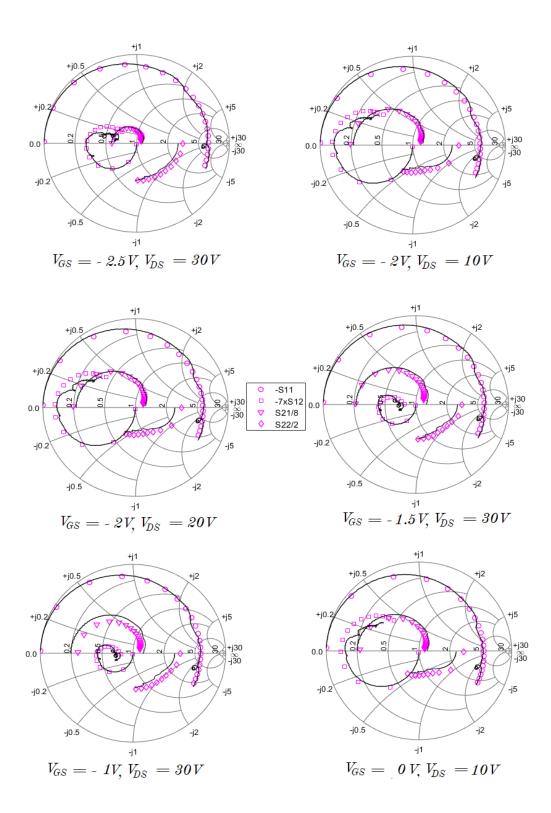

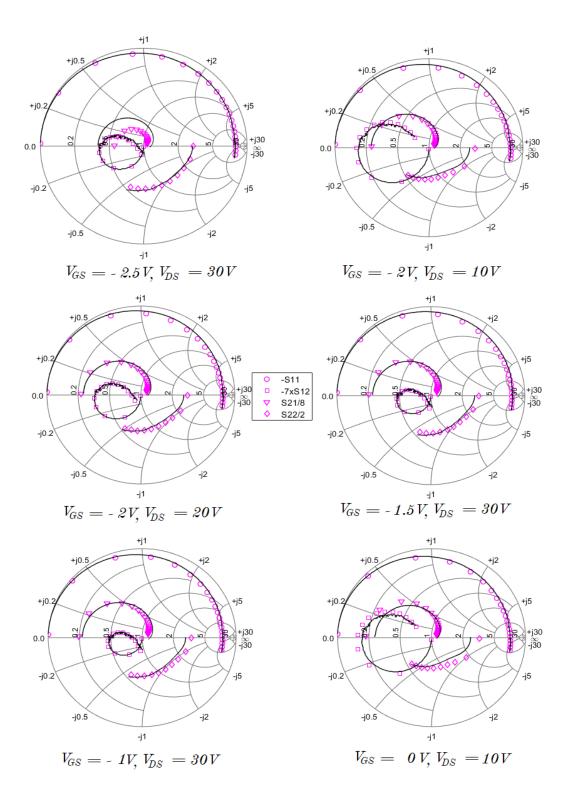

| 3.37 | S-parameter measurements (lines) and simulations (symbols) for GaN/D                                                                    |    |

|      | (left charts) and GaN/SiC (right chart) at frequencies ranging from 0.1 GHz                                                             |    |

|      | to 40 GHz at bias points of: (a) $V_{GS} = -2V$ and $V_{DS} = 20V$ , (b) $V_{GS} = -1V$                                                 |    |

|      | and $V_{DS} = 30$ V, and (c) $V_{GS} = -0$ V and $V_{DS} = 10$ V                                                                        | 89 |

| 3.38 | $C_{gp}$ and $C_{dp}$ scan for GaN/Si during phase 1                                                                                    | 90 |

| 3.39 | Inaccurate extraction due to the need of a substrate model for GaN/Si                                                                   | 90 |

| 3.40 | $C_{gp}$ and $C_{dp}$ scan for GaN/Si during phase 2                                                                                    | 91 |

| 3.41 | Plot for extracting the pad capacitances and the substrate parameters of                                                                |    |

|      | GaN/Si                                                                                                                                  | 91 |

| 3.42 | Extracted series inductances of GaN/Si                                                                         | 92  |

|------|----------------------------------------------------------------------------------------------------------------|-----|

| 3.43 | Extracted series resistances of GaN/Si.                                                                        | 92  |

| 3.44 | Convergence of GWO during the optimization of GaN/Si parameters                                                | 93  |

| 3.45 | Optimized S-parameters simulations (symbols) and measurements (lines)                                          |     |

|      | for GaN/Si at frequencies from 0.1 GHz to 40 GHz under cold pinch-off                                          |     |

|      | condition                                                                                                      | 93  |

| 3.46 | $C_{gp}$ and $C_{dp}$ scan for Graphene-Based FET                                                              | 95  |

| 3.47 | Pad capacitances and substrate parameters extraction for Graphene-Based                                        |     |

|      | FET                                                                                                            | 96  |

| 3.48 | Extrinsic series inductances extraction for Graphene-Based FET                                                 | 96  |

| 3.49 | Extrinsic series resistances extraction for Graphene-Based FET.                                                | 97  |

| 3.50 | Error convergence using GWO for optimizing the extracted parameters of                                         |     |

|      | Graphene-Based FET                                                                                             | 97  |

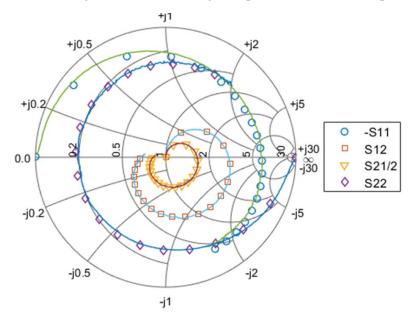

| 3.51 | Optimized S-parameters simulations (symbols) and measurements (lines)                                          |     |

|      | for the optimized values of Graphene-Based FET at frequencies from 0.1                                         |     |

|      | GHz to 40 GHz under cold pinch-off condition.                                                                  | 98  |

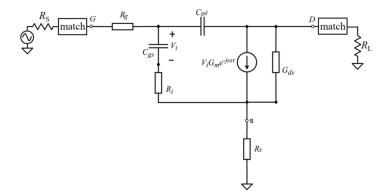

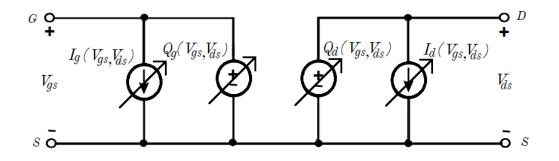

| 4.1  | Quasi-Static Large-Signal topology [2].                                                                        | 107 |

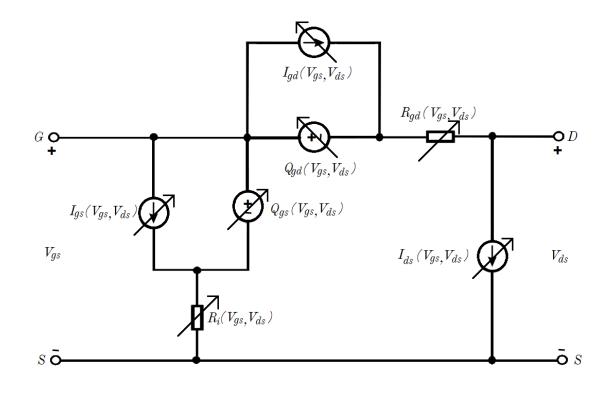

| 4.2  | Non Quasi-Static Large-Signal topology [4].                                                                    | 109 |

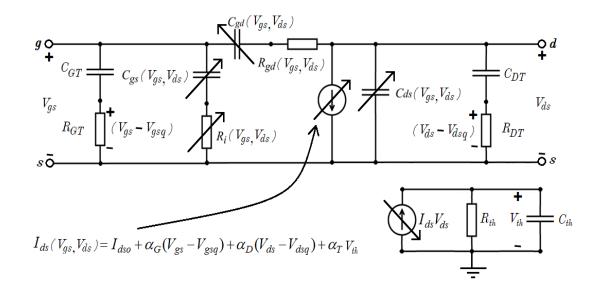

| 4.3  | Proposed large-signal model                                                                                    | 110 |

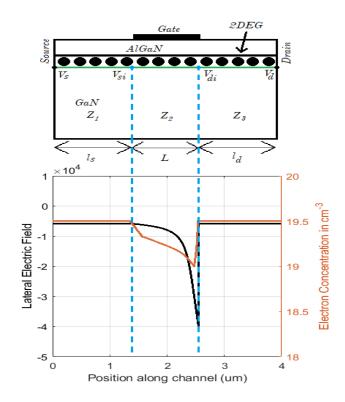

| 4.4  | Quasi-Physical Zone Division model illustration using zone-divided GaN                                         |     |

|      | HEMT structure and highlighting electron concentration and lateral electric                                    |     |

|      | field of a generic GaN HEMT device in each region [9][11].                                                     | 115 |

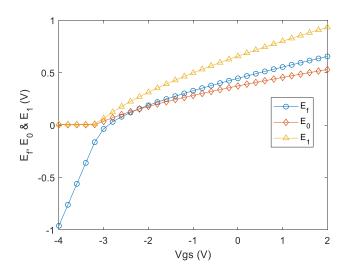

| 4.5  | Energy levels vs. $V_{gs}$ using numerical non-linear solver.                                                  | 117 |

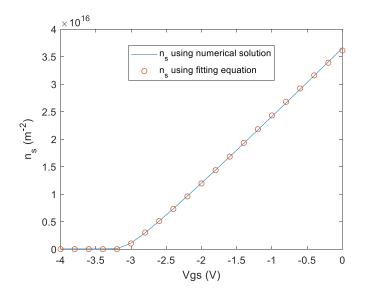

| 4.6  | $n_s$ vs. $V_{gs}$ using non-linear solver and using fitting equation (4.28)                                   | 118 |

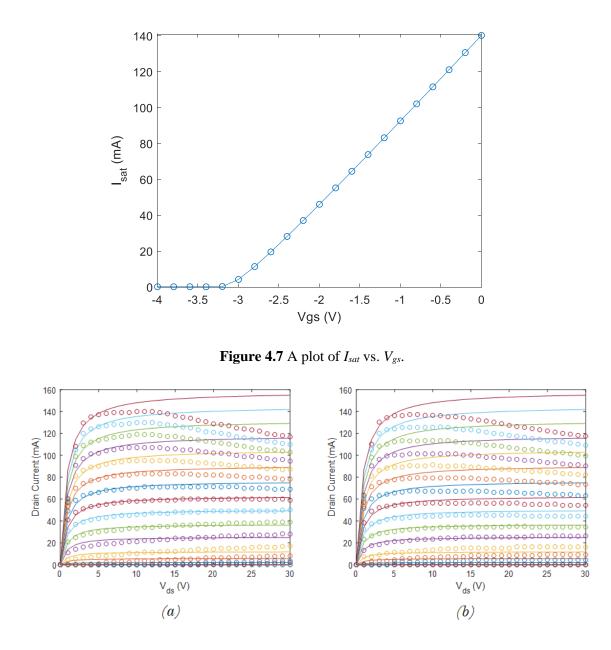

| 4.7  | A plot of <i>I</i> <sub>sat</sub> vs. <i>V</i> <sub>gs</sub> .                                                 | 119 |

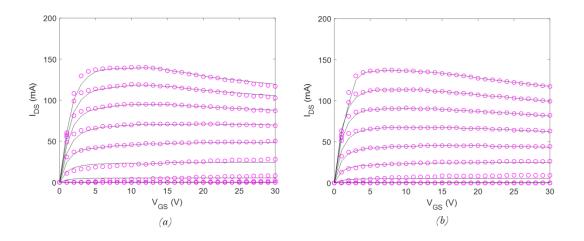

| 4.8  | Static DC IV measurements (circles) and isothermal trapping-free current                                       |     |

|      | simulations (lines) at $V_{gs} = -4$ to 0 V at a step of 0.2 V and $V_{ds} = 0$ to 30 V                        |     |

|      | at a step of 1V for (a) GaN/D and (b) GaN/SiC.                                                                 | 119 |

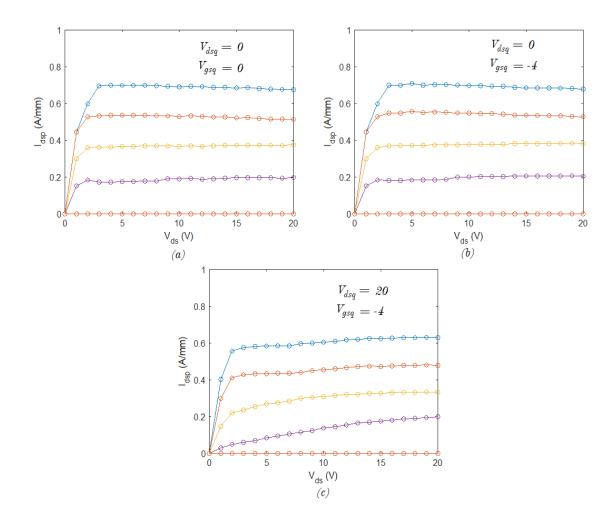

| 4.9  | Pulsed IV-measurements for 2x100 um GaN/D at quiescent bias points of                                          |     |

|      | (a) $V_{gsq} = 0V$ , $V_{dsq} = 0V$ (b) $V_{gsq} = -4V$ , $V_{dsq} = 0V$ and (c) $V_{gsq} = -4V$ , $V_{dsq} =$ |     |

|      | 20V [16]                                                                                                       | 123 |

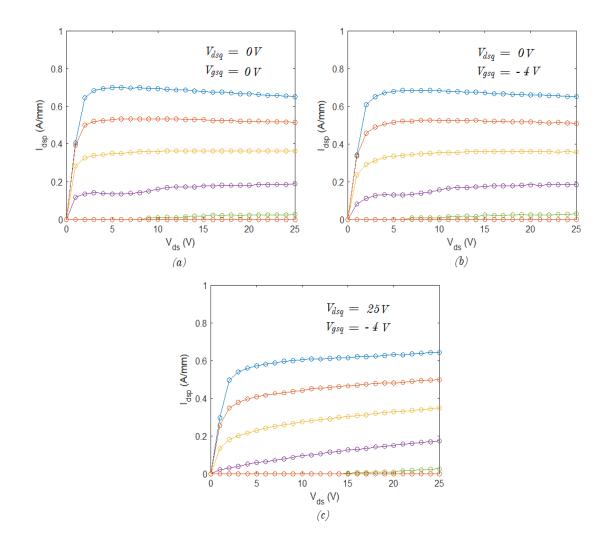

| 4.10 | Pulsed IV-measurements for 4x50 um GaN/SiC at quiescent bias points of                                         |

|------|----------------------------------------------------------------------------------------------------------------|

|      | (a) $V_{gsq} = 0$ V, $V_{dsq} = 0V$ (b) $V_{gsq} = -4$ V, $V_{dsq} = 0V$ and (c) $V_{gsq} = -4$ V, $V_{dsq} =$ |

|      | 25V [8]                                                                                                        |

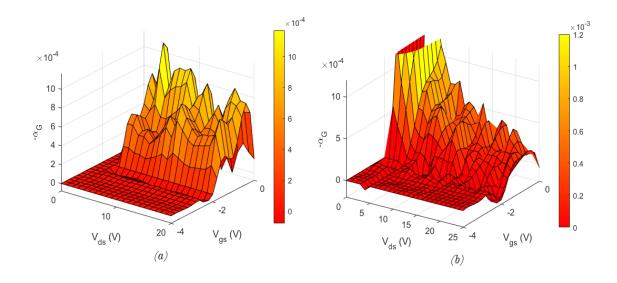

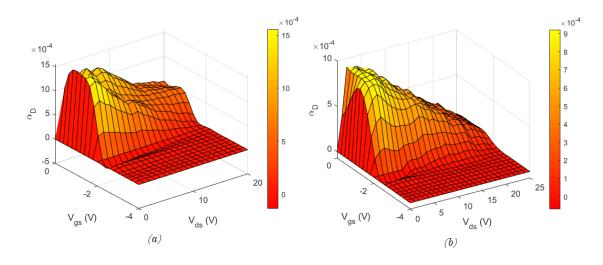

| 4.11 | $\alpha_G$ at different $V_{gs}$ and $V_{ds}$ for (a) GaN/D, (b) GaN/SiC                                       |

| 4.12 | $\alpha_D$ at different $V_{gs}$ and $V_{ds}$ for (a) GaN/D, (b) GaN/SiC126                                    |

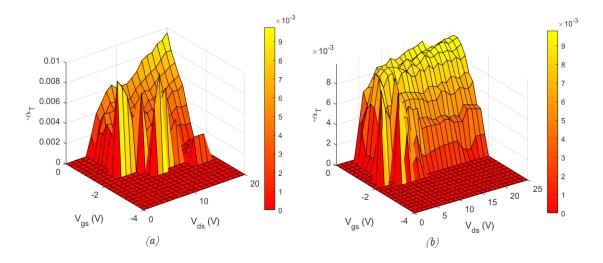

| 4.13 | $\alpha_T$ at different $V_{gs}$ and $V_{ds}$ for (a) GaN/D, (b) GaN/SiC126                                    |

| 4.14 | Large-signal model with self-heating and charge-trapping models included                                       |

|      | [2]128                                                                                                         |

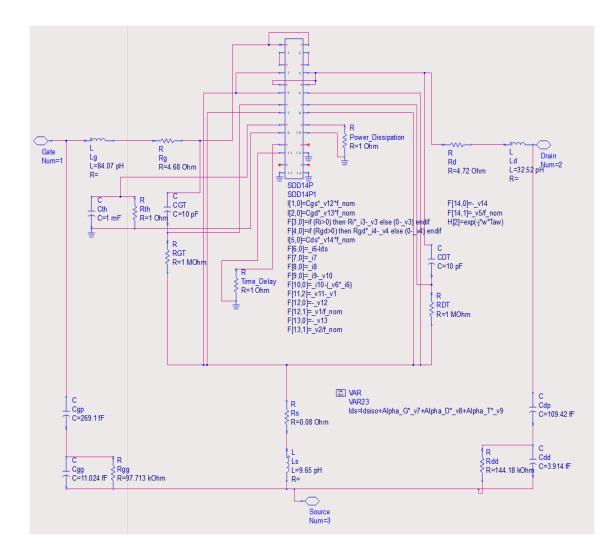

| 5.1  | Data Access Components (DAC)                                                                                   |

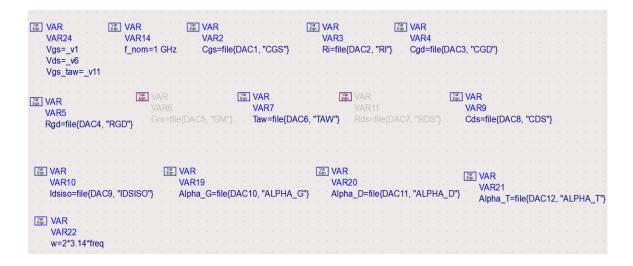

| 5.2  | Variables in ADS                                                                                               |

| 5.3  | Full model in ADS for the case of GaN/D                                                                        |

| 5.4  | S-parameters simulations (symbols) using the model in ADS and compared                                         |

|      | with measurements (lines) of GaN/D at different bias points at frequencies                                     |

|      | from 0.1 GHz to 40 GHz                                                                                         |

| 5.5  | S-parameters simulations (symbols) using the model in ADS and compared                                         |

|      | with measurements (lines) of GaN/SiC at different bias points at                                               |

|      | frequencies from 0.1 GHz to 40 GHz 139                                                                         |

| 5.6  | Static IV simulations (lines) using the model in ADS and compared with                                         |

|      | measurements (circles) for $V_{GS} = -4$ to 0V with a step of 0.4V, and $V_{DS} = 0$                           |

|      | to 30V using a step of 1V for (a) GaN/D and (b) GaN/SiC                                                        |

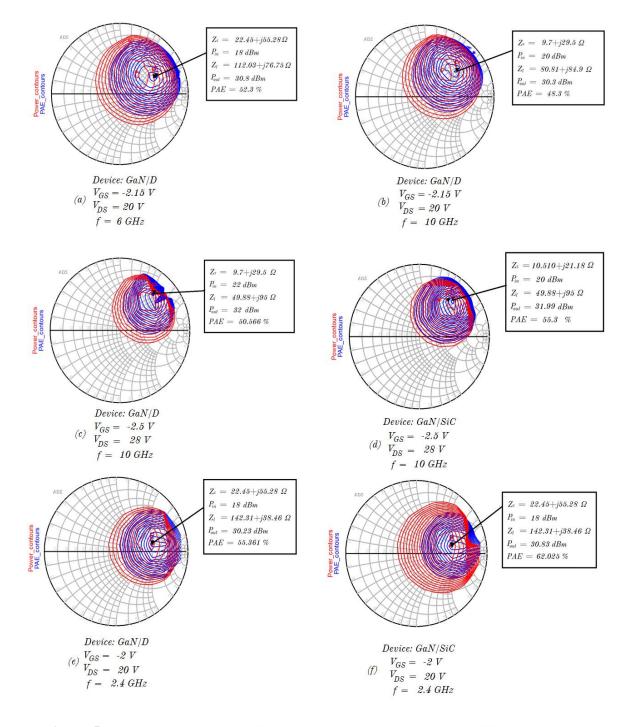

| 5.7  | Load-pull simulations for both GaN/D and GaN/SiC at different bias-points                                      |

|      | and frequencies                                                                                                |

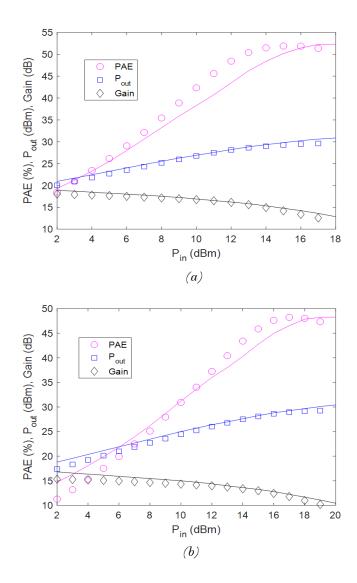

| 5.8  | Single-tone large-signal simulations (lines) and measurements (circles) for                                    |

|      | GaN/D at bias points of $V_{GS} = -2.15$ V and $V_{DS} = 20$ V at (a) 6 GHz and (b)                            |

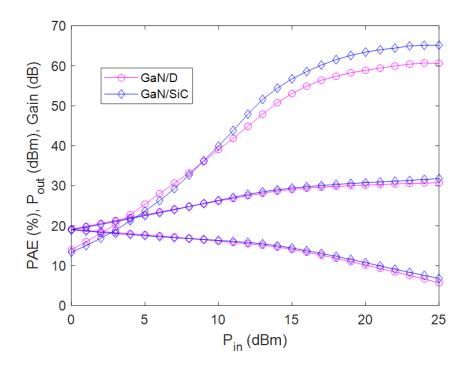

|      | 10 GHz                                                                                                         |

| 5.9  | Single-tone large-signal simulations for both GaN/D (Magenta) and                                              |

|      | GaN/SiC (Purple) at a fundamental frequency of 2.4 GHz and bias voltages                                       |

|      | of $V_{GS} = -2V$ and $V_{DS} = 20$                                                                            |

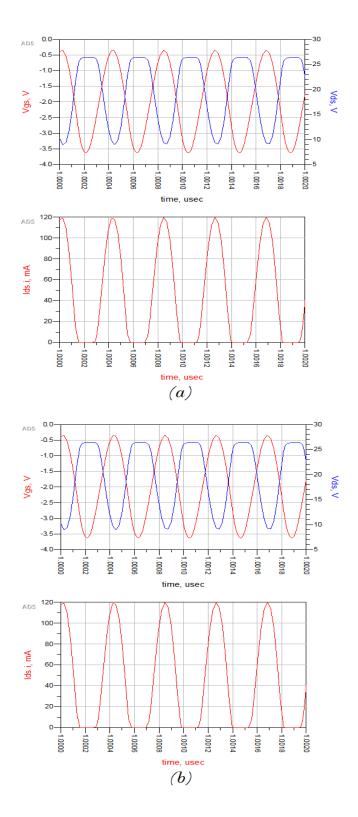

| 5.10 | Simulated large-signal waveforms for class AB at a frequency of 2.4 GHz                                        |

|      | with an input power of 12 dBm and bias voltages of $V_{GS} = -2V$ and $V_{DS} =$                               |

|      | 20V for (a) GaN/D and (b) GaN/SiC                                                                              |

|      |                                                                                                                |

## List of Tables

| 3.1 | Extracted parameters for GaN/D and GaN/SiC under cold pinch-off                | •   |  |

|-----|--------------------------------------------------------------------------------|-----|--|

|     | condition (*: "N/A" implies the component is ignored in phase 1, " $\infty$ "  |     |  |

|     | implies simplification of the model from that of Figure 3.10 to Figure 3.11    |     |  |

|     | and "-" implies result not recorded).                                          | 78  |  |

| 3.2 | Extracted extrinsic parameters of 2x200 um GaN/Si (*: "N/A" means              |     |  |

|     | elements not involved in phase 1 and "-" means data not available in the       |     |  |

|     | reference).                                                                    | 94  |  |

| 3.3 | Extracted extrinsic parameters of Graphene-Based FET (*: N/A means             |     |  |

|     | elements not present during phase 1, - means data was not given in             |     |  |

|     | literature, $\infty$ implies neglected components and hence the circuit can be |     |  |

|     | simplified from Figure 3.10 to 3.11)                                           | 99  |  |

| 4.1 | Parameters used to model the isothermal free-trapping current of               |     |  |

|     | 200um/200nm GaN HEMT [8][13][14].                                              | 120 |  |

| 5.1 | Comparison between load-pull simulations and measurements for both             |     |  |

|     | GaN/D and GaN/SiC at different frequencies and bias points.                    | 141 |  |

# List of Symbols

| $\Delta E_c(x)$                     | Conduction band offset at the AlGaN/GaN interface             |

|-------------------------------------|---------------------------------------------------------------|

| $\mu_0$                             | Low-field electron mobility                                   |

| $\mu_{e\!f\!f}$                     | Effective electron mobility                                   |

| $C_{dd}$                            | Parasitic conduction drain capacitance                        |

| $C_{ds}$                            | Intrinsic drain-to-source capacitance                         |

| $C_{dsi}$                           | Drain-to-source inter-electrode capacitance                   |

| $C_{e\!f\!f}$                       | Effective gate capacitance per unit area                      |

| $C_{gd}$                            | Intrinsic gate-to-drain capacitance                           |

| $C_{gd1}$                           | Gate-to-drain depletion region capacitance                    |

| $C_{gd2}$                           | Capacitance between the gate and the GaN cap from drain side  |

| $C_{gdf},\ C_{gdi}$                 | Gate-to-drain inter-electrode capacitance                     |

| $C_{gdp}$                           | Feedback pad capacitance                                      |

| $C_{gg}$                            | Parasitic conduction gate capacitance                         |

| $C_{gs}$                            | Intrinsic gate-to-source capacitance                          |

| C <sub>gs1</sub>                    | Gate-to-source depletion region capacitance                   |

| $C_{gs2}$                           | Capacitance between the gate and the GaN cap from source side |

| C <sub>gsf</sub> , C <sub>gsi</sub> | Gate-to-source inter-electrode capacitance                    |

| $C_m$                               | Miller capacitance                                            |

| $C_{pd}$                            | Drain pad capacitance                                         |

| $C_{pg}$                            | Gate pad capacitance                                          |

| $C_{th}$                            | Thermal capacitance                                           |

| D                                                                                                   | Effective density of quantum states                                                                                                                                                                                  |

|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| d                                                                                                   | Thickness of AlGaN layer                                                                                                                                                                                             |

| E                                                                                                   | Electric field                                                                                                                                                                                                       |

| $E_{I}$                                                                                             | Second lowest quantized energy in 2DEG                                                                                                                                                                               |

| $E_c$                                                                                               | Critical electric field                                                                                                                                                                                              |

| $E_{f}$                                                                                             | Position of the Fermi level                                                                                                                                                                                          |

| E <sub>NET</sub>                                                                                    | Induced electric field in AlGaN                                                                                                                                                                                      |

| $E_o$                                                                                               | Lowest quantized energy in 2DEG                                                                                                                                                                                      |

| fmax                                                                                                | Unity power-gain cutoff frequency                                                                                                                                                                                    |

| $f_t$                                                                                               | Unity current-gain cutoff frequency                                                                                                                                                                                  |

| $G_{ds}$ , $R_{ds}$                                                                                 | Drain-to-source channel length modulation conductance/ resistance                                                                                                                                                    |

|                                                                                                     |                                                                                                                                                                                                                      |

| $G_{gdf}$ , $R_{gdf}$                                                                               | Breakdown gate conduction / resistance                                                                                                                                                                               |

| $G_{gdf},\ R_{gdf}$                                                                                 | Breakdown gate conduction / resistance<br>Forward gate conduction / resistance                                                                                                                                       |

|                                                                                                     | -                                                                                                                                                                                                                    |

| $G_{gsf}, R_{gsf}$                                                                                  | Forward gate conduction / resistance                                                                                                                                                                                 |

| $G_{gsf}, R_{gsf}$<br>$G_m$                                                                         | Forward gate conduction / resistance<br>Channel transconductance                                                                                                                                                     |

| $G_{gsf}, R_{gsf}$<br>$G_m$<br>$G_{max}$                                                            | Forward gate conduction / resistance<br>Channel transconductance<br>The maximum power gain                                                                                                                           |

| $G_{gsf}, R_{gsf}$<br>$G_m$<br>$G_{max}$<br>$h_{21}$                                                | Forward gate conduction / resistance<br>Channel transconductance<br>The maximum power gain<br>short-circuit current gain                                                                                             |

| $G_{gsf}, R_{gsf}$<br>$G_m$<br>$G_{max}$<br>$h_{21}$<br>$I_d, I_{ds}$                               | Forward gate conduction / resistance<br>Channel transconductance<br>The maximum power gain<br>short-circuit current gain<br>Drain-to-source current                                                                  |

| $G_{gsf}, R_{gsf}$<br>$G_m$<br>$G_{max}$<br>$h_{21}$<br>$I_d, I_{ds}$<br>$I_{ds}^{DC}$              | Forward gate conduction / resistance<br>Channel transconductance<br>The maximum power gain<br>short-circuit current gain<br>Drain-to-source current<br>Measured DC current                                           |

| $G_{gsf}, R_{gsf}$<br>$G_m$<br>$G_{max}$<br>$h_{21}$<br>$I_d, I_{ds}$<br>$I_{ds}^{DC}$<br>$I_{dso}$ | Forward gate conduction / resistance<br>Channel transconductance<br>The maximum power gain<br>short-circuit current gain<br>Drain-to-source current<br>Measured DC current<br>Isothermal trapping-free drain current |

| Ig, Igs           | Gate current                                                          |

|-------------------|-----------------------------------------------------------------------|

| Isat              | Maximum current achievable                                            |

| L                 | Channel length                                                        |

| $l_d$             | Drain access length                                                   |

| ls                | Source access length                                                  |

| $N_d$             | Doping concentration of n-AlGaN layer                                 |

| ns                | Density of 2DEG                                                       |

| P <sub>in</sub>   | RF input power                                                        |

| Pout              | RF output power                                                       |

| P <sub>PE</sub>   | Piezoelectric Polarization                                            |

| P <sub>SP</sub>   | Spontaneous Polarization                                              |

| q                 | Electronic charge                                                     |

| $Q_d$             | Quasi-static drain charge                                             |

| $Q_{\mathcal{S}}$ | Quasi-static gate charge                                              |

| $Q_{gd}$          | Non Quasi-static gate-to-drain charge                                 |

| $Q_{gs}$          | Non Quasi-static gate-to-source charge                                |

| $R_d$             | Drain electrode resistance                                            |

| $R_{dd}$          | Parasitic conduction drain resistance                                 |

| $R_{dp}$          | Shunt pad resistance at the drain side                                |

| $R_{DT}, C_{DT}$  | Model for low frequency transition and trapping-effects at drain side |

| $R_g$             | Gate metal resistance                                                 |

| $R_{gd}$          | Depletion charging/discharging resistance from drain side             |

| $R_{gg}$                            | Parasitic conduction gate resistance                                 |

|-------------------------------------|----------------------------------------------------------------------|

| $R_{gp}$                            | Shunt pad resistance at the gate side                                |

| $R_{GT}, C_{GT}$                    | Model for low frequency transition and trapping-effects at gate side |

| $R_i$                               | Depletion charging/discharging resistance at source side             |

| $R_s$                               | Source electrode resistance                                          |

| <b>R</b> <sub>th</sub>              | Thermal Resistance                                                   |

| S                                   | Small-signal scattering parameter                                    |

| V                                   | Electron velocity                                                    |

| $V_{br}$                            | Breakdown voltage                                                    |

| V <sub>di</sub>                     | Intrinsic drain voltage in zone division model                       |

| V <sub>DS</sub> , V <sub>ds</sub>   | Drain-to-source voltage                                              |

| V <sub>DSQ</sub> , V <sub>dsq</sub> | Drain-to-source quiescent bias                                       |

| V <sub>dsqf</sub>                   | Drain-to-source final quiescent bias point                           |

| $V_{dsqi}$                          | Drain-to-source initial quiescent bias point                         |

| $V_{e\!f\!f}$                       | Effective gate-to-source voltage                                     |

| V <sub>GS</sub> , V <sub>gs</sub>   | Gate-to-source voltage                                               |

| $V_{GSQ}, V_{gsq}$                  | Gate-to-source quiescent bias                                        |

| $V_{gsqf}$                          | Gate-to-source final quiescent bias point                            |

| $V_{gsqi}$                          | Gate-to-source initial quiescent bias point                          |

| $V_k$                               | Knee voltage                                                         |

| $V_p$                               | Pinch-off voltage                                                    |

| Vsat                                | Electron Saturation Velocity                                         |

| $V_{si}$        | Intrinsic source voltage in zone division model                  |

|-----------------|------------------------------------------------------------------|

| $v_t$           | Thermal voltage at room temperature                              |

| $V_{TH}$        | Self-heating voltage                                             |

| W               | Width of the channel                                             |

| X               | Wolf's position vector                                           |

| $X_p$           | Prey's position vector                                           |

| Y               | Small-signal admittance parameter                                |

| Y <sub>dd</sub> | Admittance of the substrate network from drain side              |

| Y <sub>ds</sub> | Intrinsic drain-to-source admittance                             |

| $Y_{gd}$        | Intrinsic gate-to-drain admittance                               |

| $Y_{gg}$        | Admittance of the substrate network from gate side               |

| $Y_{gm}$        | Admittance of the intrinsic transconductance                     |

| Y <sub>gs</sub> | Intrinsic gate-to-source admittance                              |

| $Y_i$           | Intrinsic Y-parameters                                           |

| Ζ               | Small-signal impedance parameter                                 |

| $Z_1$           | Source Neutral Zone                                              |

| $Z_2$           | Intrinsic FET Zone                                               |

| $Z_3$           | Drain Neutral Zone                                               |

| Zo              | Reference Impedance (50 $\Omega$ )                               |

| α               | Ratio of gate-to-source capacitance to gate-to-drain capacitance |

| α <sub>D</sub>  | Fitting parameter for buffer-trapping effect                     |

| $lpha_G$        | Fitting parameter for surface-trapping effect                    |

| $\alpha_T$   | Fitting parameter for self-heating effect                         |

|--------------|-------------------------------------------------------------------|

| $lpha_w$     | Leader of the wolf pack                                           |

| β            | Ratio of drain-to-source capacitance to gate-to-drain capacitance |

| $eta_w$      | Second best wolf                                                  |

| γο           | Experimentally-measured value for $E_0$                           |

| γ1           | Experimentally-measured value for $E_1$                           |

| δ            | Velocity saturation factor                                        |

| $\delta_w$   | Third best wolf                                                   |

| Е            | Percentage Error                                                  |

| EAlGaN       | Permittivity of the AlGaN layer                                   |

| $\Theta_1$   | First-order fitting parameter for the effective mobility          |

| $\Theta_2$   | Second-order fitting parameter for the effective mobility         |

| λ            | Channel length modulation parameter                               |

| $\sigma(x)$  | Polarization charge density                                       |

| τ            | Electron transit time                                             |

| $	au_{DT}$   | Buffer-traps time constant                                        |

| $\tau_{GT}$  | Surface-traps time constant                                       |

| $	au_{th}$   | Self-heat time constant                                           |

| $\phi_B(x)$  | Schottky Barrier Height                                           |

| ω            | Frequency in rad/s                                                |

| $\omega_w$   | Other wolves                                                      |

| $arPsi_{sd}$ | Surface potential at the drain side                               |

| $\Phi_{sm}$ Average | e surface potential |

|---------------------|---------------------|

|---------------------|---------------------|

$\Phi_{ss}$  Surface potential at the source side

# List of Abbreviations

| 2DEG    | Two-Dimensional Electron Gas           |

|---------|----------------------------------------|

| ADS     | Advanced Design System                 |

| CAD     | Computer-Aided Design                  |

| CVD     | Chemical Vapor Deposition              |

| CW      | Continuous-wave                        |

| DAC     | Data Access Component                  |

| DC      | Direct Current                         |

| DUT     | Device-Under-Test                      |

| EC-LSM  | Equivalent Circuit- Large-signal Model |

| ECM     | Equivalent Circuit Model               |

| EC-SSM  | Equivalent Circuit- Small-signal Model |

| FET     | Field-Effect Transistor                |

| GaAs    | Gallium Arsenide                       |

| GaN     | Gallium Nitride                        |

| GaN/D   | GaN on Diamond substrate               |

| GaN/Si  | GaN on Silicon substrate               |

| GaN/SiC | GaN on Silicon Carbide substrate       |

| GWO     | Grey Wolf Optimizer                    |

| HEMT    | High Electron Mobility Transistor      |

| IMD     | Intermodulation-Distortion             |

| LNA     | Low Noise Amplifier                    |

| MESFET | Metal–Semiconductor Field-Effect Transistor       |

|--------|---------------------------------------------------|

| MODFET | Modulation-Doped Field-Effect Transistor          |

| MOSFET | Metal–Oxide–Semiconductor Field-Effect Transistor |

| PA     | Power Amplifier                                   |

| PAE    | Power Added Efficiency                            |

| QPZD   | Quasi-Physical Zone Division                      |

| RF     | Radio Frequency                                   |

| SDD    | Symbolic Defined Device                           |

| SiN    | Silicon Mononitride                               |

| SP     | Surface Potential                                 |

| UHF    | Ultra High Frequency                              |

| VNA    | Vector Network Analyzer                           |

#### Chapter 1: Introduction

#### 1.1 Motivations

Gallium Nitride (GaN) High Electron Mobility Transistors (HEMTs) are very attractive devices for high-frequency high-power applications, such as in satellite and 5G communication systems [1]-[7]. In fact, GaN HEMTs are commonly used nowadays for the design of high-efficiency power amplifiers, mainly because of their large bandgap energy (resulting in high breakdown voltages), and high saturation velocity, due to the separation of the dopant atoms from the free charge carriers and polarization effects (which mitigate the effect of the impurity scattering effects) [8]. Consequently, GaN devices exhibit a large output power and high Power Added Efficiency (PAE). However, the high power density of GaN HEMTs results in an increase in their operating temperature, which deteriorates their PAE during normal and overloaded functioning conditions [9]. This issue has led to a reduction in device lifetime as well as negative current drift due to both the nucleation layer used in-between the GaN buffer and the substrate (to reduce lattice mismatch between them) and the thermal resistance associated with the substrate (this latter must be as low as possible to efficiently dissipate the heat through the substrate) [9]. There should be tradeoffs to have both reduced temperature resistance and acceptable lattice matching between the substrate and the GaN buffer [10]. Therefore, in order to reach the full potential and capabilities of the GaN HEMT, one should retain a substrate that has both low thermal resistance to reduce self-heating effects and high electrical resistance to reduce leakage current. Furthermore, it should adhere to the GaN buffer by using a suitable material that provides a very little lattice mismatch with the substrate in order to reduce charge-trapping effects.

To address this issue, several substrate materials have been utilized for GaN HEMTs, from which Silicon Carbide (SiC) and Silicon (Si) substrates are the most commonly used [11]. The GaN HEMT on SiC-substrate (GaN/SiC) is the state-of-the-art GaN HEMT. SiC exhibits moderate thermal conductivity with high electrical resistivity [9]. On the other side, the Si substrate of GaN on Si-substrate (GaN/Si) has a thermal conductivity that is about three times lower than GaN/SiC and high electrical resistivity (comparable to GaN/SiC) [9]. Due to the lower thermal resistivity of the GaN/SiC

compared to GaN/Si, it will have a lower self-heating effect associated with it, which will reduce the current dispersion and hence improve the PAE. This feature shows the primary reason behind the choice of GaN/SiC as a state-of-the-art device.

In 2006, the GaN HEMT on a diamond substrate (GaN/D) was demonstrated in [12]. Diamond has a thermal conductivity that is two- to four-times the thermal conductivity of SiC. Therefore, the GaN/D can have a 40% reduction in channel temperature, leading to a spacing between the gate fingers three-times smaller compared to GaN/SiC, without worrying about thermal crosstalk. This implies, in theory, an expected output power three-times larger than that of GaN/SiC while maintaining thermal reliability [9]. Also, diamond has an electrical resistivity of about 10 orders of magnitude larger than SiC. Furthermore, its high substrate resistivity, with the potential of having good matching between the GaN buffer and diamond substrate, could lead to a tremendous improvement in PAE by reduced self-heating effects and leakage current induced by charge trapping effects [9]. It is clear that GaN/D holds valuable promises to the future of high-frequency high-power amplifier design due to its increased reliability of thermal management properties.

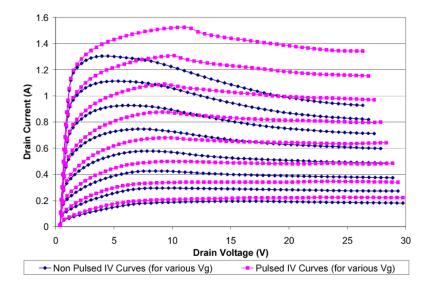

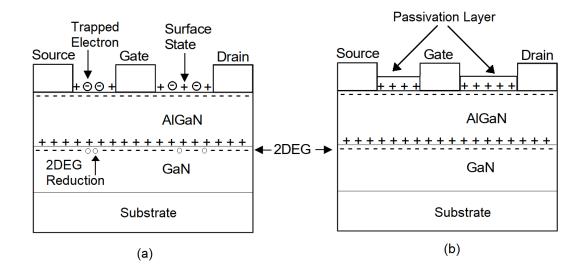

All of the above electrical characteristics, charge-trapping and self-heating effects, should be modeled to efficiently capture their impact and learn how to mitigate them. The electrical Equivalent Circuit Model (ECM) has been retained for the reason of good compromise between the physical model and the behavioral model [13]. It can also be relatively easy to integrate it in Computer-Aided Design (CAD) tools. The current dispersion due to buffer-charge-trapping, surface-charge-trapping, and self-heating effects can be modeled using the Equivalent Circuit-Large-signal Model (EC-LSM) [14]. Furthermore, pulsed IV measurements can allow us with the help of the EC-LSM to separate the three effects on current dispersion, allowing for more extensive studies on each distinctive effect, in order to reduce its impact. However, to develop an accurate EC-LSM, an accurate multi-biased Equivalent Circuit-Small-signal Model (EC-SSM) is required [14]. The EC-SSM can also describe the substrate electrical resistivity and the parasitic conduction through the substrate, which induces leakage current caused by buffer-trapping effects [15].

However, based on the technical literature, switching between different substrates implies considering different circuit models, thus, different extraction techniques for each circuit model. This approach increases complexity and obstructs the automation capabilities of the extractor. In addition to that, existing extraction techniques do not take into account both the asymmetrical GaN HEMT structure and the parasitic conduction through the substrate together, which does not work for asymmetrical devices that exhibit parasitic conduction through the substrate. A need for a single small-signal model that uses a single extraction technique for all types of GaN HEMTs should be studied regardless of the type of substrate used; it should also take into account the asymmetrical GaN HEMT structure and parasitic conduction effects in the extraction technique.

#### 1.2 Literature Review

During the last three decades, numerous works have been proposed on developing various models and extraction techniques for the GaN HEMT that describe various physical and electrical characteristics. A large-signal modeling approach was applied to GaN/Si for RF high-power applications as presented in [15]. This model takes into account parasitic conduction through the substrate at lower frequencies as well as chargetrapping effects and self-heating effects associated with high-power applications. The obtained values were optimized using a hybrid optimization method that combines genetic and simplex optimization techniques. In 2004, a temperature-dependent model for continuous-wave (CW) and pulsed-mode operation was applied to GaN/SiC [16]. This model used pulsed measurements at various biases and temperatures to describe thermal and frequency dispersion using small- and large-signal GaN HEMT models. In [17], a general-purpose large-signal model for GaN and SiC MESFET devices was developed and evaluated using DC, S-parameters, and large-signal measurements. This model takes into account harmonics, which would describe physical dispersion and time delay of electrons to cross the channel. A table-based large-signal model for GaN HEMT on SiC substrate that takes into account charge-trapping and self-heating effects was developed in 2007 [18]. This model uses the B-spline-approximation technique for model-element construction that improves intermodulation-distortion (IMD) simulation. The intrinsic gate capacitances and conductances of the small-signal model were integrated in order to

develop the gate charge and current source of the large-signal model. Pulsed I-V measurements were used to characterize the current dispersion due to self-heating effects and charge-trapping effects under constant temperature. It was also found that using the *B*-spline approximation improves the I-V simulations. In [19], an empirical approach was used to deal with nonlinearly dynamic thermal effects. The model was most suitable for non-constant-envelope RF applications such as in pulsed radar. It uses Volterra's nonlinear system modeling theory; however, the series was modified in order to simplify the model. All of the above-mentioned papers depend on static I-V measurements, pulsed I-V measurements, and/or *S*-parameters measurements in order to develop both the EC-SSM and EC-LSM; they have also used different models depending on the type of substrate used for the GaN HEMT.

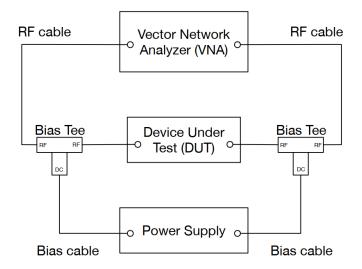

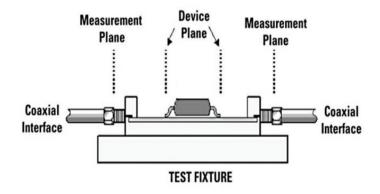

As for the parameter extraction of the extrinsic part of the EC-SSM, the existing extraction techniques differ in terms of complexity, accuracy, and type of topology implemented in the extrinsic part. In 1988, a paper addressing small-signal modeling for MOSFETs was presented [20]. The paper describes a direct extraction of the extrinsic and intrinsic parts of the small-signal model using a few simple matrix manipulations. It was verified that the model's S-parameters fit well up to 26.5 GHz. In [21], dedicated onwafer test-structures were used to model the RF behavior of the Device-Under-Test (DUT). It proposes an improved three-step de-embedding to subtract the influence of parasitics and accurately model the RF behavior of the DUT. The paper in [22] showed that extremely high gate voltages have to be applied to correctly determine the series resistances of the extrinsic part of GaN HEMT's EC-SSM. The authors in [20] and [22] used cold pinch-off and forward S-parameters measurements at high gate voltage, while in [21], test structures were used to extract the extrinsic parameters. In 2006, a model parameter-extraction procedure for GaN HEMT was introduced showing that high gate voltage is not necessary to extract the parasitic inductances and resistances [23]. An efficient and accurate extraction algorithm for GaN HEMT was introduced in [24]; it uses only cold devices to extract all the extrinsic parameters without the need for forward Sparameter measurements. This model takes into account the time-delay in the output conductance as well. The work in [25] built a model that has 12 extrinsic components and developed an extraction technique that uses only cold pinch-off S-parameters

measurements. This model is applicable for large GaN HEMT devices with a 3.2 mm gate periphery. It shows high accuracy with measurements without the need for forward S-parameters measurements. The techniques described in [23]-[25] used pinch-off Sparameter measurements to extract the extrinsic inductances and resistances without relying on the forward S-parameters measurements. Although GaN HEMT circuit modeling is usually derived from linear conventional S-parameters; nonlinear scattering parameters, or "X-parameters" can also be used to model the HEMTs [26]. X-parameters are a superset of "small-signal" S-parameters and "large-signal" S-parameters. The main reason for using the X-parameters for modeling GaN HEMT devices is their ability to include the device behaviour at harmonics of the fundamental frequency at specific bias points. This leads to combining both the parameter extraction process and nonlinear modeling by incorporating the nonlinear X-parameter measurements. However, it was stated that X-parameters lead to improvements in the extracted parameters only via incorporating an artificial neural network, leading to additional complexity in the extraction procedure [26]. In addition to that, X-parameters do not describe the circuit structure of GaN HEMT, which leads to different conversion rules and equations to convert them to S-parameters, hence adding additional complexity [26]. X-parameters have great promising for the future of GaN modeling, but these behavioral-based measurements still impose difficulties in the field of GaN modeling.

A performance comparison between GaN/D and GaN/SiC was presented in [27]. The GaN/D and GaN/SiC were modeled using an EC-LSM in order to compare the extrinsic and the intrinsic parameters of both devices. However, no study was performed to evaluate the charge-trapping effects of both devices. The work in [28] used an EC-SSM that takes into account ambient temperature changes on the extrinsic and intrinsic parts of the EC-SSM for both GaN/D and GaN/SiC. Self-heating effects were investigated in [29] between the GaN/D and GaN/Si by performing a direct comparison between static DC and pulsed I-V measurements. It showed that self-heating effects are direr in GaN/Si compared to GaN/D due to the excellent thermal conductivity of the diamond substrate. No charge-trapping effects were studied in this reference. Most works in GaN/D are still in their early phases, thus requiring more extensive studies in order to improve the development and application of the GaN/D HEMT technology [28].

The above literature review is certainly not comprehensive since that there has been a great deal of work in the field of GaN HEMTs modeling; however, it provides the necessary information for the work presented in this thesis.

#### 1.3 Objectives

As mentioned above, analyzing GaN HEMTs with different substrates will imply considering different topologies for the extrinsic network of the EC-SSM. This, in turn, will require multiple extraction techniques thus, increasing complexity. The first objective of this research work is to develop a single extraction technique for the extrinsic part of the EC-SSM of GaN HEMTs, assuming a unique EC-SSM, regardless of the substrate type. This model should be also applicable to different types of small-scaled high mobility devices. This technique would simplify the automation of the extractor and allows such an extraction technique to be applied for different devices with different substrate characteristics.

In [30], it was shown that due to asymmetrical device-structure, a passivation layer, and buffer-trapping effects, there will be an electric field rearrangement that will cause asymmetry between the gate-source side and gate-drain side as appose to typical MOSFET structures. This asymmetry should be considered in our extraction technique. To the best of the authors' knowledge, there is no existing extraction technique that takes into account both the asymmetrical GaN HEMT structure and the parasitic conduction through the substrate together. The proposed extraction technique takes into account, for the first time, both the asymmetrical GaN HEMT structure and the parasitic conduction effect. The extraction technique and its corresponding EC-SSM should be validated by using other devices such as Graphene-based FETs and as well as devices with different characteristics than GaN/D and GaN/SiC, such as the GaN/Si, which has parasitic conduction through the substrate at lower frequencies due to buffer-trapping effects.

The extracted parameters of the intrinsic and extrinsic parts will then undergo a new optimization technique for fine-tuning their values. The optimization technique is known as Grey Wolf Optimizer, which was shown that has high accuracy and high chances of avoiding local minima if the scanning range is small enough, which is quite suitable with our extraction technique [31-33]. The next objective would be to implement the EC-LSM that takes into account the nonlinear characteristics of the GaN HEMT's drain-to-source current. The EC-LSM, with the addition of pulsed IV measurements, will allow us to separate the self-heating and charge-trapping effects that are superimposed on the I-V measurements. This step would, therefore, allow for a direct comparison of the performance of the GaN/D vs. the state-of-the-art GaN/SiC device, based on the separated effects. The EC-LSM will be implemented in the Advanced Design System (ADS) for validation purposes and used to simulate multiple class-AB power amplifiers (operating at different frequency ranges) to test bench our model and compare the results with the technical literature.

The objectives of this work may be summarized as follows:

- Develop an extraction technique that simplifies the automation of extracting the extrinsic part of GaN HEMT, even on different substrates.

- Take into account the asymmetry between the gate-source and gate-drain electric field distribution due to asymmetrical device-structure, passivation layer deposition, and buffer charge-traps. It should also take into account parasitic conduction through the substrate.

- Optimizing the extracted extrinsic and intrinsic parameter using Grey Wolf Optimizer, this tool is suitable for this type of problem due to its high accuracy and local minima avoidance enabled by the extraction technique.

- Extraction technique validation by applying it to GaN/Si, GaN/SiC and GaN/D, and by applying it on Graphene-based FETs.

- Develop the EC-LSM for both GaN/D and GaN/SiC and using the pulsed I-V measurements in order to model the self-heating and charge-trapping effects on current dispersion individually for each effect.

- Implement the model using ADS for both GaN/SiC and GaN/D.

- Test bench the models in ADS by applying the model into multiple class AB power amplifiers targeted for applications operating at the X band and/or UHF frequency range.

### 1.4 Original contributions

Original contributions can be highlighted from this work as:

- Proposing, for the first time, a single extraction technique for the extrinsic network, which uses a single EC-SSM that works accurately for major types of substrates of GaN HEMTs. This extraction technique takes into account both the asymmetrical GaN HEMT structure and the parasitic conduction through the substrate, which is a first in the field of GaN HEMT modeling.

- Also, for the first time, to the best of the authors' knowledge, comparing, individual effects of self-heating, surface-trapping, and buffer-trapping effects on current dispersion between GaN/D and GaN/SiC-based devices using empirical fitting parameters extracted from pulsed IV measurements.

### 1.5 Outline

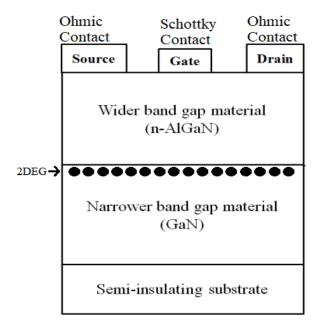

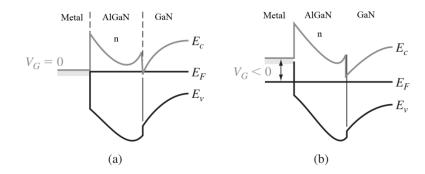

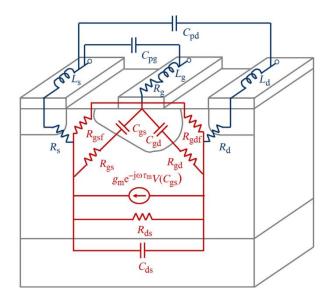

Chapter 2 will be discussing the theoretical background of GaN HEMT necessary for modeling its behavior. We will be detailing the reasons behind choosing GaN HEMT as a candidate for high-power high-frequency circuit design, and its basic structures and physics. 2-DEG and polarization effects will be shown. Non-ideal effects that are of major concern when performing device modeling will be detailed. These non-ideal effects can be related to current dispersion due to self-heating effects and charge trapping effects, parasitics within the device, and the substrate choice. Measurement data necessary for this work will be discussed showing how each type of measurement is considered and how can they be utilized for building various circuit models. Finally, modeling approaches will be discussed showing how the equivalent circuit model compromises both the physical-based and the behavioral-based model.

Chapter 3 is mainly divided into two parts. The first is related to the theory and different small-signal modeling approaches of GaN HEMT. The second is related to our work and contributions to the field of small-signal modeling. In this chapter, we will be showing the major parasitics found in the small-signal model of GaN HEMTs. Different structures for the extrinsic part of GaN HEMT will be studied since they differ in terms of extraction techniques and the amount of parasitics they consider. RF performance

metrics such as the transit frequency will be derived. Types of extraction approaches will be provided. The proposed EC-SSM and extraction technique will be presented in-depth detailing the steps taken to extract the extrinsic parameters of GaN HEMT and the advantages behind the proposed extraction technique. The extraction technique is then applied to *S*-parameters measurements obtained from the technical literature, specifically 2x100 um GaN/D [27], 4x50 um GaN/SiC [34], 2x200 um GaN/Si [35] as well as Graphene-based FET [36]. The extracted data will be discussed and validated for these devices.

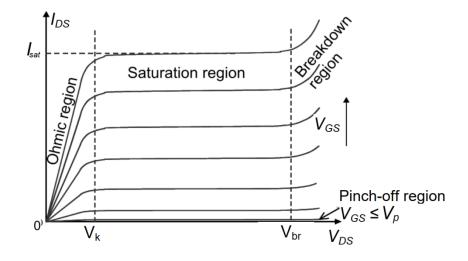

In Chapter 4, we will be modeling the non-linear drain-to-source current with its dispersive effects caused by charge-trapping and self-heating phenomena. First, we will be looking at different topologies used for large-signal modeling, two of which representing the intrinsic capacitances as charge components, while the third topology will represent the intrinsic capacitances as current components. Then, we will be considering the techniques used to build the isothermal trapping-free current [18][37-38]; this latter can be developed using empirical methods such as extracting the isothermal trapping-free current from pulsed IV measurements, or by using quasi-physical models such as the Surface Potential model [37] or Quasi-Physical Zone Division model [38]. We will be retaining the Quasi-Physical Zone Division model in our research work due to its simplicity, high accuracy, and lower number of fitting parameters compared to the Surface Potential model. The position of the Fermi level and the density of the 2-DEG will be numerically solved and fitted into a simplified expression, then the isothermal trapping-free current will be derived taking into consideration mobility degradation and velocity saturation. Finally, pulsed-IV measurements will be used for both GaN/D and GaN/SiC to develop the overall model that takes into account charge-trapping and selfheating effects, we will be comparing the fitting parameters extracted from the pulsed IV measurements between GaN/D and GaN/SiC and compare our insights with the observations from the literature.

Chapter 5 will be related to model validation by implementing the overall model in the Keysight Technologies Advanced Design System commercial software [30]. We will be showing how to implement the model using a Symbolically Defined Device and how to read the intrinsic components with the help of Data Access Components and Variables. We will first simulate the *S*-parameters under small signal input and large-signal DC bias to verify their accuracy with measurements. Next, we will be comparing the static DC IV characteristics between simulations and measurements for both GaN/D and GaN/SiC. Load-pull and single-tone simulations for class AB operation will be provided and compared with measurements.

Chapter 6 will summarise the work while giving research directions to future work.

## References

- K. Yuk, G. Branner and C. Cui, "Future directions for GaN in 5G and satellite communications," 2017 IEEE 60th Int. Midwest Symp. on Circuits and Syst. (MWSCAS), Boston, MA, 2017, pp. 803-806.

- [2] Y. Pei, "GaN Technology for 5G Application," 2019 Int. Conf. on IC Design and Technol. (ICICDT), SUZHOU, China, 2019, pp. 1-4.

- [3] K. Kunihiro, S. Hori and T. Kaneko, "High Efficiency Power Amplifiers for Mobile Base Stations: Recent Trends and Future Prospects for 5G", *IEICE Trans. on Fundam. of Electronics, Commun. and Comput. Sciences*, vol. 101, no. 2, pp. 374-384, 2018.

- [4] T. Do *et al.*, "7–13 GHz MMIC GaN HEMT Voltage-Controlled-Oscillators (VCOs) for satellite applications," 2017 12th Eur. Microw. Integr. Circuits Conf. (EuMIC), Nuremberg, 2017, pp. 220-223.

- [5] J. Wang, H. Yu and F. Yang, "Design of GaN HEMT Class-E Power Amplifier for Satellite Communication," 2018 Int. Conf. on Microw. and Millimeter Wave Technol. (ICMMT), Chengdu, 2018, pp. 1-3.

- [6] D. Maassen *et al.*, "A 12-W GaN-HEMT power amplifier for Ku-band satellite communication," 2016 21st Int. Conf. on Microw., Radar and Wireless Commun. (MIKON), Krakow, 2016, pp. 1-4.

- [7] K. Inoue, N. Ui and S. Sano, "High power and high efficiency GaN-HEMT for microwave communication applications," 2011 IEEE MTT-S Int. Microw. Workshop Ser. on Innovative Wireless Power Transmiss.: Technol., Syst., and Appl., Uji, Kyoto, 2011, pp. 267-270.

- [8] D. Neamen, *Semiconductor physics and devices*. New York: McGraw-Hill Higher Educ., 2012.

- [9] F. Ejeckam *et al.*, "GaN-on-diamond: The next GaN", *Microw. J.*, vol. 57, no. 5, pp. 124-136, 2014.

- G. Riedel *et al.*, "Reducing Thermal Resistance of AlGaN/GaN Electronic Devices Using Novel Nucleation Layers," in *IEEE Electron Device Lett.*, vol. 30, no. 2, pp. 103-106, Feb. 2009.

- [11] H. Amano *et al.*, "The 2018 GaN power electronics roadmap", *J. of Phys. D: Appl. Phys.*, vol. 51, no. 16, p. 163001, 2018.

- [12] G. Jessen *et al.*, "AlGaN/GaN HEMT on Diamond Technology Demonstration," 2006 IEEE Compound Semicond. Integr. Circuit Symp., San Antonio, TX, 2006, pp. 271-274.

- [13] G. Crupi and D. Schreurs, *Microwave de-embedding*. Oxford: Academic Press, 2014.

- [14] A. Jarndal and G. Kompa, "An accurate small-signal model for AlGaN-GaNHEMT suitable for scalable large-signal model construction," in *IEEE Microw. and Wireless Compon. Lett.*, vol. 16, no. 6, pp. 333-335, June 2006.

- [15] A. Jarndal, A. Z. Markos and G. Kompa, "Improved Modeling of GaN HEMTs on Si Substrate for Design of RF Power Amplifiers," in *IEEE Trans. on Microw. Theory and Techn.*, vol. 59, no. 3, pp. 644-651, March 2011.

- [16] J. Lee and K. Webb, "A temperature-dependent nonlinear analytic model for AlGaN-GaN HEMTs on SiC," in *IEEE Trans. on Microw. Theory and Techn.*, vol. 52, no. 1, pp. 2-9, Jan. 2004.

- [17] I. Angelov *et al.*, "On the large-signal modelling of AlGaN/GaN HEMTs and SiC MESFETs," *Eur. Gallium Arsenide and Other Semicond. Appl. Symp.*, GAAS 2005, Paris, 2005, pp. 309-312.

- [18] A. Jarndal and G. Kompa, "Large-Signal Model for AlGaN/GaN HEMTs Accurately Predicts Trapping- and Self-Heating-Induced Dispersion and Intermodulation Distortion," in *IEEE Trans. on Electron Devices*, vol. 54, no. 11, pp. 2830-2836, Nov. 2007.

- [19] I. Melczarsky *et al.*, "Compact Empirical Modeling of Nonlinear Dynamic Thermal Effects in Electron Devices," in *IEEE Trans. on Microw. Theory and Techn.*, vol. 56, no. 9, pp. 2017-2024, September 2008.