### software/FPGA co-design for Edge-computing: Promoting object-oriented design

Xuan Sang Le

#### ▶ To cite this version:

Xuan Sang Le. software/FPGA co-design for Edge-computing: Promoting object-oriented design. Other [cs.OH]. Université de Bretagne occidentale - Brest, 2017. English. <NNT: 2017BRES0041>. <tel-01661569>

#### HAL Id: tel-01661569 https://tel.archives-ouvertes.fr/tel-01661569

Submitted on 12 Dec 2017

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### THÈSE / UNIVERSITÉ DE BRETAGNE OCCIDENTALE

sous le sceau de l'Université Bretagne Loire

pour obtenir le titre de DOCTEUR DE L'UNIVERSITÉ DE BRETAGNE OCCIDENTALE Mention : Informatique

École Doctoral Santé, Information, Communication, Mathématique, Matière

> Software/FPGA Co-design for Edge-computing: Promoting Object-oriented Design

présentée par Xuan Sang LE

préparée à École Mines-Télécom, IMT Lille Douai et Lab-STICC UMR CNRS 6285, École Nationale Supérieure de Techniques Avancées de Bretagne

Thèse soutenue le 31 Mai 2017 devant le jury composé de:

**Olivier ROMAIN** Professeur, Université de Cergy-Pontoise/ Rapporteur

**Anne ETIEN** Maître de conférences HDR, Polytech Lille/ Rapporteur

Thomas LEDOUX Maître de conférences, IMT Atlantique/ Examinateur

Ahcene BOUNCEUR Maître de conférences HDR, Université de Bretagne Occidentale/ Examinateur

Loïc LAGADEC Professeur, ENSTA Bretagne / Directeur

Noury BOURAQADI Professeur, Mines-Télécom, IMT Lille Douai/ Co-directeur

©2017 – Xuan Sang LE all rights reserved.

#### Abstract

Cloud computing is often the most referenced computational model for Internet of Things. This model adopts a centralized architecture where all sensor data is stored and processed in a sole location. Despite of many advantages, this architecture suffers from a low scalability while the available data on the network is continuously increasing. It is worth noting that, currently, more than 50% internet connections are between things. This can lead to the reliability problem in realtime and latency-sensitive applications. Edge-computing, which is based on a decentralized architecture, is known as a solution for this emerging problem by: (1) reinforcing the equipment at the edge (things) of the network and (2) pushing the data processing to the edge.

Edge-centric computing requires sensors nodes with more software capability and processing power while, like any embedded systems, being constrained by energy consumption. Hybrid hardware systems consisting of FPGA and processor offer a good trade-off for this requirement. FPGAs are known to enable parallel and fast computation within a low energy budget. The coupled processor provides a flexible software environment for edge-centric nodes.

Applications design for such hybrid network/software/hardware (SW/HW) system always remains a challenged task. It covers a large domain of system level design from high level software to low-level hardware (FPGA). This results in a complex system design flow and involves the use of tools from different engineering domains. A common solution is to propose a heterogeneous design environment which combining/integrating these tools together. However, the heterogeneous nature of this approach can pose the reliability problem when it comes to data exchanges between tools.

Our motivation is to propose a homogeneous design methodology and environment for such system. We study the application of a modern design methodology, in particular object-oriented design (OOD), to the field of embedded systems. Our choice of OOD is motivated by the proven productivity of this methodology for the development of software systems. In the context of this thesis, we aim at using OOD to develop a homogeneous design environment for edge-centric systems. Our approach addresses three design concerns: (1) hardware design, where object-oriented principles and design patterns are used to improve the reusability, adaptability, and extensibility of the hardware system. (2) hardware / software co-design, for which we propose to use OOD to abstract the SW/HW integration and the communication that encourages the system modularity and flexibility. (3) middleware design for Edge Computing. We rely on a centralized development environment for distributed applications, while the middleware facilitates the integration of the peripheral nodes in the network, and allows automatic remote reconfiguration. Ultimately, our solution offers software flexibility for the implementation of complex distributed algorithms, complemented by the full exploitation of FPGAs performance. These are placed in the nodes, as close as possible to the acquisition of the data by the sensors, in order to deploy a first effective intensive treatment.

#### Résumé

L'informatique en nuage (cloud computing) est souvent le modèle de calcul le plus référencé pour l'internet des objets (Internet of Things). Ce modèle adopte une architecture où toutes les données de capteur sont stockées et traitées de façon centralisée. Malgré de nombreux avantages, cette architecture souffre d'une faible évolutivité alors même que les données disponibles sur le réseau sont en constante augmentation. Il est à noter que, déjà actuellement, plus de 50 % des connexions sur Internet sont inter objets. Cela peut engendrer un problème de fiabilité dans les applications temps réel. Le calcul en périphérie (Edge computing) qui est basé sur une architecture décentralisée, est connue comme une solution pour ce problème émergent en: (1) renforçant l'équipement au bord du réseau et (2) poussant le traitement des données vers le bord.

Le calcul en périphérie nécessite des nœuds de capteurs dotés d'une plus grande capacité logicielle et d'une plus grande puissance de traitement, bien que contraints en consommation d'énergie. Les systèmes matériels hybrides constitués de FPGAs et de processeurs offrent un bon compromis pour cette exigence. Les FPGAs sont connus pour permettre des calculs exhibant un parallélisme spatial, aussi que pour leur rapidité, tout en respectant un budget énergétique limité. Coupler un processeur au FPGA pour former un noeud garantit de disposer d'un environnement logiciel flexible pour ce noeud.

La conception d'applications pour ce type de systèmes hybrides (réseau/logiciel/matériel) reste toujours une tâche difficile. Elle couvre un vaste domaine d'expertise allant du logiciel de haut niveau au matériel de bas niveau (FPGA). Il en résulte un flux de conception de système complexe, qui implique l'utilisation d'outils issus de différents domaines d'ingénierie. Une solution commune est de proposer un environnement de conception hétérogène qui combine/intègre l'ensemble de ces outils. Cependant, l'hétérogénéité intrinsèque de cette approche peut compromettre la fiabilité du système lors des échanges de données entre les outils.

L'objectif de ce travail est de proposer une méthodologie et un environnement de conception homogène pour un tel système. Cela repose sur l'application d'une méthodologie de conception moderne, en particulier la conception orientée objet (OOD), au domaine des systèmes embarqués. Notre choix de OOD est motivé par la productivité avérée de cette méthodologie pour le développement des systèmes logiciels. Dans le cadre de cette thèse, nous visons à utiliser OOD pour développer un environnement de conception homogène pour les systèmes de type Edge Computing. Notre approche aborde trois problèmes de conception: (1) la conception matérielle, où les principes orientés objet et les patrons de conception sont utilisés pour améliorer la réutilisation, l'adaptabilité et l'extensibilité du système matériel. (2) la co-conception matériel/logiciel, pour laquelle nous proposons une utilisation de OOD afin d'abstraire l'intégration et la communication entre matériel et logiciel, ce qui encourage la modularité et la flexibilité du système. (3) la conception d'un intergiciel pour l'Edge Computing. Ainsi il est possible de reposer sur un environnement de développement centralisé des applications distribuées, tandis ce que l'intergiciel facilite l'intégration des noeuds périphériques dans le réseau, et en permet la reconfiguration automatique à distance. Au final, notre solution offre une flexibilité logicielle pour la mise en oeuvre d'algorithmes distribués complexes, et permet la pleine exploitation des performances des FPGAs. Ceux ci sont placés dans les noeuds, au plus près de l'acquisition des données par les capteurs, pour déployer un premier traitement intensif efficace.

To my daughter, Uyen Nhi

## Contents

| 1 | Introduction |                                                                             |    |  |  |

|---|--------------|-----------------------------------------------------------------------------|----|--|--|

|   | 1.1          | Context: Internet of Thing, Edge computing and FPGA                         | 1  |  |  |

|   |              | 1.1.1 Internet of Things                                                    | 1  |  |  |

|   |              | 1.1.2 Edge Computing for Cyber-physical Systems                             | 3  |  |  |

|   |              | 1.1.3 Using FPGAs for Edge Computing in IoT: Benefits and Challenges        | 4  |  |  |

|   | 1.2          | Research Objectives and Contributions                                       | 6  |  |  |

|   |              | 1.2.1 Research Objectives                                                   | 6  |  |  |

|   |              | 1.2.2 Contributions                                                         | 7  |  |  |

|   | 1.3          | Outline of the Thesis                                                       | 8  |  |  |

| 2 | State        | e of the Art                                                                | 9  |  |  |

| - | 2.1          | Edge Computing                                                              | 10 |  |  |

|   |              | 2.1.1 Dedicated SN for Edge Computing                                       | 10 |  |  |

|   |              | 2.1.2 Using FPGAs for Edge Computing in IoT                                 | 11 |  |  |

|   |              | 2.1.3 Discussion                                                            | 11 |  |  |

|   | 2.2          | Hardware Design Background                                                  | 12 |  |  |

|   |              | 2.2.1 Overview                                                              | 12 |  |  |

|   |              | 2.2.2 Hardware Design Methodologies                                         | 12 |  |  |

|   |              | 2.2.3 Discussion                                                            | 13 |  |  |

|   | 2.3          | Meta-modeling for System-level Hardware Design Using MDE                    | 14 |  |  |

|   |              | 2.3.1 Model-Driven Engineering                                              | 14 |  |  |

|   |              | 2.3.2 Component-based approaches                                            | 16 |  |  |

|   |              | 2.3.3 Platform-based approaches                                             | 18 |  |  |

|   |              | 2.3.4 UML and Object Oriented based Approaches                              | 20 |  |  |

|   |              | 2.3.5 Summary                                                               | 22 |  |  |

|   | 2.4          | Software/Hardware Co-design                                                 | 24 |  |  |

|   |              | 2.4.1 Early Binding Approaches                                              | 24 |  |  |

|   |              | 2.4.2 Late Binding Approach                                                 | 26 |  |  |

|   |              | 2.4.3 Discussion                                                            | 27 |  |  |

|   | 2.5          | Positioning our work                                                        | 27 |  |  |

| 3 | Prom         | noting Object Oriented Principles on HW Design Using the OoRC Meta-model    | 29 |  |  |

| U | 3.1          |                                                                             | 30 |  |  |

|   | 0.1          | Introduction                                                                | 31 |  |  |

|   | 3.2          | Fine-grained Modeling: FPGA Circuit at RTL Level                            | 32 |  |  |

|   | 0.2          | 3.2.1 Circuit Signals as Data Objects                                       | 32 |  |  |

|   |              | 3.2.2 Circuit Structures Modeling                                           | 33 |  |  |

|   |              | 3.2.3 Discussion                                                            | 34 |  |  |

|   | 3.3          | A Simplified DSL for HW Design                                              | 35 |  |  |

|   | 2.0          | 3.3.1 Overview of the DSL                                                   | 35 |  |  |

|   |              | 3.3.2 OoRCScript Syntax                                                     | 35 |  |  |

|   | 3.4          | Coarse-grained Modeling: Hardware System Level Design Using Object Oriented |    |  |  |

|   |              |                                                                             |    |  |  |

|   |            | 3.4.1 Basic OO Concepts for HW Design                                    | 38       |

|---|------------|--------------------------------------------------------------------------|----------|

|   |            | 3.4.2 Basic OO Design Operations                                         | 40       |

|   |            | 3.4.3 OOD Pattern on Hardware Design                                     | 40       |

|   | 3.5        | Circuit Model Transformation                                             | 47       |

|   |            | 3.5.1 Overview of the Transformation Process                             | 47       |

|   |            | 3.5.2 Exporting Circuit Models                                           | 48       |

|   |            | 3.5.3 Legacy VHDL Reuse via a Dedicated VHDL Parser                      | 48       |

|   |            | 3.5.4 Automatic Circuits Integration and Configuration                   | 50       |

|   |            | 3.5.5 Discussion                                                         | 51       |

|   | 3.6        |                                                                          | 52       |

|   |            | 3.6.1 Execution Model: time-driven vs. event-driven                      | 52       |

|   |            | 3.6.2 Event-driven Simulation of Circuit Models                          | 53       |

|   | 3.7        |                                                                          | 54       |

|   |            |                                                                          | 54       |

|   |            | 0                                                                        | 55       |

|   | 3.8        |                                                                          | 57       |

|   | 0.0        |                                                                          | •••      |

| 4 | OoR        | CBridge: Seamless Integration of FPGAs with High-Level Software          | 59       |

|   | 4.1        |                                                                          | 60       |

|   | 4.2        |                                                                          | 62       |

|   |            |                                                                          | 62       |

|   |            |                                                                          | 64       |

|   |            | 0                                                                        | 64       |

|   | 4.3        | 0 11 0 7 11 0                                                            | 65       |

|   |            |                                                                          | 65       |

|   |            |                                                                          | 66       |

|   |            |                                                                          | 66       |

|   |            | 1 0                                                                      | 67       |

|   | 4.4        |                                                                          | 69       |

|   | 4.5        | / 80.0                                                                   | 71       |

|   | 4.5        |                                                                          | 71       |

|   |            |                                                                          | 73       |

|   |            |                                                                          | 74       |

|   |            |                                                                          |          |

|   | 4.6        | ů –                                                                      | 75<br>76 |

|   | 4.0        | Summary                                                                  | /0       |

| 5 | CaR        | DIN: A Dedicated Environment for Edge Computing on Reconfigurable Sensor |          |

| J |            |                                                                          | 79       |

|   | 5.1        |                                                                          | 80       |

|   | 5.2        |                                                                          | 82       |

|   | 5.2<br>5.3 |                                                                          | 83       |

|   | 5.5        | 5                                                                        | 83       |

|   |            |                                                                          |          |

|   |            | , ,                                                                      | 85       |

|   | E 4        |                                                                          | 87       |

|   | 5.4        | ,                                                                        | 88       |

|   |            |                                                                          | 88       |

|   |            | 8                                                                        | 90       |

|   | 5.5        | , , , , , , , , , , , , , , , , , , , ,                                  | 91       |

|   | 5.6        | Summary                                                                  | 95       |

| 6   | Conclusion and Perspectives |                          |     |  |  |  |  |  |

|-----|-----------------------------|--------------------------|-----|--|--|--|--|--|

|     | 6.1                         | Contribution Summary     | 97  |  |  |  |  |  |

|     |                             | Current and Future Works |     |  |  |  |  |  |

| Ref | erenc                       | es                       | 111 |  |  |  |  |  |

## Acknowledgments

Firstly, I would like to express my sincere gratitude to my advisors Prof. Noury Bouraqadi and Prof. Loic Lagadec for the continuous support of my Ph.D study and related research, for their patience, motivation, and immense knowledge. Their guidance helped me in all the time of research and writing of this thesis. I could not have imagined having better advisors and mentors for my Ph.D study.

My sincere thanks also goes to my supervisors Dr. Luc Fabresse, Dr. Jean-Christophe Le Lann, and Dr. Jannik Laval, for their kindness, their availability and their advices on techincal and scientific aspects during this thesis. Without their precious support it would not be possible to conduct this research.

Besides my advisors and supervisors, I would like to thank the rest of my thesis committee: Prof. Olivier Romain, Dr. Anne Etien, Dr. Thomas Ledoux and Dr. Ahcene Bounceur, for their insightful comments and encouragement, but also for the hard question which incented me to widen my research from various perspectives.

I thank my fellow labmates at IMT Lille Douai and ENSTA Bretagne with whom i have pleasure to work and for all the fun we have had in the last three years.

Last but not the least, I would like to thank my family: my wife, Phuong TRAN and to my daughter, Uyen Nhi, for supporting me spiritually throughout writing this thesis and my life in general.

Xuan Sang LE

## List of Figures

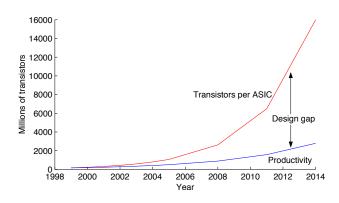

| 2.1        | Hardware design productivity gap: number of transistors available on a chip vs. the ability for the transistors to be used efficiently in a design [int 11, Sed06] | 12       |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

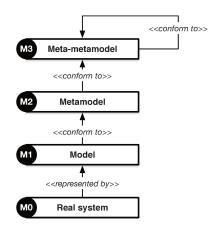

| 2.2        | Four layers meta-modelling framework                                                                                                                               | 15       |

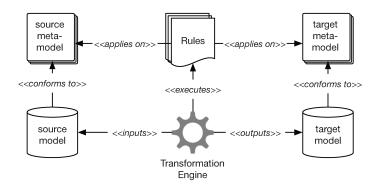

| 2.3        | Model transformations allow to remodel an input model by executing transformation                                                                                  |          |

|            | rules <b>using a transformation</b> engine                                                                                                                         | 15       |

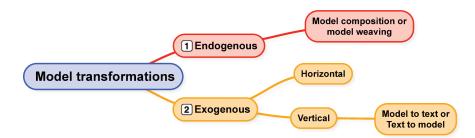

| 2.4        | Classification of model transformations.                                                                                                                           | 17       |

| 2.5        | Early binding: Both SW/HW parts are designed simultaneously and separately. An                                                                                     |          |

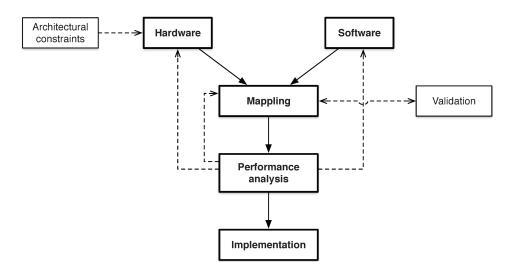

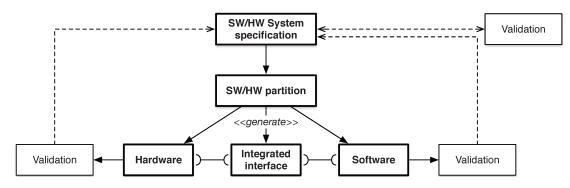

| 2.6        | automatic mapping process is needed to interfacing both parts                                                                                                      | 25       |

|            | or MDE-based). The system handles automatically the partition and the inter-task for                                                                               |          |

|            | interfacing at the high-level-synthesis phase.                                                                                                                     | 26       |

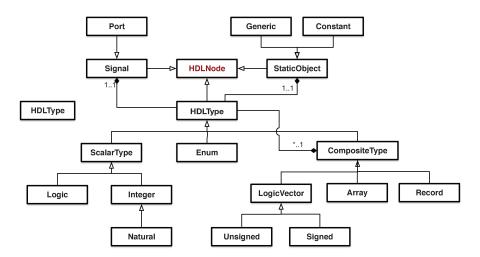

| 3.1        | Simplified class diagram models signals and their associated data types. OoRC supports only synthesizable data type                                                | 32       |

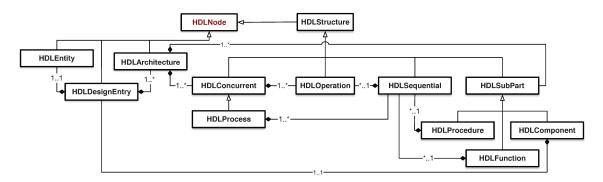

| 3.2        | Classes define meta-descriptions of hardware structures. Theses meta-descriptions                                                                                  | 02       |

| 0.2        | are based on synthesizable VHDL structures                                                                                                                         | 34       |

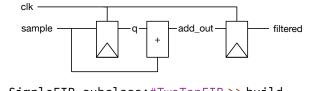

| 3.3        | Description of the FIR filter in listing 3.1 using OoRCScript                                                                                                      | 36       |

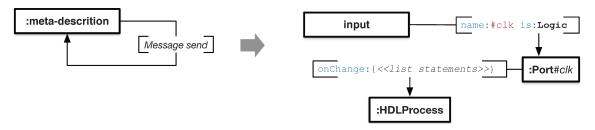

| 3.4<br>3.4 | Basic principle of OoRCScript syntax: "sending a message to a description will gen-                                                                                | 50       |

| 5.4        | erate a new description"                                                                                                                                           | 36       |

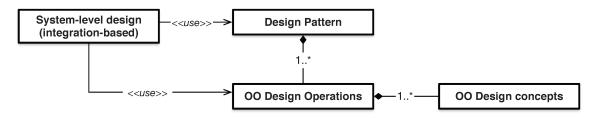

| 3.5        | Using object oriented technique on HW system-level design                                                                                                          | 38       |

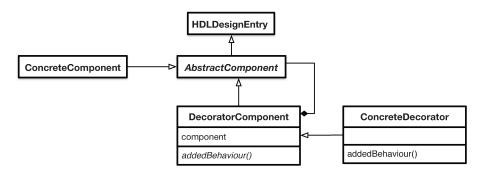

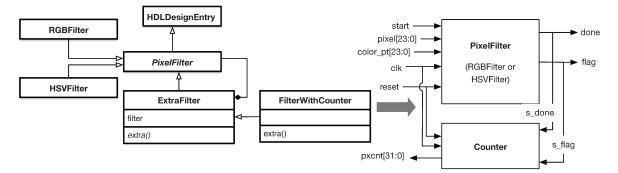

|            |                                                                                                                                                                    | 30<br>41 |

| 3.6<br>3.7 | Base structure of decorator pattern applied on hardware design                                                                                                     | 41       |

|            | Example: attach more responsibility to a pixel filter using decorator pattern                                                                                      | 43<br>43 |

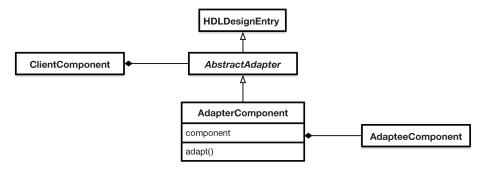

| 3.8        | Base structure of adapter pattern applied on hardware design                                                                                                       |          |

| 3.9        | Example: Interface conversion using adapter pattern                                                                                                                | 44       |

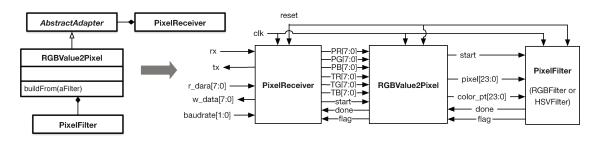

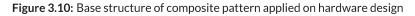

| 3.10       | Base structure of composite pattern applied on hardware design                                                                                                     | 45       |

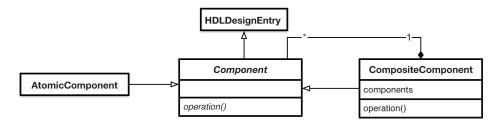

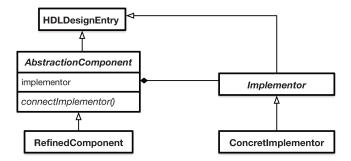

| 3.11       | Base structure of bridge pattern applied on hardware design                                                                                                        | 46       |

| 3.12       | Example: Interface & architectural implementation decoupling using bridge                                                                                          | 46       |

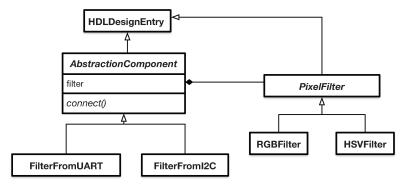

| 3.13       | T-diagrams represent basic model transformations supported in OoRC                                                                                                 | 47       |

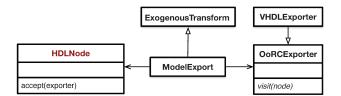

| 3.14       | By using a visitor pattern, a circuit model can be independently exported to other model (VHDL/Verilog, etc.)                                                      | 48       |

| 3.15       | VHDL designs are parsed into parser trees before being converted to circuit models                                                                                 |          |

| 0.10       | using OoRCAdapter                                                                                                                                                  | 49       |

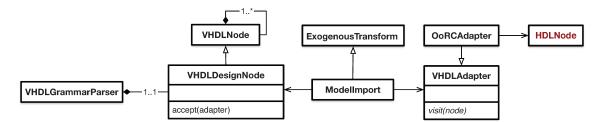

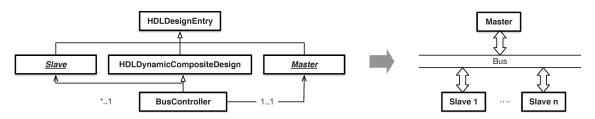

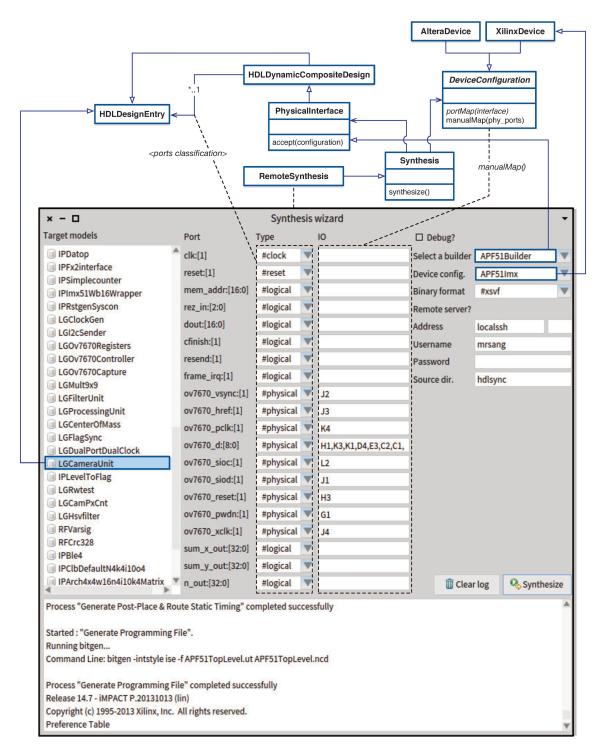

| 3.16       | HDLDynamicCompositeDesign allows semi-automatic composition of models and pro-                                                                                     | .,       |

| 0.10       | vides a virtual process method for manual models linking                                                                                                           | 51       |

| 3.17       | A predefined Master-slave bus interface: IP designers just need to subclass Slave or                                                                               | 0.       |

| 0.17       | Master to define their application logic                                                                                                                           | 51       |

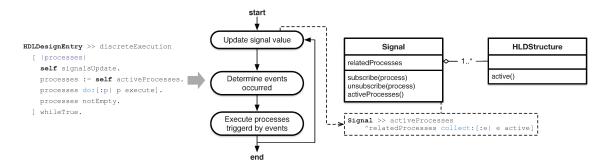

| 3.18       | Event-driven simulation of discrete system using an observer pattern. Assignment of                                                                                |          |

|            | a value to a signal will cause all related processes become active.                                                                                                | 53       |

| 3.19       | Class digram design and the corresponding GUI implementation of our model syn-                                                                                     |          |

|            | thesis toolset                                                                                                                                                     | 56       |

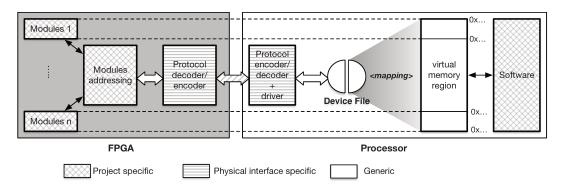

| 4.1        | Memory mapping is used to provide a convenient access to FPGA from software. The                                                                                   |          |

|            | solution must be as generic as possible to enable the reuse of the system.                                                                                         | 61       |

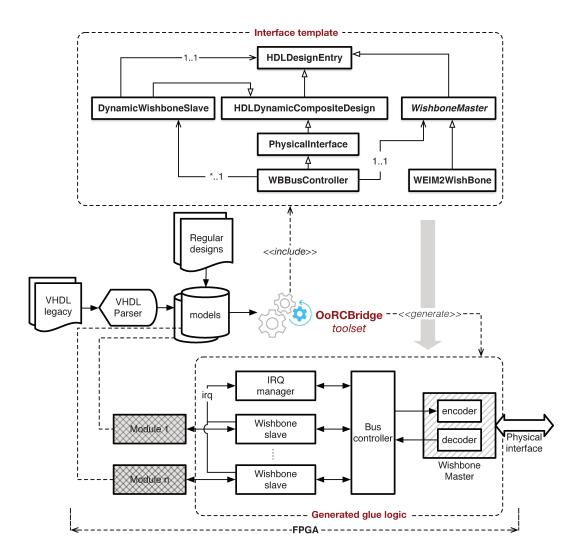

| 4.2  | In OoRCBridge, OOD is used to design interface template. Designs are reused , refined and enriched to provide a generic, automatic and modularized IPs integration |    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | mechanism                                                                                                                                                          | 63 |

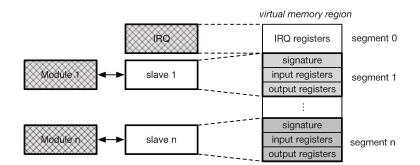

| 4.3  | Addressing scheme generated automatically by the bus controller                                                                                                    | 64 |

| 4.4  | OoRCBridge middleware provides generic APIs for hardware communication. The<br>OoRC toolset generates automatically application-specific accessing classes using   |    |

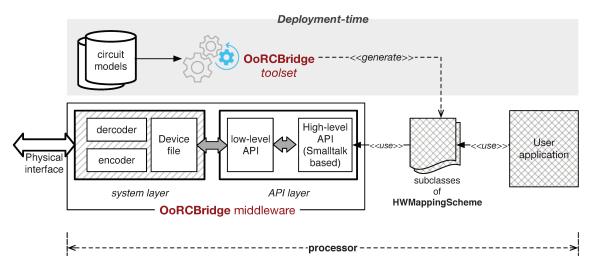

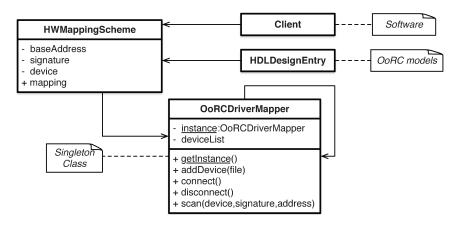

|      | these APIs                                                                                                                                                         | 65 |

| 4.5  | HWMappingScheme abstracts and encapsulates hardware circuits as regular soft-                                                                                      |    |

| 1.0  |                                                                                                                                                                    | 67 |

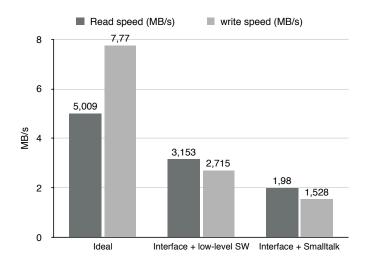

| 4.6  | Performance measurement for continuously read/write test                                                                                                           | 68 |

| 4.7  | DebuggableSlave allows to inject automatically a debug sub-circuit to the slave and                                                                                |    |

|      | turns it to a Breakpoint controller                                                                                                                                | 69 |

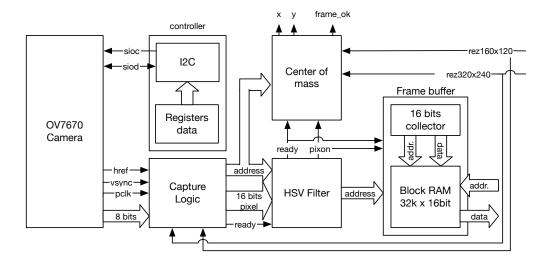

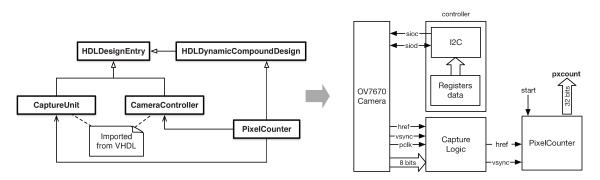

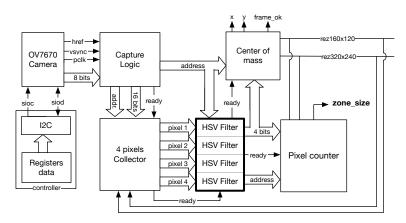

| 4.8  | Original design of the detection circuit                                                                                                                           | 72 |

| 4.9  | Mixture use of imported VHDL designs and custom design using OoRCSCript. The                                                                                       |    |

|      | pixel counter simply count all received pixels                                                                                                                     | 73 |

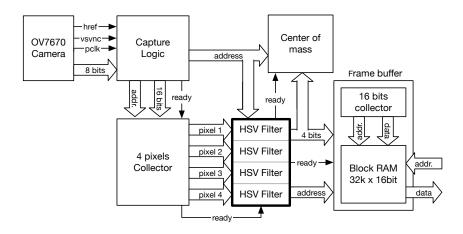

| 4.10 | Optimized design of the detection circuit with 4 HSV filters in parallel                                                                                           | 74 |

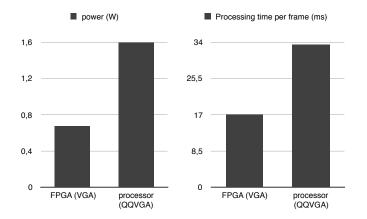

| 4.11 | On the left, the power consumption between the software and hardware implemen-                                                                                     |    |

|      | tation of the object detection. On the right, the processing time per frame of each                                                                                |    |

|      | version                                                                                                                                                            | 75 |

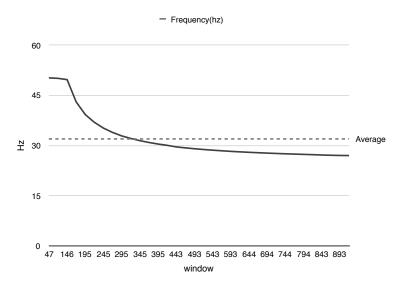

| 4.12 | Publishing frequency of the topic /spybot/objectpos in regarding different window                                                                                  |    |

|      | sizes of messages                                                                                                                                                  | 76 |

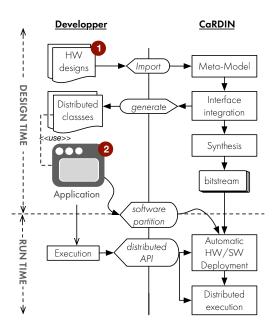

| 5.1  | Workflow of CaRDIN. Developers need to: (1) import the HW IP to system for soft-                                                                                   |    |

| 0.1  | ware/bitstream generation; (2) use the generated classes to develop their application                                                                              | 81 |

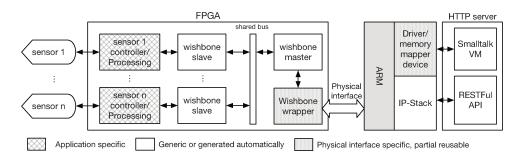

| 5.2  | Simplified hardware/software architecture of a edge-centric node: the system is                                                                                    | •  |

|      | made as generic as possible by maximizing the reusability of software/hardware                                                                                     |    |

|      | components                                                                                                                                                         | 83 |

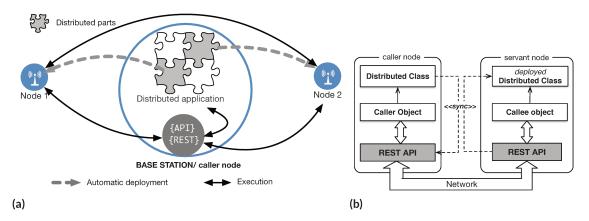

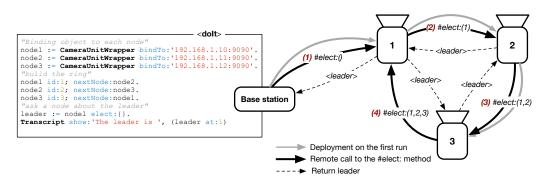

| 5.3  | (a) The entire application is developed on base station but is executed in distributed                                                                             |    |

|      | manner; (b) Communication between distributed objects residing in the caller node                                                                                  |    |

|      | and the servant node                                                                                                                                               | 83 |

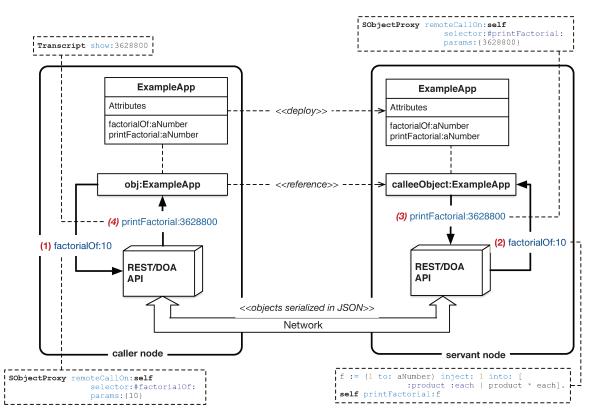

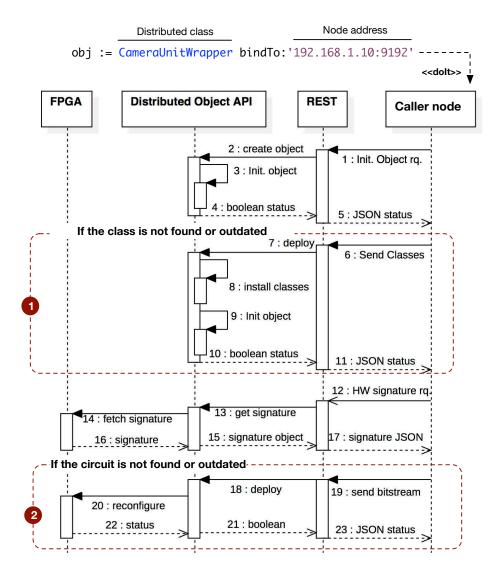

| 5.4  | The automatic deployment and remote call of the example in listing 5.1                                                                                             | 85 |

| 5.5  | If the SW/HW is not deployed or outdated, the initialization of a distributed object                                                                               |    |

|      | will automatically trigger the reconfiguration of the node                                                                                                         | 86 |

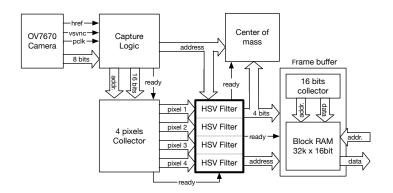

| 5.6  | Object detection implementation on the FPGA.                                                                                                                       | 88 |

| 5.7  | Network load of the node on different operations: (5.7a) the software/bitstream                                                                                    |    |

|      | reconfiguration process ([ $t$ , $t$ + 2]); (5.7b) the frequently fetching test ([ $t$ , $t$ + 70]) and                                                            |    |

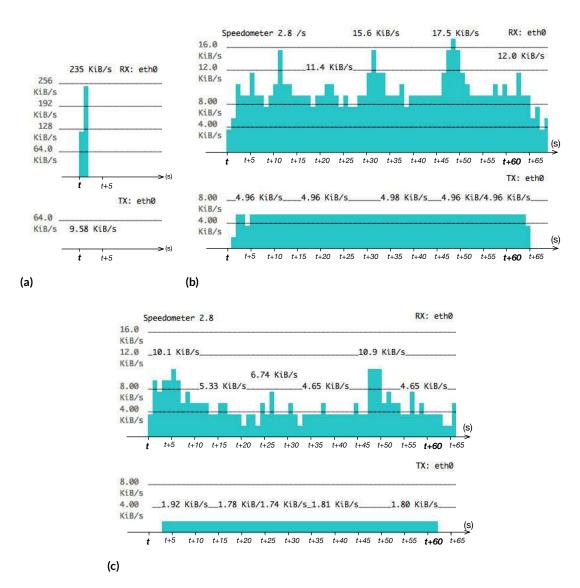

|      | lastly (5.7c) the streaming test ([ $t$ , $t$ + 70]). $t$ is the time when an operation begins                                                                     | 92 |

| 5.8  | 3 camera sensor nodes tracking a moving ball. Question: Which camera actually                                                                                      | _  |

|      | has the ball?                                                                                                                                                      | 93 |

| 5.9  | The frame buffer unit is replaced by the pixel counter unit to count the filtered pixels.                                                                          | 93 |

| 5.10 | Deployment and execution of the distributed application via CaRDIN middleware.                                                                                     | 95 |

## Listings

| 3.1        | VHDL implementation of a simplest low pass FIR filter $y_n = x_n + x_{n-1} + x_{n-1} + x_{n-1}$ | 34  |

|------------|-------------------------------------------------------------------------------------------------|-----|

| 3.2        | Function/procedure definition                                                                   | 38  |

| 3.3        | Design reuse                                                                                    | 38  |

| 3.4        | An optimized re-implementation of <i>SimpleFIR</i> using inheritance and override features .    | 39  |

| 3.5        | Abstract architecture                                                                           | 40  |

| 3.6        | OoRCScript abstract method                                                                      | 40  |

| 3.7        | Example of adding a counter to an existing pixel filter                                         | 41  |

| 3.8        | Implementation of interface converting using adapter pattern                                    | 43  |

| 3.9        | Implementation: decouple data interface (UART, I2C)                                             | 45  |

| 3.10       | Create a new FIR filter model and resize all data signals to 16 bits                            | 48  |

| 3.11       | Functional simulation implementation                                                            | 54  |

| 3.12       | Behavioural simulation implementation                                                           | 54  |

| 4.1        | Example of using hardware breakpoint in software. The HWCounterMapping is the                   |     |

|            | accessing class of a simple hardware counter. This counter has an input and an output           |     |

|            | signal, and counts from 0 to the value of input (100). The breakpoint is set for output         |     |

|            | at value 50 (first operand). Note that the slave uses the address of ouput to select the        |     |

|            | second operand for the comparator                                                               | 70  |

| 4.2        | A mixture of ROS API and OoRCBridge middleware API. The code publishes object                   |     |

| <b>-</b> 1 | positions through the ROS middleware                                                            | 75  |

| 5.1        | ExampleApp -a subclass of SSSynchronisableObject- is a distributed class with one               |     |

|            | annotated method (#factorialOf:). On the base station, at the first object instantiation        |     |

|            | of the class (line 15), the class is automatically deployed on remote node. Line 16             | •   |

| <b>F</b> 0 | requires the node to calculate the factorial of 10, then prints it on the base station          | 84  |

| 5.2        | Example of a distributed class. The methods with a pragma are executed remotely.                | 0.0 |

| 5.0        | Others are locally executed methods                                                             | 88  |

| 5.3        | Token Ring Implementation for camera surveillance examples using CaRDIN                         | 94  |

## Glossary

- **API** Application Programming Interface. iv, x, xi, 2, 8, 14, 20, 30, 31, 35, 48, 59, 62, 65–71, 75, 76, 79, 81–85, 89, 98

- AST Abstract Syntax Tree. 99

- **AXI** Advanced eXtensible Interface. 62

- **BLIF** Berkeley Logic Interchange Format. 49

- **CAD** Computer-aided design. 31, 32, 48, 57, 98, 99

- CLB Configurable Logic Block(s). 4

- **CORBA** Common Object Request Broker Architecture. 87

- **CPS** Cyber-physical Systems. 3

- **DOA** Distributed Objects API. 83-85, 87, 94, 95, 98, 99

- **DSL** Domain Specific Language. iii, 29–31, 35, 37, 38, 49, 57, 97

- EC Edge Computing. 3, 4, 10, 11

- EDA Electronic Design Automation. 12, 17, 18

- FIR Finite impulse response. ix, xi, 35, 36, 48

- **FPGA** Field Programmable Gate Array. iii, ix, 1, 4, 5, 7, 10, 11, 13, 15, 21, 25–29, 31, 32, 35, 52, 55, 60–62, 64–75, 80–82, 85, 87–91, 97–100

- FSM Finite State Machine. 18, 20, 26, 27

- FSMD Finite State Machine with Datapath. 17

- GPIO General Purpose Input/Output. 72

- GUI Graphic User Interface. ix, 18, 31, 55, 56, 99

- **HDL** Hardware Description Language. 12–14, 17, 18, 20–22, 24, 25, 27, 28, 30, 31, 35, 51, 52

- HLS High Level Synthesis. 13, 24, 26, 30, 60

- HTTP Hypertext Transfer Protocol. 82, 87, 90

- **HW** Hardware. iii, iv, ix, x, 5–8, 12, 13, 16, 19, 21–31, 34, 35, 38, 39, 45, 51, 59, 60, 65, 79–82, 85, 86, 97–99

- I2C Inter-Integrated Circuit. xi, 45, 46

- IEEE Institute of Electrical and Electronics Engineers. 17, 32, 48

- **IoT** Internet of Things. iii, 1-4, 9-11, 27, 28, 97, 100

- IP (1) "Internet Protocol" in the context of networking, in case of hardware design, the term means

(2) "Intellectual Property". ix, x, 8, 10–13, 17–22, 24, 25, 27, 30, 31, 50–52, 57, 63–65, 79–82, 95, 97, 98

- JSON Javascript Object Notation. 82, 84

- MARTE Modelling and Analysis of Real-time and Embedded Systems. 20, 21, 26

- **MDE** Model Driven Engineering. ix, 8, 13, 14, 16, 18, 20–24, 26, 27, 30

- **MOF** Meta Object Facility. 15

- **OMG** Object Management Group. 15

- **OO** Object Oriented. iv, 20-22, 29, 38, 40

- **OOD** "Object Oriented Design". iv, x, 6-8, 18, 20-22, 24, 25, 27-31, 34, 35, 40, 63, 64, 97-99

- OOL Object Oriented Language. 20

- **OoRC** Objectification of Reconfigurable Circuits. iii, 8, 29–35, 47–53, 55, 57, 61, 81

- PCLe (Peripheral Component Interconnect Express. 60

- **REST** Representational state transfer. 2, 81, 82, 84, 87, 89, 90

- **ROS** Robot Operating System. iv, xi, 25, 59, 71, 75, 76

- RTL Register Transfer Level. iii, 7, 8, 12, 13, 17, 27, 29–32, 48, 91, 97

- **SN** Sensor Network(s). 2, 3, 10, 11, 80, 87, 100

- **SOAP** Simple Object Access Protocol. 2

- **SoC** System on a Chip. 19–21, 26, 60

- SW Software. iv, ix, x, 5–8, 11, 12, 16, 18, 19, 24–28, 59–61, 65, 79–82, 85, 86, 97–99

- **UART** Universal asynchronous receiver/transmitter. xi, 43, 45, 46

- UML Unified Modelling Language. iii, 9, 14, 20–22, 25–27, 32, 35, 99

- VHDL Very High Speed Integrated Circuit Hardware Description Language. iv, ix-xi, 5, 8, 12, 18, 20, 21, 25, 29, 31–35, 38, 39, 47–51, 55, 57, 64, 67, 68, 72–74, 81, 89, 91, 97, 99

- VM Virtual Machine. 81, 82, 85, 87, 90, 98, 99

- WIEM Wireless External Interface Module. 60, 62, 67, 68, 88

- XML Extensible Markup Language. 17, 18, 82

# Introduction

#### Contents

| 1.1 | Context                                   | : Internet of Thing, Edge computing and FPGA                   | 1 |

|-----|-------------------------------------------|----------------------------------------------------------------|---|

|     | 1.1.1                                     | Internet of Things                                             | 1 |

|     | 1.1.2                                     | Edge Computing for Cyber-physical Systems                      | 3 |

|     | 1.1.3                                     | Using FPGAs for Edge Computing in IoT: Benefits and Challenges | 4 |

| 1.2 | 1.2 Research Objectives and Contributions |                                                                |   |

|     | 1.2.1                                     | Research Objectives                                            | 6 |

|     | 1.2.2                                     | Contributions                                                  | 7 |

| 1.3 | Outline                                   | of the Thesis                                                  | 8 |

#### 1.1 Context: Internet of Thing, Edge computing and FPGA

#### 1.1.1 Internet of Things

Internet of things (IoT) is a concept increasingly supported by various stakeholders and market forces. It is foreseen to be a world-wide network of interconnected devices or objects (things) through wired and wireless connections [VF13]. The network provides a unique addressing scheme and creates a pervasive environment where a person can interact anytime with the digital and physical worlds. The primary goal is to enable things to be connected anytime, anywhere and with anything or persons using existing network infrastructure. Objects can identify themselves and have seamless intelligence for context decision making. IoT can be considered as the next evolution of the internet [Eva11] and has many potential applications, especially in smart systems such as healthcare, Smart Cities, Smart Grids, Smart Cars and mobility, Smart Homes and Assisted Living, Smart Industries, Public safety, Energy & environmental protection, Agriculture, etc.

#### 1.1.1.1 Resource for IoT

The existing internet infrastructure is the primary resource for IoT. Most IoT devices are IP-enabled<sup>\*</sup> and are able to easily participate to the internet. Web services –such as REST, SOAP, etc.– are well established mechanisms for the communication between IoT nodes. The advantage of web services is that they are general purpose and thus, can be easily integrated to others systems (e.g. IoT systems) that are built on standard (and general purpose) IT components. The passing of IP to IPv6 allows an unrestricted address scheme and enables a large-scale of things.

At the physical level (sensor, actuator, etc.), where the devices (things) actually interact with the real world, Sensor Networks (SN) are an important resource for IoT architecture. IoT can be considered as an evolution [MPV11] of SN at an internet-scale, thus existing work on SN can be adapted to IoT. SN offer a virtual layer where the digital system can communicate with the physical environment. Typically, a SN architecture consist of 4 main concepts [CF14]:

- Network components: elements that enable connectivity within the network, connect an application platform at one end of the network with one or more actual physical devices. These components correspond to the concepts of node, gateway, relay, sensor and actuator.

- Hardware platforms: The hardware requirement necessary for sensor/actuator nodes, computational/functional nodes (relay, server).

- Middlewares: software stack create an virtual layer between application and the physical world. They aim at operating, monitoring and managing the sensor network. They are often generic and flexible to different application scenario.

- Topology: describes how the SN is organized. The most common network topologies used in SN are star, tree, mesh or hybrid networks that combine the other ones. In the context of IoT, any kind of IP-based topologies can be applied.

At the processing level, cloud computing is currently the most referenced computational model for IoT [BdDPP16]. Cloud computing adopts a centralized architecture with large virtual ability of storage and processing power. It is defined [MG11] as "a model for enabling ubiquitous, convenient, on-demand network access to a shared pool of configurable computing resources (e.g., networks, servers, storage, applications, and services) that can be rapidly provisioned and released with minimal management effort or service provider interaction...". IoT can benefit from this model for sensor data collecting, processing and decision making. The cloud can expose different services for sensor data usage (e.g. API, web services). It creates a virtual layer between things and applications, thus hiding the complexity of tasks like system development, integration and management, etc.

#### 1.1.1.2 Potential Problem of current IoT configuration

For the last decades, we have seen an important increase of IoT devices. A research in [Fri 13] (2013) shows that, in 2011, there were more than 15 billion things on the internet, over 50% internet connections are between or with things. By 2020, this number can go up to more than 30 billion things and

<sup>\*</sup> Internet Protocol

over 200 billion intermittent connections are forecasted. All the connections are based on the clientcloud model. Sensor data such as thermostats, surveillance cameras, healthcare system measurement, etc. are centralized to the cloud. This is not always obvious since IoT devices have different radical characteristics. Some are occasional accessed while others require realtime always-on connections. Connection bandwidth<sup>†</sup> is another crucial factor, many devices are satisfied with low bandwidth connections while others need a high bandwidth for data transfer. This is often referred as the Big-data problem [ZE<sup>+</sup> 11].

This centralized infrastructure of cloud suffers from a low scalability while the available data is continuously increasing. In real-time IoT systems this can lead to latency problems. That is, a large amount of IoT nodes may cause a work overhead to the system due to an intensive quantity of data to be transferred over the network. This costs network resources and degrades the response time of the system. The value for decision making of sensor data may be lost while it is traveling across the network. For data processing, although multi-core processors (on the cloud) are powerful enough for mass processing, it is not guaranty that they will be suitable for future calculation requirements of IoT.

Sensor networks, the base of IoT, are often considered as networks of simple devices with limited performance. These devices are only used for data acquisition and transmission. This restricted vision leads to simple communication-centric middleware models. While these devices and middleware respond well the requirements of SN, they may be not suitable at the scale of IoT. IoT systems, especially in smart system, may need more powerful devices with the ability to perform some local computations and decision making.

#### 1.1.2 Edge Computing for Cyber-physical Systems

Cyber-physical systems (CPS) are integrations of computation and physical processes [LeeO8]. It can be considered as a merger of embedded systems –a composition of standalone computing elements – and sensor network. CPS shares the same basic architecture with IoT. Nevertheless, it presents a higher combination and coordination between physical and computational elements [RHTO15]. The integration of software-intensive embedded systems and internet communication into CPS is considered to be the next revolution of IoT. CPS provides the necessary infrastructure to deal with the Big-data problems.

"In many aspects of human activity, there has been a continuous struggle between the forces of centralization and decentralization..." [GLME<sup>+</sup>15]. While today internet activities are dominant by the cloud, solution for the emerging IoT problems (as presented) requires a new evolution for the computational model. The network topology and the computing resource distribution need to be revised, in order to exploit the powerful features of IoT. The combination of Edge computing (EC) and CPS can be considered as a solution for these problems by: (1) migrating from a centralized architecture (cloud) to a distributed computing architecture; (2) strengthening the equipment at the edge of the network, where sensors are deployed and (3) performing analytics and knowledge generation at the source of the data.

<sup>&</sup>lt;sup>†</sup>Today, two thirds of Internet traffic are dedicated to image transmission, this can go up to 80% in the next years

Lopez et al. [GLME<sup>+</sup>15] and Faure et al. [FFH<sup>+</sup>11b, FFH<sup>+</sup>11a] share a human-centric vision on EC in which they consider the important role of human in the edge devices. This vision shows a global view of edge-centric computing with different interesting discussions about: Trust, Privacy, Control, Intelligence and Proximity. My vision here, in this thesis, is limited in the context of IoT and shares some similarities with one presented by Bonomi et al. [BMZA12], where EC extends the cloud computing to the edge of the network. EC considers a node-oriented view of the internet. This architecture consists of data center and clouds at the core and surrounding by nodes with small web server and content-distributed network. At the edge of the network, some distinguishing characteristics can be found:

- Low latency and proximity: by pushing the data processing to the edge of the network, a large

amount of raw sensor data can be processed locally in order to produce a compact and rich

information before delivery to the centralized point. This reduces the network traffic and thus

allows a fast response time. It also adds the possibility of filtering sensor data before delivery.

EC promotes also the distributed communication between closed nodes rather than using a faraway central point (cloud).

- Scalability: EC allows large-scale sensor network with large number of nodes since the network overload are distributed to the edge.

- Realtime interaction: EC is suitable for realtime IoT applications by allowing fast response time between things and application (over the network).

- Heterogeneity: different form factor of edge-devices can be easily deployed in wide-variety of EC environment.

- Intelligence and Control are on the edges: nowadays, hardware devices become smaller and more powerful while being cheaper. Thus, IoT devices have more processing and storage capacity. This implies that edge-centric nodes are more capable and can make local decision and control what to do with sensor data.

Edge-centric nodes are processing-centric, thus, requires more processing capability. However, as regular embedded systems, they are constrained by power consumption. There are always the struggle to balance the performance/energy ratio on these systems. Moreover, as complex processing units, edge-centric nodes need an evolutive and flexible architecture to boost the application development productivity.

#### 1.1.3 Using FPGAs for Edge Computing in IoT: Benefits and Challenges

#### 1.1.3.1 FPGAs

FPGAs [Xil] –stands for Field Programmable Gate Array– are integrated circuits designed to be reconfigured by designers. They were first invented by Xilinx in 1985 and have been increasingly grown up since then. Xilinx and Altera (now acquired by Intel) are two vendors that have a crucial role in the development of FPGAs. These devices are based on a matrix of configurable logic blocks (CLBs) connected by programmable interconnects (switches). Thus FPGAs can be reconfigured to fit different application contexts after manufacturing. This can be done by specifying the functionality of each CLB and then wiring them together (using configurable switches). Traditionally, FPGA configurations are described using Hardware Description Languages such as VHDL or Verilog. These descriptions are synthesized, using dedicated synthesis tools, into binary form (bitstream), that configures the device.

FPGAs are used in wide range of applications such as Aerospace, Automotive, Data Center, Medical, Security, Image and Signal processing, etc. Advantageous characteristics of FPGAs are: (1) Reconfigurability and Flexibility: FPGAs are reconfigurable and can implement easily tailored circuits for different application contexts; (2) Performance: FPGAs enable parallel and fast computations, thus are suitable for acceleration purpose; (3)Energy consummation: direct parallel hardware execution of tasks avoids the overhead problem of traditional software system such as processors and thus is energy-friendly; (4) Maintainability: FPGAs circuits can be easily reconfigured when performance improvements or bug fix are available; (5) Reliability: FPGA circuits are a real hardware implementation of tasks, they minimize the reliability problem in comparison to software on processors since tasks are executed in parallel and have their own deterministic hardware resource.

#### 1.1.3.2 FPGAs and Edge-computing

As stated, in edge-computing, edge-centric nodes' functionality often exceeds simple data collection and embeds more complex features. These nodes require more processing capabilities while keeping power consumption low. Reconfigurable architectures such as FPGAs are known to enable parallel and fast computations within a low energy budget, hence can play a crucial role in edge-centric nodes [DLPBT12]. FPGAs add more processing ability to the nodes and thus allow to locally perform more sophisticated tasks. Furthermore, using FPGAs improves the flexibility of the node's hardware. That is, the hardware can be simply tailored to adapt to different kinds of sensors.

Today FPGA devices often come in a hybrid form factor consisting of an FPGA coupled with an embedded processor (e.g. ARM). This kind of devices is ideal for building edge-centric nodes since: (1) they offer the hardware acceleration (FPGA) while (2) providing a flexible and powerful software environment (processor) for complex middleware and applications (IP-stack, web services).

#### 1.1.3.3 Challenges

Digital Hardware (FPGAs) design is always a complicate task. The design process requires a specific knowledge which remains a challenge for developers and usually results in a loss of productivity. Especially, when FPGAs are used together with advanced software systems (edge-centric middleware, web services, distributed content network, etc.), the problem of HW/SW co-design (detailed in section 2.4) becomes a real challenge. There is a need for a dedicated environment to support efficient development and deployment of such hybrid systems into the network. The environment should address to the following criteria:

- Generalization and Heterogeneity: since we target a network of nodes rather than a single device, the design environment (both SW and HW) should be generic enough to deal with different edge-centric devices (FPGA/processor). A standardized environment also helps applying design constraints on the system and thus better support system scalability.

- Integrability and Interoperability: the environment should promote the integration of: (1) SW and HW parts in an individual node and (2) the integration of each node to the over-all net-

work. A common communication protocol is needed for the SW/HW interfacing as well as the distribution of content over the network.

- Reconfigurability and maintainability: a network may contain hundreds to thousands of hybrid nodes, manual deployment, reconfiguration, or maintenance of each node is an important issue. An automatic mechanism is mandatory for remote (over-the-network) deployment and configuration of nodes, both on SW and HW.

- Distributed computing: Edge computing relies on distributed computing to push the processing to the edge. Therefore, middleware should promote the development and deployment of distributed algorithm/application over the network.

These challenges cover a large domain of system level design from high level software to low level hardware. On the one hand, we rely on an high-end edge-centric (based on web services) software environment for end user application development and deployment. On the other hand, we need to deal with low-level FPGA design and SW/HW integration. There is always the need of a unified design methodology and environment for closing this important gap between the two worlds.

#### 1.2 Research Objectives and Contributions

#### 1.2.1 Research Objectives

When looking at existing design methodologies for both SW and HW system, it is clear that software design methodologies, such as Object Oriented Design (OOD), are in advance of hardware, in term of *productivity*. Hardware design always remains a long and tedious process, especially when it comes to the SW/HW co-design problem. This result in a complex system design flow and involve the use of tools from different engineering domains. Common solutions tend to propose a heterogenous design environment that integrates/combines these tools togethers. However, the heterogeneous nature of this approach can pose the reliability problem when it comes to data exchanges between tools of different expertise domains (i.e. syntactical and semantics interoperability). Our motivation is to propose a homogeneous design methodology and environment for such system to minimize this problem.

This work studies the application of modern design methodologies, in particular the OOD, on embedded system design. Firstly, we aim at profiting object oriented principles to hardware design for a more productive HW design environment. This latter complements the traditional HW design methodologies by promoting the concepts of Generalization, Generation, Standardization and Separation of concerns. Therefore it allows better system Reusability, Maintainability, and Extendability.

Secondly, we explore the use of OOD to produce a uniform methodology and environment for SW/HW co-design. The largest gain of OOD here is the ability to abstract the SW/HW integration process in an implementation-independent way. Hence, the interfacing gap can be automatized at certain level by some correct-by-construction and automatic generation techniques. This is important seeing that closing SW/HW gap remains always a complex, time-consuming, error-prone and less-contributive task.

Last but not least, we want to position the proposed design approaches on the context of edgecentric computing where the target system becomes much more complicated with a network of hybrid SW/HW nodes connected together. This forms a complex distributed environment and rises the question of how to efficiently manage, develop, deploy and maintain such system. A manual solution is not an option considering the network scale of the system. In this case, while the processing is decentralized (distributed), the development (both SW and HW), should be centralized to facilitate the management and maintenance. The deployment should be automatized to be able to handle a large scale of nodes. Such dedicated edge-centric environment is still missing in our perspective.

#### 1.2.2 Contributions

The research towards this thesis has been partly included in the following publications (papers or poster, chronological order):

- 1. Xuan Sang LE, Loïc Lagadec, Luc Fabresse, Jannik Laval, and Noury Bouraqadi. From Smalltalk to Silicon: Towards a methodology to turn Smalltalk code into FPGA. In *IWST 14*, Cambridge, United Kingdom, August 2014

- Xuan Sang LE, Loïc Lagadec, Luc Fabresse, Jannik Laval, and Noury Bouraqadi. A meta model supporting both hardware and smalltalk-based execution of fpga circuits. *IWST '15*, pages 6:1–6:14, 2015. IWST best paper award

- 3. Xuan Sang LE, Luc Fabresse, Jannik Laval, Jean-Christophe Le Lann, Loïc Lagadec, and Noury Bouraqadi. Dynamic distributed programming on reconfigurable ip-based smart sensor networks. Presented as poster at 11ème Colloque du GDR SoC-SiP, France, 2016

- 4. Xuan Sang LE, Luc Fabresse, Jannik Laval, Jean-Christophe Le Lann, Loïc Lagadec, and Noury Bouraqadi. Speeding Up Robot Control Software Through Seamless Integration With FPGA. In SHARC '16: 11th National Conference on Software and Hardware Architectures for Robots Control, Brest, France, 2016

- Xuan Sang LE, Jean-Christophe Le Lann, Loïc Lagadec, Luc Fabresse, Noury Bouraqadi, and Jannik Laval. Cardin: An agile environment for edge computing on reconfigurable sensor networks. In the proceedings of The 2016 International Conference on Computational Science and Computational Intelligence (CSCI'16), Las Vegas, Nevada, USA, 2016

The contribution presented in this thesis are designed and developed by the author. The software environment used for modeling and middleware, toolset building is based on Pharo Smalltalk [DZHC17] – an elegant object oriented language and environment. The research carried out for this thesis resulted in the following contributions (listed in the order they appear in this thesis):

- Conceptual meta-model –baptized OoRC– that brings OOD concepts and principles to hardware design. The meta-model support modeling hardware system at two levels of granularity:

fine-grained level where it is used to specify FPGA circuits at RTL level;

coarse-grained level where OOD principles and design patterns are employed to abstract and modularize the hardware system.

- 2. Dedicated design environment (middleware and toolset) for SW/HW integration which is based on the OOD and platform-based design approaches. The essential is to close the SW/HW gap by abstracting the communication and provide automatic implementation (generation) of the interface (both SW and HW) depending on the application context.

Hardware architecture, middleware and toolset for edge-centric application development. The philosophy here is to (1) centralize the development of distributed (decentralized) application, (2) automatize the application deployment and (3) abstract the network communications.

OOD is the main design methodology employed throughout these contributions to produce a unique design environment and flow. It is used in conjunction with (1) Model-Driven Engineering (MDE) to model hardware system, (2) platform-based design for SW/HW co-design and (3) distributed programming to provide environment for distributed application development and deployment on the network.

#### 1.3 Outline of the Thesis

Chapter 2 presents the state of the art of our research which covers the following domains: edgecomputing, hardware design, and HW/SW co-design. Chapter 3 describes our OoRC meta-model at conceptual level. Both RTL-level modeling and system-level modeling are addressed. The chapter also describes how the meta-model handles the reuse of VHDL legacy IPs as regular object oriented models. Chapter 4 targets the SW/HW co-design problem with OoRCBridge, middleware and toolset dedicated for integrating FPGA devices in existing high-level software system. Concretely, the SW/HW communication is standardized, a mechanism for automatic interface generation is specified and an API for abstracting HW accessing is also provided. Chapter 5 puts it all together in the context of edgecomputing. We present our dedicated distributed environment named CaRDIN. It has been developed for application building and deploying on such hybrid system. Finally, in chapter 6, conclusions are drawn and future work related to the OoRC meta-model and CaRDIN are discussed. "Creativity is thinking up new things. Innovation is doing new things."

Theodore Levitt

## 2 State of the Art

#### Contents

| 2.1 | omputing | 10                                                  |    |

|-----|----------|-----------------------------------------------------|----|

|     | 2.1.1    | Dedicated SN for Edge Computing                     | 10 |

|     | 2.1.2    | Using FPGAs for Edge Computing in IoT               | 11 |

|     | 2.1.3    | Discussion                                          | 11 |

| 2.2 | Hardwa   | are Design Background                               | 12 |

|     | 2.2.1    | Overview                                            | 12 |

|     | 2.2.2    | Hardware Design Methodologies                       | 12 |

|     | 2.2.3    | Discussion                                          | 13 |

| 2.3 | Meta-m   | nodeling for System-level Hardware Design Using MDE | 14 |

|     | 2.3.1    | Model-Driven Engineering                            | 14 |

|     | 2.3.2    | Component-based approaches                          | 16 |

|     | 2.3.3    | Platform-based approaches                           | 18 |

|     | 2.3.4    | UML and Object Oriented based Approaches            | 20 |

|     | 2.3.5    | Summary                                             | 22 |

| 2.4 | Softwa   | re/Hardware Co-design                               | 24 |

|     | 2.4.1    | Early Binding Approaches                            | 24 |

|     | 2.4.2    | Late Binding Approach                               | 26 |

|     | 2.4.3    | Discussion                                          | 27 |

| 2.5 | Position | ing our work                                        | 27 |

This chapter covers an examination of existing research in the field of embedded system design methodologies and application of FPGA-based device in IoT and edge-centric computing. The first section enlightens the current use of SN and FPGA in the edge computing domain. We then analyze the hardware design gap by comparing different existing hardware design methodologies. Hardware/software co-design is another related important research field which will be discussed at the end of the chapter.

#### 2.1 Edge Computing

#### 2.1.1 Dedicated SN for Edge Computing

Edge centric architecture consists of a data center at the core surrounded by capable nodes with small web server constituting a content distribution network. Sensor Networks compliant with Internet protocol (IP) are good candidates for building such architecture. Unfortunately, most SNs solutions are non-IP-compatible SNs, thus have difficulty to participate to internet (missing of IP stack). In the context of EC, the integration of such SN to IP-based network requires the deployment of an extra layer at the edge of the two networks to link non-IP SN communications with internet communications [GRL+08, KBLK07]. Proposed approaches are focused on wrapping data coming from sensor sources for sharing and processing over the Internet. Those works provide heterogeneity out of SN. Communication and application-level code needs to be hand-programmed for each node. Recently, a new research trend has emerged in this area: the IP-based sensor networks, [PKGZ08, D<sup>+</sup>09], that offers a more natural and direct way to bring SN to the internet. These approaches assume that sensor nodes are powerful enough to implements an IP stack. The web services can be used on top of these systems and offer the compatibility between SN and standard IoT infrastructures. These works show an important advance in the area. They, however, provide only the infrastructure without further software API for the operations and interactions of the node.

Middleware plays a crucial role in SN, it defines an application platform that: (1) can be deployed in various application scenarios; (2) can handle the heterogeneous and distributed nature of the network and (3) promotes the integrability of the system. Diverse middleware solutions have been proposed for SN. Some approaches such as [YG02, MFHH05] consider the SN as a *virtual database* that can be queried through an SQL-like language. Others rely on *Mobile agent* approach in which applications are modular and each module can be distributed through the network [BHSS07, ORRM09]. The works in [MAK07, SCC<sup>+</sup>06] propose a *Virtual Machine* approach which is more general than Mobile Agents. They allow arbitrary code to run on sensor nodes and make the software independent from the hardware architecture. *Message oriented middleware* [KS09, CCD<sup>+</sup>09] is another possible solution for communication inside SN. These approach support sending and receiving messages between distributed systems via an event-driven mechanism (publish/subscribe service). These middle-wares could be a standalone architecture that runs directly on bare-metal hardware or could be built on top of an OS – such as TinyOS [LMP<sup>+</sup>05]– dedicated for sensor network. All of these middleware are used mainly for querying raw sensor data rather than support the development and deployment of complex applications on the nodes.

#### 2.1.2 Using FPGAs for Edge Computing in IoT

Since the application of FPGAs for Edge Computing is a brand new topic, the state of the art is still limited in the context of IoT. However, we can consider the use of FPGA on SN as references, seeing that SN is the base of IoT and Edge Computing. Many researchers have explored the benefit of parallel processing and hardware reconfiguration in FPGA for prototyping sensor networks. Some approaches use only FPGA with [MR08, CSM08] or without [LSKT13, HRVG08] soft-core processor (e.g. NIOS) to build the sensor nodes. Those enable the flexible adaptation of hardware changes on sensor nodes, but do not offer the flexible reconfiguration that software approaches do, nor do they support remote reconfiguration of the node. Since the system is entirely implemented in FPGA, the software capacity of these nodes is limited that lead to the missing of an efficient middleware. Other works such as [Ber12, KPC<sup>+</sup>08, PRDC] address to these problems by proposing a non IP-based approach with an entire workflow to generate, remotely configure and reconfigure the FPGA. Theses work use a micro-controller ( $\mu$ C) to reconfigure the FPGA. Both software ( $\mu$ C) and hardware (FPGA) can be reprogrammed/reconfigured remotely from host via a wireless link (e.g. ZigBee).However, the use of  $\mu$ C still limits the software capability of the node. The development is entirely baremetal ( $\mu$ C/FPGA) which is specific and limits the reusability of the system. All of these approaches are non IP-based and are not compatible with an internet and edge-centric usage. Firstly, to support IoT, the IP-stack (and web services) must be implemented on µC or on FPGA which requires specific skills. Secondly, they are designed only for sensor data acquisition and thus are not suitable for edge-centric applications.

#### 2.1.3 Discussion

Current proposed SN architectures are based on the cloud-computing model, where all sensor data are centralized and processed in a sole place. Sensor nodes are often simple devices with limited software capabilities and used for data acquisition and transmission. This results a very simple communication-based middleware. When passing to an edge computing model, these architectures and middlewares need to be revised. The IP protocol should be the base protocol for network communication. By reinforcing the edge of the network, edge-centric nodes are more powerful. This requires a new generation of middleware to be able to (1) efficiently exploit the hardware capability of the nodes, (2) provide a rich set SW features for building complex application.

FPGAs show interesting application in edge computing since they offer parallel and realtime processing ability to the node with a reasonable energy budget. However, current uses of FPGAs on SN come up with pure hardware nodes that have limited SW capability and thus are unsuitable for EC. EC requires nodes with (1) rich SW features, (2) flexible middleware for nodes communication and interaction and (3) real-time data processing capability. Hybrid FPGA devices consisting of an FPGA coupled with embedded processor are therefore good candidates. The processor greatly simplifies the implementation of an IP-based software stack and associated web services as well as provides enough performance for an edge-centric middleware. The FPGA is dedicated to critical and real-time data processing tasks.

**Figure 2.1:** Hardware design productivity gap: number of transistors available on a chip vs. the ability for the transistors to be used efficiently in a design [int11, Sed06]

#### 2.2 Hardware Design Background

#### 2.2.1 Overview

Basically, a good system design methodology should consider following important criteria: (1) Time-tomarket (design time), (2) Productivity (production outputs/inputs ratio), (3) Maintainability (repair/replace, flexible to change, easy to maintenance, etc.), (4) Extensibility (adding new capability) and (5) Reusability (reuse with less modification possible). A flexible and generic solution for software/hardware integration involves SW/HW co-design. Software design has shown an important evolution with Oriented Object Design and Design Pattern. These design methodologies have been well proven on real world projects. They are claimed to be the best methodologies to satisfy the presented criteria. In [LHKS91], authors have shown that object-oriented paradigm can improve productivity of software design by about 50% (1.5 times). Hardware design, however, alway remains a long and tedious process. According to More's Law, the complexity of hardware system in terms of logic transistors integrated on a chip increases about 58% per year. Nevertheless, the hardware design productivity increases around 21% per year [int11]. In Electronic Design Automation (EDA) community, this rate is known as *design productivity gap* (figure 2.1) which results in inflating design costs. Most current research efforts on hardware design are aimed at closing this gap by rising the abstraction level and increase IP (Intellectual Property) reuse.

#### 2.2.2 Hardware Design Methodologies

The traditional and commonly used languages for hardware design is Hardware Description Languages (HDL), such as VHDL or Verilog. These languages allow to describe IP (Intellectual Property) cores at Register Transfer Level (RTL). For decades, the main concern of hardware designer is to create an efficient component (e.g. speed, area or power usage) using these languages. They focus on the creation and qualification of IP content for a specific application regardless of its further reusability in the application domain. This can cause a redundancy of similar IPs designed for different applications depending on different requirements. This design habit is called *content-based* design [DSO4]. It is worth noting that reuse does not necessarily apply only to circuits (content), but can also be applied

to concepts and techniques. Hardware designers are using methodologies (concepts + techniques) that are several years behind software. Traditional HW design methods and HDLs are not equipped with modern design features –such as object oriented– and thus limit the reusability, extendability and maintainability of existing IPs.

The increased complexity of hardware system requires more productive methodologies. Currently, to gain productivity, modern hardware design seeks to rise the design abstraction level. Literally, there are mainly two directions of abstraction: content-level abstraction and system-level abstraction.