# ALGORITHMIC TECHNIQUES FOR THE MICRON AUTOMATA PROCESSOR

A Thesis Presented to The Academic Faculty

by

Indranil Roy

In Partial Fulfillment

of the Requirements for the Degree

Doctor of Philosophy in the

School of Computational Science and Engineering

Georgia Institute of Technology August 2015

Copyright © 2015 by Indranil Roy

# ALGORITHMIC TECHNIQUES FOR THE MICRON AUTOMATA PROCESSOR

## Approved by:

Professor Srinivas Aluru, Advisor School of Computational Science and Engineering Georgia Institute of Technology

Professor Alberto Apostolico School of Computational Science and Engineering Georgia Institute of Technology

Professor Sudhakar Yalamanchili School of Computational Science and Engineering Georgia Institute of Technology Professor David A. Bader School of Computational Science and Engineering Georgia Institute of Technology

Professor Richard Vuduc

The School of Electrical and Computer

Engineering

Georgia Institute of Technology

Date Approved: 24 April 2015

To my family, loved ones and friends.

## **PREFACE**

This dissertation is the first in-depth study on the use of the Micron Automata Processor, a novel re-configurable co-processor that supports direct hardware implementation of a set of non-deterministic finite automata over a streaming input. This study is made interesting by the fact that this co-processor will be the only commercially available processor which is directly based on the Multiple Instruction Single Data architecture. This allows it to efficiently handle a class of applications which are inherently difficult to compute using existing processors.

By design, this processor is well-suited to accelerate applications which need to find all occurrences of thousands of complex string-patterns in the input data. This document details our research to implement such applications on this processor and evaluate the performance benefits. We have also significantly widened the scope of the applications which can be accelerated through this processor by finding ways to solve some classic graph problems such as finding maximal cliques and Hamiltonian cycle/paths in a graph, and problems which can be reduced to those graph problems, such as the boolean satisfiability (SAT) problem. We have outlined various strengths and weaknesses of the processor, and describes techniques to estimate performance. These algorithmic and estimation techniques are already being used by other researchers to provide solutions to a wide variety of problems such as *Brill tagging* and *Association Rule Mining*.

This processor has been in the making for the past eight to nine years. Our research group was the first outside the company, that the developers reached out to for application development in 2011. Subsequently, two other academic groups joined later. The processor was unveiled to the world in November 2013, at the *Supercomputing* conference. Since then, many other researchers have joined the effort through the *Center for Automata*

## Processing.

Initially, the aim of our group was to accelerate problems in string pattern matching from the field of bioinformatics. We started with accelerating the search for known string patterns called *motifs* in protein sequences and extended it to accelerate the discovery of unknown motifs in biological sequences, a known *NP*-complete problem.

While coming up with a solution for the latter, it became evident that this processor can be used to solve various problems on unweighted graphs. However, the following transformations are imperative for solving graph problems on the Automata Processor. First, the nodes and edges in the graph must be represented using strings which can be streamed to the co-processor. Second, the graph problem must be converted into a string-pattern matching problem which can be evaluated using automata over the streaming data. We developed algorithmic techniques to represent nodes and edges of any generic graph using strings, and create efficient automata which can be used to solve a variety of graph problems including finding cliques, Hamiltonian path and cycles, connected components, and single-source shortest paths; and other problems like boolean satisfiability which can be reduced to graph problems. These techniques are detailed in this dissertation.

It is hoped that the the advent of this processor will galvanize the field of automatabased applications by providing a means to support their implementation in hardware. Towards that end, this dissertation contributes many algorithmic techniques and automatadesign strategies which can be used to develop applications which run efficiently on this new processor.

## **ACKNOWLEDGEMENTS**

I would like to take this opportunity to express my sincerest gratitude to those who contributed towards the completion of this thesis.

First and foremost, I thank my principal advisor Dr. Srinivas Aluru. His guidance, patience and support throughout my doctoral studies has been exemplary. Without him this dissertation would not have been possible.

I am also grateful to Dr. David A. Bader, Dr. Professor Alberto Apostolico, Dr. Professor Richard Vuduc, and Dr. Sudhakar Yalamanchili for their valuable time and suggestions. Their varied experience and in depth knowledge has often provided guiding light and provided validation to the research that I conducted.

I will forever be indebted to my parents. Their sacrifices in getting me here are momentous. I must also thank my roommates Yuzhu and Rahul for being with me through thick and thin over the past few years. They have developed mutual respect for each other solely on the capability of tolerating me. Besides them, I owe gratitude to my delightful labmates, with whom I passed the best part of most days. They have made my workload considerably lighter.

Finally, I would like to thank Paul Dlugosch, Paul Glendenning and Michael Leventhal from Micron Technology, Inc. for various collaborations which were required to bring this work to fruition.

## **Contents**

| DE  | DICA             | TION           |                                     | ii |  |  |

|-----|------------------|----------------|-------------------------------------|----|--|--|

| PR  | EFAC             | <b>EE</b>      |                                     | V  |  |  |

| AC  | ACKNOWLEDGEMENTS |                |                                     |    |  |  |

| LIS |                  |                |                                     |    |  |  |

| LIS | т оғ             | F <b>IGU</b> I | RES                                 | ij |  |  |

| SU  | MMA              | RY .           |                                     | V  |  |  |

| I   | INT              | RODU           | CTION                               | 1  |  |  |

| II  |                  |                | AUTOMATA PROCESSOR                  |    |  |  |

|     | 2.1              |                | mming Model                         |    |  |  |

|     |                  | 2.1.1          | Configuration Stage                 |    |  |  |

|     |                  | 2.1.2          | Execution Stage                     |    |  |  |

|     |                  | 2.1.3          | Automata Elements                   | 0  |  |  |

|     | 2.2              | Progra         | amming Resources                    | 3  |  |  |

| Ш   | GEN              | NERAT          | ING EFFICIENT ANML-AUTOMATA         | 5  |  |  |

|     | 3.1              | Transl         | ating classical NFAs to ANML-NFAs   | 5  |  |  |

|     |                  | 3.1.1          | Handling $\varepsilon$ -transitions | 6  |  |  |

|     |                  | 3.1.2          | Removing Redundancies in ANML-NFA   | 7  |  |  |

|     | 3.2              | Count          | er Elements                         | 0  |  |  |

|     | 3.3              | Boolea         | an Elements                         | 3  |  |  |

|     |                  | 3.3.1          | Group-of-Two (GoT)                  | 3  |  |  |

|     | 3.4              | Handli         | ing Look-ahead Assertions           | 5  |  |  |

|     |                  | 3.4.1          | Example 1                           | 6  |  |  |

|     |                  | 3.4.2          | Example 2                           | 7  |  |  |

|     | 3.5              | Going          | Beyond Regular Languages            | 7  |  |  |

|     |                  | 3.5.1          | Example 3                           | 8  |  |  |

|              |     | 3.5.2   | Example 4                                                 | 29 |

|--------------|-----|---------|-----------------------------------------------------------|----|

|              | 3.6 | Applic  | eation Developers Notes                                   | 29 |

|              |     | 3.6.1   | Minimizing Reconfiguration Time                           | 30 |

|              |     | 3.6.2   | Avoiding Stalls to Handle Output                          | 31 |

|              |     | 3.6.3   | Maximizing Resource Utilization                           | 32 |

|              | 3.7 | Summ    | ary                                                       | 33 |

| IV           | HIG | H PER   | FORMANCE PATTERN MATCHING                                 | 34 |

|              | 4.1 | Fast-S  | NAP                                                       | 35 |

|              |     | 4.1.1   | Background                                                | 36 |

|              |     | 4.1.2   | Snort Rules                                               | 37 |

|              |     | 4.1.3   | Methodology                                               | 39 |

|              | 4.2 | Proton  | nata                                                      | 42 |

|              |     | 4.2.1   | Background                                                | 43 |

|              |     | 4.2.2   | Methodology                                               | 45 |

|              | 4.3 | Perfori | mance Evaluation                                          | 51 |

|              |     | 4.3.1   | Estimation model                                          | 52 |

|              |     | 4.3.2   | Snort                                                     | 52 |

|              |     | 4.3.3   | PROTOMATA                                                 | 54 |

|              | 4.4 | Summ    | ary                                                       | 57 |

| $\mathbf{V}$ | FIN | DING I  | DE-NOVO PATTERNS IN BIOLOGICAL SEQUENCES                  | 58 |

|              | 5.1 | Backg   | round                                                     | 58 |

|              | 5.2 | Design  | of Building Blocks for Motif Search on Automata Processor | 60 |

|              |     | 5.2.1   | Bounded Mismatch Identification Automaton                 | 60 |

|              | 5.3 | Overvi  | iew of Proposed Algorithm                                 | 61 |

|              | 5.4 | Findin  | g Cliques in Multipartite Sequence Graph                  | 63 |

|              |     | 5.4.1   | Overview of the Proposed Algorithm                        | 63 |

|              |     | 5.4.2   | Pruning the Clique Search Space                           | 64 |

|              |     | 543     | Clique Management and Pruning the Node Search Space       | 6/ |

|     |            | 5.4.4                                                          | Clique Finding using Automata Processor                                                  | 65                                 |

|-----|------------|----------------------------------------------------------------|------------------------------------------------------------------------------------------|------------------------------------|

|     |            | 5.4.5                                                          | Automata Processor Implementation Details                                                | 67                                 |

|     |            | 5.4.6                                                          | qPMP solution                                                                            | 69                                 |

|     | 5.5        | Search                                                         | ing for Motifs Consistent With Cliques                                                   | 69                                 |

|     |            | 5.5.1                                                          | Arranging Candidate Motifs as Search Trees                                               | 70                                 |

|     |            | 5.5.2                                                          | Handling Large Search Trees                                                              | 71                                 |

|     |            | 5.5.3                                                          | Overview of the Proposed Algorithm                                                       | 72                                 |

|     |            | 5.5.4                                                          | Filtering candidate motifs With Less Than <b>d</b> Mismatches With At Least One Sequence | 74                                 |

|     |            | 5.5.5                                                          | Phase 2: Identifying Actual Motifs from Eligible Candidates                              | 79                                 |

|     | 5.6        | Perform                                                        | mance Estimation                                                                         | 85                                 |

|     |            | 5.6.1                                                          | Established run-time Features of the Automata Processor                                  | 86                                 |

|     |            | 5.6.2                                                          | Execution Time for Finding <b>n</b> -cliques                                             | 86                                 |

|     |            | 5.6.3                                                          | Execution Time for Motif Discovery from Cliques                                          | 88                                 |

|     | 5.7        | Summa                                                          | ary                                                                                      | 89                                 |

| VI  | SOL        | VING (                                                         | GRAPH PROBLEMS - I                                                                       | 90                                 |

|     | 6.1        | Backgr                                                         | ound                                                                                     | 90                                 |

|     |            | 6.1.1                                                          | Boolean Satisfiability (SAT) Problem                                                     | 91                                 |

|     |            |                                                                |                                                                                          |                                    |

|     |            | 6.1.2                                                          | Modified Requirement Specification                                                       | 93                                 |

|     |            | <ul><li>6.1.2</li><li>6.1.3</li></ul>                          | Modified Requirement Specification                                                       |                                    |

|     | 6.2        | 6.1.3                                                          | •                                                                                        | 95                                 |

|     | 6.2        | 6.1.3                                                          | Overview of Changes                                                                      | 95<br>95                           |

|     | 6.2        | 6.1.3<br>Method                                                | Overview of Changes                                                                      | 95<br>95<br>96                     |

|     | 6.2        | 6.1.3<br>Method                                                | Overview of Changes                                                                      | 95<br>95<br>96<br>96               |

|     | 6.2        | 6.1.3<br>Method<br>6.2.1<br>6.2.2<br>6.2.3                     | Overview of Changes                                                                      | 95<br>95<br>96<br>96               |

|     |            | 6.1.3<br>Method<br>6.2.1<br>6.2.2<br>6.2.3<br>Perform          | Overview of Changes                                                                      | 95<br>95<br>96<br>96<br>99         |

| VII | 6.3<br>6.4 | 6.1.3<br>Method<br>6.2.1<br>6.2.2<br>6.2.3<br>Perform          | Overview of Changes                                                                      | 95<br>96<br>96<br>99<br>100        |

| VII | 6.3<br>6.4 | 6.1.3<br>Method<br>6.2.1<br>6.2.2<br>6.2.3<br>Perform<br>Summa | Overview of Changes                                                                      | 95<br>96<br>96<br>99<br>100<br>101 |

|            | 7.1.2  | Automata Design                     | . 103 |

|------------|--------|-------------------------------------|-------|

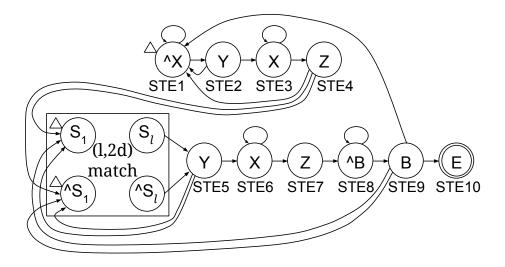

| 7.2        | Findin | g Acyclic Paths in Graphs           | . 105 |

|            | 7.2.1  | Overview Of The Algorithm           | . 106 |

|            | 7.2.2  | Basic Path Extension Edge Automaton | . 106 |

|            | 7.2.3  | Path Extension Edge Automata        | . 108 |

|            | 7.2.4  | Applications                        | . 111 |

|            | 7.2.5  | Heuristics For Pruning Search Space | . 112 |

|            | 7.2.6  | Job Partitioning                    | . 112 |

|            | 7.2.7  | Estimating Speed-up                 | . 113 |

|            | 7.2.8  | Additional Improvements             | . 113 |

| 7.3        | Buildi | ng Shortest Path Trees in Graphs    | . 115 |

|            | 7.3.1  | Overview Of The Algorithm           | . 116 |

|            | 7.3.2  | Basic Edge Macro                    | . 117 |

|            | 7.3.3  | Applications                        | . 120 |

|            | 7.3.4  | Future directions                   | . 122 |

| 7.4        | Summ   | ary                                 | . 123 |

| VIII CON   | NCLUS  | ION                                 | . 128 |

| 8.1        | Challe | enges                               | . 128 |

| 8.2        | Achiev | vements                             | . 131 |

| 8.3        | Scope  | For Future Research                 | . 132 |

| Appendi    | x A -  | — BOUNDED MISMATCH COUNT AUTOMATON  | . 135 |

| • •        |        |                                     |       |

| XITA       | MULO   |                                     | 144   |

| X/ I' I 'A |        |                                     | 1/1/1 |

## **List of Tables**

| 1 | Comparison of run-times from <i>ps_scan</i> and PROTOMATA    | <br>55 |

|---|--------------------------------------------------------------|--------|

| 2 | Estimated and actual run-times of various stages of Motomata | <br>87 |

# **List of Figures**

| 1  | Example 1: State-diagram                                                | 11 |

|----|-------------------------------------------------------------------------|----|

| 2  | Example 1: Equivalent ANML NFA                                          | 11 |

| 3  | Hierarchical layout of processing elements in an AP chip                | 13 |

| 4  | Example 1: Revisited                                                    | 16 |

| 5  | Example 2: State-diagram with $\varepsilon$ -transitions                | 17 |

| 6  | Example 2: Equivalent ANML-NFA                                          | 17 |

| 7  | Example 3: ANML-NFA with <i>all-input-start</i> STE                     | 18 |

| 8  | Example 1: Optimized ANML-NFA                                           | 19 |

| 9  | ANML-NFA without any counter-element to accept exactly 50 repetitions . | 20 |

| 10 | ANML-NFA with counter-element to accept exactly 50 repetitions          | 21 |

| 11 | ANML-NFA to accept repetitions above a minimum threshold                | 22 |

| 12 | ANML-NFA to accept repetitions within a range                           | 23 |

| 13 | Group of Two (GoT) STEs                                                 | 23 |

| 14 | Latched-STE using a GoT                                                 | 24 |

| 15 | Using the <i>select</i> and <i>enable</i> lines of the GoT              | 25 |

| 16 | Handling look-ahead assertions using a boolean AND element              | 26 |

| 17 | Difference beteen ANML and PCRE lookaheads                              | 27 |

| 18 | Expressing non-regular languages using ANML: Example 1                  | 28 |

| 19 | Expressing non-regular languages using ANML: Example 2                  | 29 |

| 20 | Using a GoT to regulate output generation                               | 32 |

| 21 | ANML-NFA for a SNORT rule with 3 lookaheads                             | 41 |

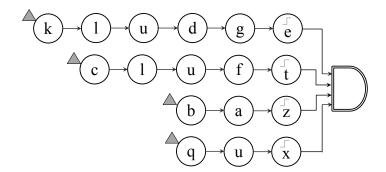

| 22 | Occurrence of the PROSITE motif                                         | 45 |

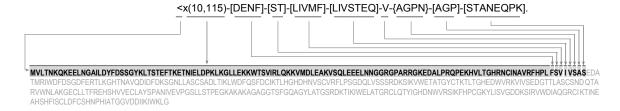

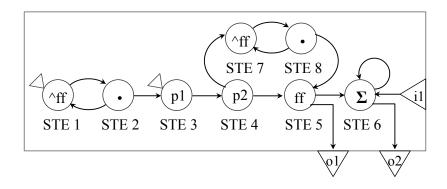

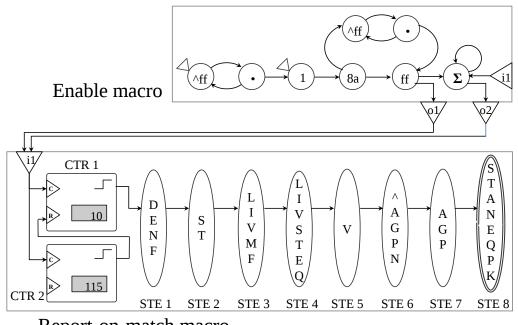

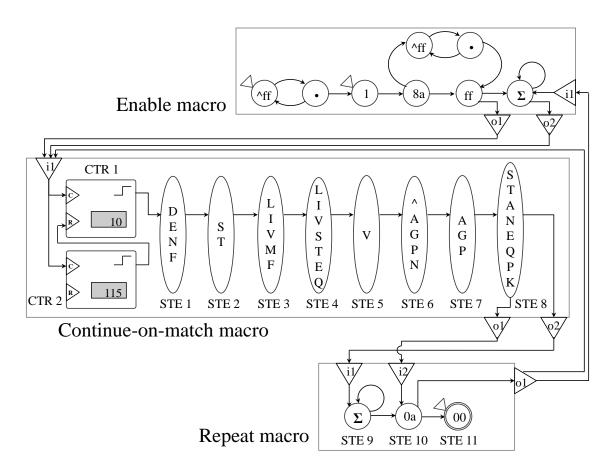

| 23 | The Enable macro                                                        | 48 |

| 24 | The <i>Locate-occurrence</i> automaton                                  | 50 |

| 25 | The Global-match automaton                                              | 51 |

| 26 | The Bounded Mismatch Identification automaton                           | 60 |

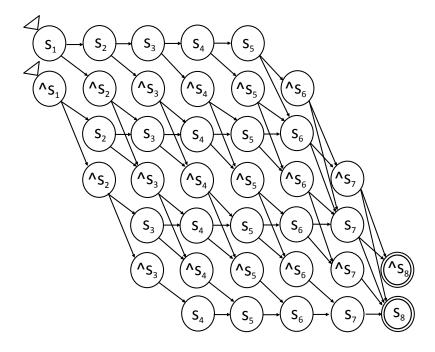

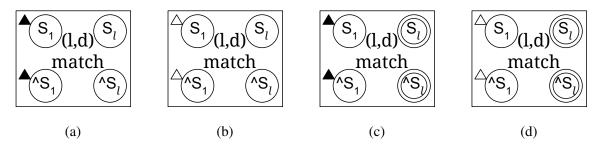

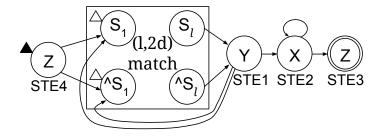

| 27 | Shorthand representations of the $(l,d)$ match automaton                | 61 |

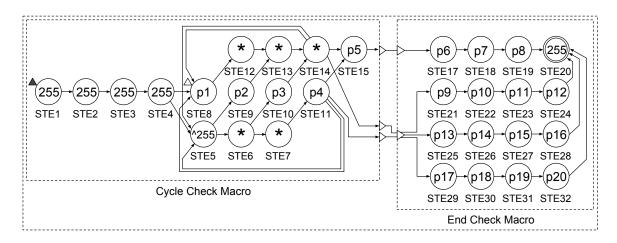

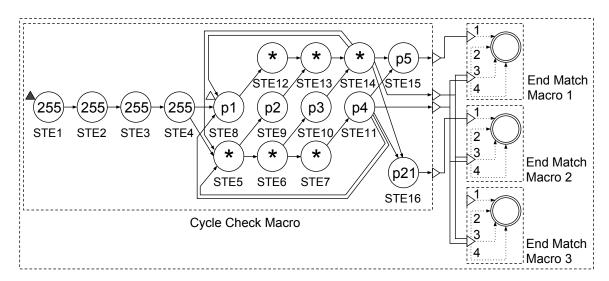

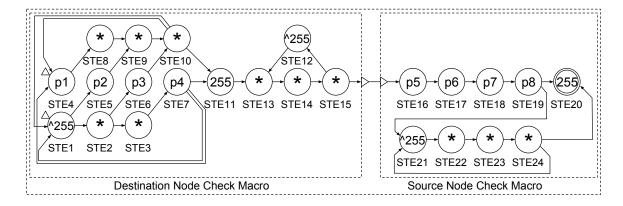

| 28 | Automaton to check if node is a neighbor of every bucket 68 |

|----|-------------------------------------------------------------|

| 29 | Automata to identify neighboring cliques of a node 69       |

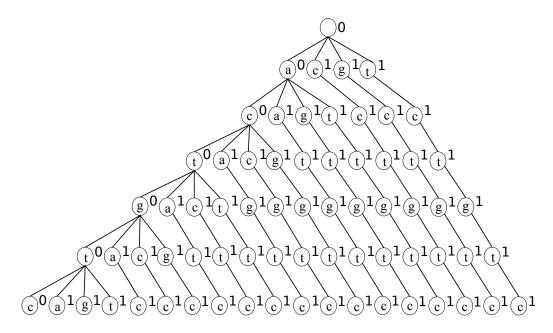

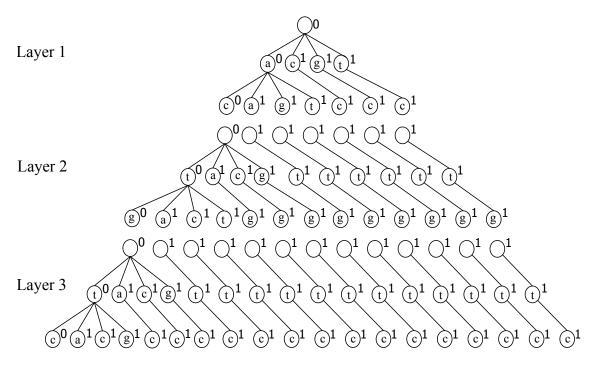

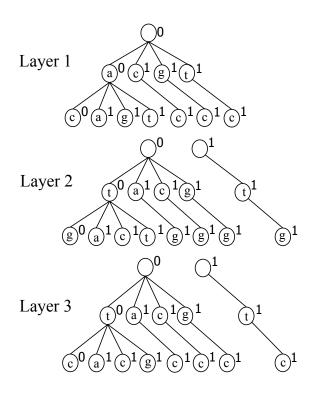

| 30 | Search tree for $S = actgtc$ with up to one mismatch        |

| 31 | Search tree partitioned into multiple layers                |

| 32 | Unique subtrees in each layer of the search tree            |

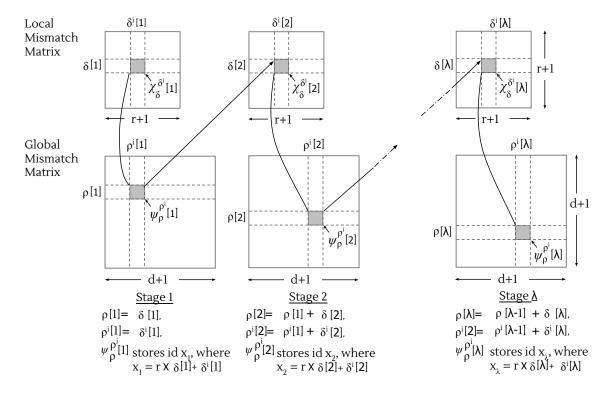

| 33 | Local Mismatch Matrix and Global Mismatch Matrix            |

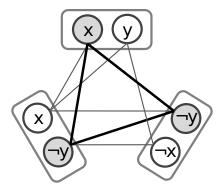

| 34 | Reduction of boolean SAT problem to a graph problem         |

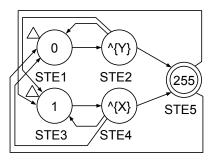

| 35 | Clique-automaton                                            |

| 36 | Clique macro                                                |

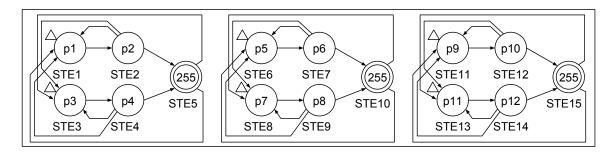

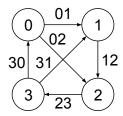

| 37 | String labels of nodes and edges in a graph                 |

| 38 | Finding Hamiltonian paths starting at node 0                |

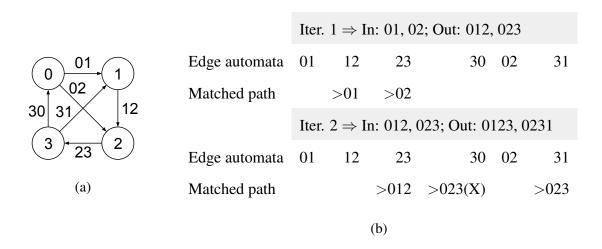

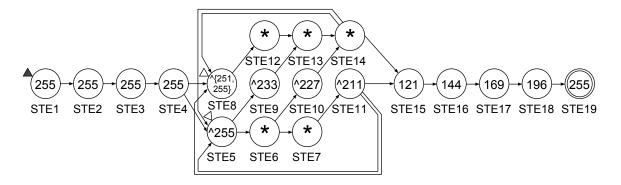

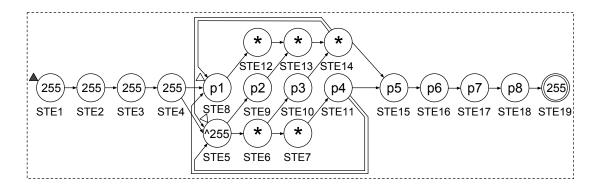

| 39 | Basic Path Extension Edge Automaton                         |

| 40 | Basic edge macro for extending acyclic paths                |

| 41 | Path extension multiple edge macro                          |

| 42 | Extended path extension multiple edge macro                 |

| 43 | Basic tree extension edge macro                             |

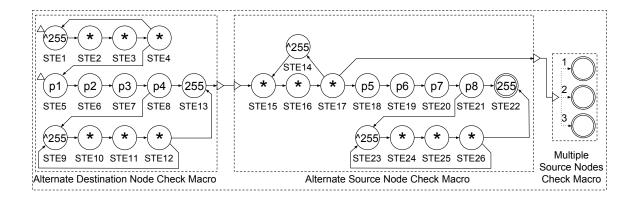

| 44 | Alternate basic tree extension edge macro                   |

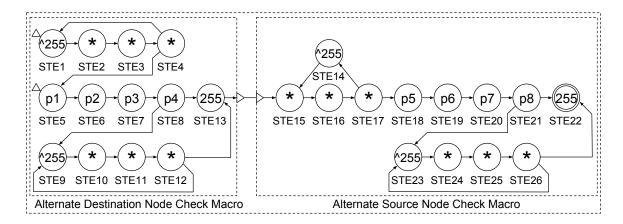

| 45 | Tree extension multiple edge macro                          |

| 46 | Alternate tree extension multiple edge macro                |

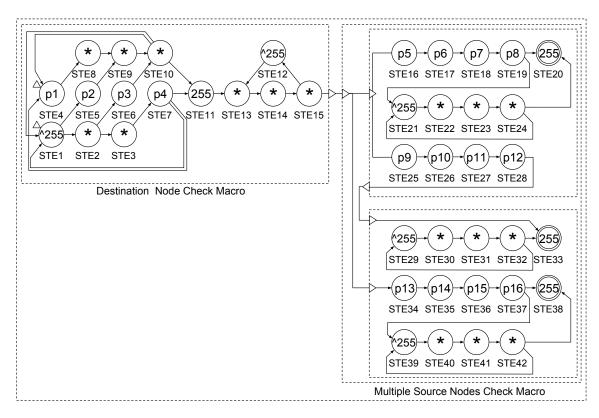

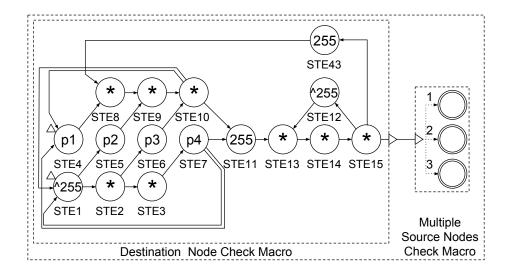

| 47 | Modified tree extension multiple edge macro                 |

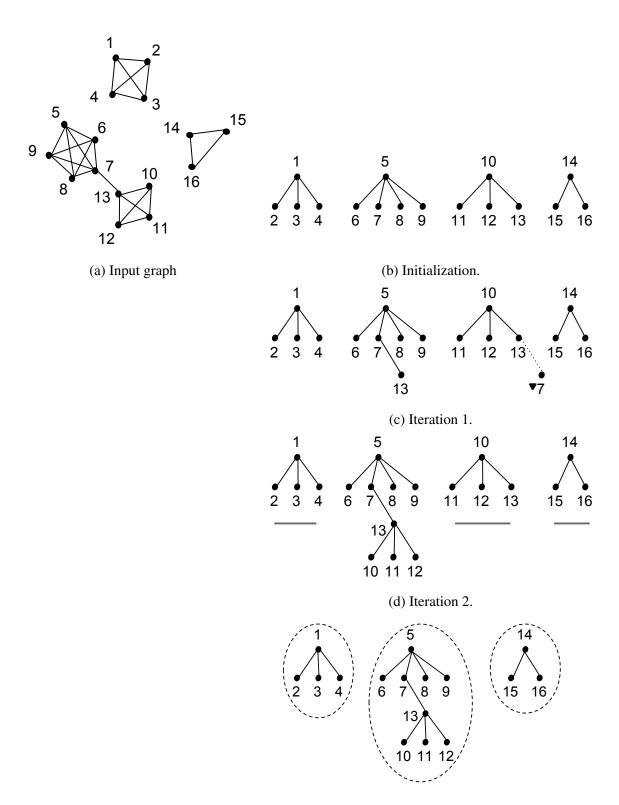

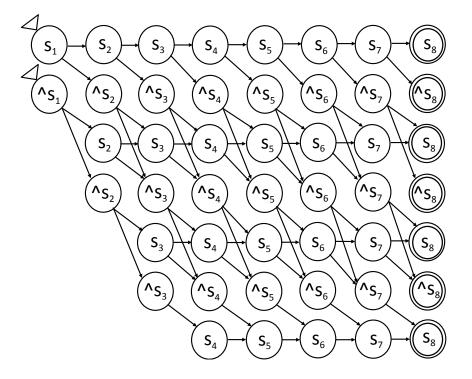

| 48 | Finding all connected components in a graph                 |

| 49 | Bounded Mismatch Count Automaton 136                        |

## SUMMARY

Our research is the first in-depth study in the use of the Micron Automata Processor, a novel re-configurable streaming co-processor which is designed to execute thousands of Non-deterministic Finite Automata (NFA) in parallel. By design, this processor is well-suited to accelerate applications which need to find all occurrences of thousands of complex string-patterns in the input data. We have validated this by implementing two such applications, one from the domain of network security and the other from the domain of bioinformatics. Both these applications are significantly faster than their state-of-art counterparts based on existing accelerators. Our research has also widened the scope of the applications that can be handled using this processor by designing algorithms to solve graph problems. In order to make this possible, we developed fundamental techniques to represent nodes and edges in the graph using strings, and convert the graph problem into a string-pattern matching problem. Subsequently, we created efficient automata which identify the patterns representing output graph structures like maximal-cliques, connected components, Hamiltonian paths, Hamiltonian cycles, etc. These techniques have been used in applications such as discovery of new *motifs* in biological sequences, and solving challenging instances of the boolean satisfiability problem. These applications and algorithms have not only guided other developers who joined the program later, but also yielded valuable feedback and design-inputs for the next generation of the chip which is currently in the design phase. We hope that this work paves the way for the early adoption of this upcoming architecture and continues to aid in the development of efficient solutions to some of the problems which are currently computationally challenging.

## Chapter I

## INTRODUCTION

The capability to perform complex and numerous pattern-matching operations in parallel is commonly found in nature. For example, it lies at the basis of natural language processing, object recognition and analytical skills required to compose and understand the text and diagrams in this document. Even insects and animals use pattern-matching subconsciously to search for food, hunt, identify threats etc. However, our current computers are not adept at this kind of computing. This is partially because of the rarity of processors based on the Multiple Instruction Single Data (MISD) architecture, necessary to perform multiple pattern matching operations on a single input data in parallel. In fact, barring the *systolic arrays*, whose classification as MISD is questionable, there are no known commercially available processors for this basic classification of processors described in Flynn's taxonomy [30].

The most challenging part of building high performance MISD machines is to provide routing capability to stream the same data to thousands of processing units operating in parallel. Hardware implementations have been proposed since 1982 [29]. However, not much has come to fruition till date. Most recent efforts [75, 11, 54, 74, 72] concentrate on the utilization of high-performance reconfigurable Field-Programmable Gate Array (FPGA) processors to implement parallel pattern-recognition engines in hardware. However limitations still remain in these implementations. In [25], the authors have provided an extensive review of the related literature and categorized these limitations on ten key criteria, the most important of which being space and power efficiency.

However, some very interesting developments have been reported recently. IBM introduced its *SyNAPSE* chip [40] in 2014 whose processing units are highly connected

'brain-like' neurons. The most recent chip has one million such neurons. Similarly, Hewlett Packard announced that they would release a device in 2017, grandly named *The Machine* [38], which uses *memristors* to unify memory and compute operations. With large scale interconnectivity within these memristors, they hope to perform large scale graph pattern-matching operations at high speeds. *DNA-computers* [49] employ biological molecules as processing units which interact with other molecules swimming around in the same chemical solution. Because, even a small volume of solution contains an extremely large number of biological molecules, it is expected that the *right* sequence of interactions will be carried out in at least a few instances. The idea is to use an exponential number of processing elements to compute an exponential number of operations in polynomial time. This method can be used to solve very complex problems such as finding the *Hamiltonian path* in a graph [6].

Another idea proposed since the 1990s has been the implementation of processing in memory [47]. Although, this idea has promise, all attempts to manufacture such a chip failed in the 1990s. This is partially attributed to the manufacturing technology at the time which limited the amount of circuitry that could be fitted inside a single chip. Since then, the capacity of memory chips have grown exponentially based on Moore's law, but the growing disparity of speeds between the CPU and the memory has also led to the so-called *memory-wall*. Therefore, memory manufacturers are having a re-look at this technology.

In this dissertation, we will look at one such attempt by *Micron Technology, Inc.* Christened the *Automata Processor* (AP) [25], it has been in the works for close to a decade now. For the majority of this duration, the project was shrouded in secrecy. In 2011, our research group was the first group outside Micron, whom the developers talked to about the technology. The goal of the ensuing collaboration was to find innovative solutions to accelerate a wide variety of applications using this chip.

Subsequently, in the November of 2013, the chip was unveiled to the rest of the world during the *Supercomputing* conference at Denver, Colorado. Since then, many research

groups have joined this effort and the chip production has reached advanced stages. Some initial batches have already been manufactured and tested within the company premises. It is expected that the chip will become available in the market in late 2015.

The AP chip is a reconfigurable co-processor which is designed to compute thousands of Non-deterministic Finite Automata (NFA) in parallel on a single input data stream. It uses Dynamic Random Access Memory (DRAM) technology to provide the underlying MISD architecture. As this chip is specialized to carry out only string-pattern recognition operations, it is both space and power-efficient. Besides, it is much easier to program for these specific operations than a general-purpose FPGA.

However, although the programming environment is very simple, coming up with efficient algorithms and automata for this processor may need ingenuity and innovation on behalf of programmers who are trained on traditional processing platforms. The AP provides new operations and new avenues of parallelism to exploit, while curtailing the capability to execute others. This might require take some time and learning to get used to.

This research was the first attempt to understand these concepts and establish some basic ground rules for the design algorithmic techniques and automata for the AP. It is hoped that this will aid developers in future to master this technology quickly and create solutions for problems which are challenging to solve using existing processor technologies.

In our endeavour, we progressively tackled harder and harder problems. We started with accelerating pattern-matching applications for which the use of the chip follows naturally, i.e. applications that need to find all occurrences of thousands of complex string-patterns in an input string. We graduated to handling various classical problems in unweighted graphs, for which the solutions were not intuitive. Along the way, we devised techniques to optimize the automata in terms of size, as well as execution time, by overcoming critical performance and routing bottlenecks.

Besides these, we developed assessment techniques to accurately estimate the run-times of applications, by taking into account the overheads of various steps in different stages in

the execution pipeline. By analysing the run-times of various parts of the applications using these techniques, we could provide critical feedback to the developers of the chip to make various refinements. Some of these refinements have already made their way into the current generation of the chip, while others will be incorporated in the next generation of the chip, which is currently in the design phase.

The rest of this dissertation is organized as follows. In Chapter 2, we have described the AP hardware from an application developer's perspective. Although limited, this description is succinctly captures the prominent features of the chip required to understand the algorithm designs in the rest of the document. Readers who are interested to know more about the architectural features of the hardware are directed to the online portal [5] and the following research paper [25].

In Chapter 3, simple ways to convert NFAs expressed as classical state-diagrams to *ANML-NFA* is described. ANML (pronounced as animal) stands for *Automata Network Markup Language* which is used to define automata for the AP. We have also outlined various optimization strategies for ANML-NFA. This may be useful to automata theory experts to convert existing automata designs to ANML-NFA. The goal is to galvanize the huge body of work which currently lies dormant for want of a suitable hardware.

Next, we delve into an intuitive use of the AP to accelerate applications which search for all occurrences of thousands of complex string-patterns in input data-streams. We chose two applications, one from the network security domain and the other from the field of bioinfomatics. The first application is called Fast-SNAP (for Fast-SNort using AP) and searches for all occurrences of over 4394 *signatures* of network intrusion in network data. These signatures have been obtained from the Snort [61] database. Using the resources on a single AP board, Fast-SNAP is estimated to support *deep packet inspection* of network data packets using all these signatures from the Snort database at 8-11 Gbps. This is at least an order of magnitude faster than other applications using GPUs and FPGAs.

The second application is called PROTOMATA (for PROTein autOMATA) and looks

for all occurrences of 1308 protein *motifs* in protein sequences. These motifs have been downloaded from the PROSITE [66] database. Depending on the size of the input data and search settings, PROTOMATA can be about half a million times faster than its single-CPU-based counterpart. The above two applications are described in Chapter 4, and can serve as model implementations for other similar applications. Most of the automata parts are designed as modular *macros* which can be imported as is into future applications or with few minor modifications.

Once PROTOMATA was developed, which looks for occurrences of known motifs in the input data, the next logical step was to use the AP to accelerate the search for new unknown motifs. This second problem is significantly more difficult. In fact, the search for one of the simplest kinds of motifs called (*l,d*)-motifs is known to be *NP*-complete. The computational problem was first formulated by Pevzner in the year 2000 [57] and is called the *planted motif search* problem. Both *exact* and *approximate* solutions to this problem exist. Approximate algorithms are significantly faster, but they sometimes miss out on subtle motifs which are biologically important. Although exact algorithms to find all motifs exist, they take exponential time.

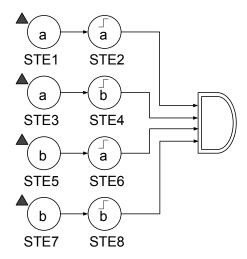

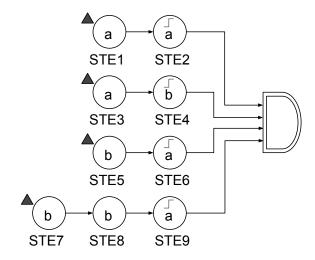

One of the ways to find these motifs is to reduce the problem to finding maximal cliques in an n-partitioned graph. A clique is a sub-graph wherein any two nodes are connected to each other. In an n-partitioned graph, the nodes are divide into n disjoint partitions, and no two nodes from the same partition are connected to one another. Therefore, the size of a maximal clique in a n-partitioned graph is at most n.

One aspect of this transformed graph problem was that the nodes in the graph represent strings, and the edges between them represented a bounded number of mismatches between these strings. We started with developing an automaton to count the number of mismatches between any two strings, by programming the first string as an automaton and streaming the other string to see which accept state the automaton reached. This automaton was then extended to a clique-finding automaton. The automaton was designed in such way

that its structure was agnostic of the input string with which it was designed. Multiple instances of such an automaton can be compiled and loaded quickly, once the input strings are provided. The complete application called MOTOMATA (for MOtif auTOMATA) is described in Chapter 5.

Developing MOTOMATA gave us a critical insight into solving graph problems using the AP. If graph nodes represent strings and edges represent a relation between those strings, then automata can be developed to check these properties in parallel leading to significant speed-up. This led us to developing solutions for other graph problems using generic graphs.

We designed a strategy to assign string labels to nodes in a generic graph, and define a relationship between those labels to signify the existence of an edge. The label of nodes which are connected by an edge exhibit this relationship, otherwise not. Some graph problems can be described as string-pattern-matching problems in this transformed notation. Automata designed to check for these relationships can then be executed in parallel in the AP to provide speed-up. We used this technique to solve various graph problems.

For example, the boolean satisfiability (SAT) problem checks whether there is some assignment of values TRUE and FALSE to the variables of a boolean formula, such that the formula evaluates to TRUE. This is a well-known NP-complete problem which can also be reduced to finding cliques of size n in an n-partitioned graph. We have already solved this problem in MOTOMATA. However, the characteristics of the input in the SAT problem is different from those of the input in MOTOMATA, lending the former to be non-viable solution as a SAT solver. Therefore, we had to come up with a new solution as described in Chapter 6.

In the planted motif search problem and the boolean SAT problem, the input itself is not a graph, but the algorithm converts it into one by representing different parts of the input as nodes in a graph. The edges between the nodes are not present in the input either, but a condition for the existence of an edge is provided. The objective of the algorithms is to find

a set of nodes which satisfy the connectivity constraint of a certain output graph structure, i.e. cliques of a certain size. Therefore, the primary goal of the automata is to check for the existence of all edges that are required to satisfy this connectivity constraint.

However in many other graph problems, all the nodes and edges are already listed in the input. Therefore, checking for the existence of edges is not the computational challenge. Instead, the problem is to arrange nodes and edges in the input graph into output graph structures such as search trees and acyclic paths. Besides, the graphs in the previous two problems where specialized i.e. the nodes were distributed into *n*-partitions. This is not the case with problems on generic graphs.

In Chapter 7, we describe methods to transform any input graph into a string notation which can be handled on the AP. Further, we define automata to use this string notation to identify the placement of the nodes and edges into the output structures for applications such as finding *single-source shortest paths*, *connected components*, and Hamiltonian paths and cycles in the graph. Some of these methods are estimated to be significantly faster than state-of-art implementations on other platforms, while others serve in demonstrating fundamental algorithmic techniques for future research.

In future, these methods may be improved to provide better performance or support a wider variety of graph problems, e.g. problems involving weighted graphs. Also, there is significant potential for research into exploring streaming solutions for graph problems using a single compute node connected to one or more AP(s), a fast flash-based I/O, and a large main-memory bank. Not only can such a system reduce the demands on cost, power and space, but may also provide efficient solutions to the large graph problems where exploiting data-locality may be difficult.

We have come a long way, starting with basic string-pattern matching applications to accelerating classic NP-hard graph problems. Some of the methods and techniques developed during this research have already started to aid other researchers to provide innovative solutions [73, 78] using the AP. It is hoped that this trend will continue into the future.

## **Chapter II**

## MICRON AUTOMATA PROCESSOR

The Automata Processor is one of the very few, if not the only processor based on the MISD architecture. The implementation of this architecture is done by using the Dynamic Random Access Memory (DRAM) technology. In a DRAM chip, a memory address and operation can be broadcast on every clock cycle to every *memory cell* in the chip using a system-wide bus. In AP, the memory-cells are replaced by *processing elements* and instead of a memory address and operation, one byte from the input data stream is broadcast in every clock cycle. A programmable *routing network* is used to connect the processing elements to one other. Through this routing network, elements activate each other in every clock cycle. Finally, an *output handling unit* is added to report whenever the occurrence of a pattern is detected.

The software required for programming the AP is available from an online developers portal [5]. A Software Development Kit (SDK) can be downloaded which describes methods to define and compile the automata and load the same into an AP. The SDK also provides run-time environment to handle all run-time operations.

Although, the chip is still not available, the SDK provides provides limited capability to simulate the execution of small automata inside the AP chip using a command-line interface. If a visual interface is desired, a *work-bench* can be downloaded to create, edit and simulate ANML-NFA through a graphical user interface. and visualize their execution over test data streams.

## 2.1 Programming Model

Executing programs on the AP involves two stages, namely the *configuration* stage and the *execution* stage. In the configuration stage, the user-defined automata are programmed into

the AP; and in the execution stage, these automata are executed in parallel on streaming data. If an automaton reaches its accept state, an output is created along with the offset in the stream where the event occurred.

## 2.1.1 Configuration Stage

The configuration stage can be further broken down into the *compilation* and *loading* steps. In the compilation step, the user-defined automata are converted into machine-loadable *images* using the AP compiler which comes with the SDK. This step involves executing complex place-and-route algorithms which may take considerable time based on the input automata. On the other hand, loading images into the AP board is extremely fast. For example, the entire AP board can be loaded with new automata in about 50 milliseconds.

According to well-known theory, finite automata and regular expression (regex) are equivalent, i.e. any finite automata can be represented as a regex, and vice-versa. The AP compiler also accepts regex defined in PCRE. In this case, the compiler internally converts them into their equivalent automata and then creates the loadable image from the same.

### 2.1.2 Execution Stage

During the execution stage, all the data strings to be checked are organized into a *data flow*. The host application running on the CPU uses the run-time environment to stream the data flow to the AP. On the AP, one byte from the data flow is broadcast to all the processing elements in every clock cycle. Henceforth, the data byte is called a *symbol* and the clock cycle is called a *symbol-cycle*. 128 million symbols can be processed per second, giving rise to a processing rate of 1 Gbps.

At the beginning of the first symbol-cycle, only the processing elements marked as *start-elements* are *active*. Each start-element processes the first symbol in the data flow. If a *match* occurs, then the start element activates all elements connected to its outgoing lines. All elements which are activated in the current symbol-cycle, process the next symbol from the data flow in the next symbol-cycle, and the process continues.

If an element is programmed as a *reporting* element, then on a match, an *output event* is generated, wherein an *output vector* is recorded in an *output buffer*. The execution continues from the next symbol-cycle as long as there are symbols left in the data flow and at least one processing element is active.

Asynchronously, the run-time environment reads the output vector from the output buffer to the main memory, decodes it and presents the host application with the id(s) of the reporting element(s) which generated the output and the offset in the data flow where the output event occurred. In case, the input patterns were defined as regexes, id(s) of the matched regex(es) are returned instead of the id(s) of the reporting element(s).

#### 2.1.3 Automata Elements

The PCRE syntax is well known to the programming community. However, the ANML language is new. Therefore, we briefly introduce it here.

The processing elements in ANML are very similar to the classical *state-diagram* representation. In a state-diagram, the *states* are depicted using circles and transitions between the states are drawn as directed edges. A state is identified using state-labels, which are placed inside the circle. In our examples, we have chosen integers to represent state-labels. Similarly, each edge is accompanied by an edge-label which appears above the arrow depicting the edge. The edge-label could be a symbol, or a set of symbols on which the transition occurs. Such a set is called a *character-class*. A *start state* is depicted using a short incoming arrow (with no source), and an *accept state* is shown by marking the boundary of the circle with double lines.

In the beginning, only the start state is active. The symbols of the search string are processed one by one. If a state is active and the symbol to be processed is present in the edge-label of any of its outgoing edge, then the state at the end of that edge is made active for the next symbol. The process continues till either all the states are inactive or one of the accept states becomes active. In the latter case, the string is accepted by the automaton.

Thus, traversing the state-diagram from a start state to an accept state while concatenating the edge labels on the way defines a string accepted by the automaton.

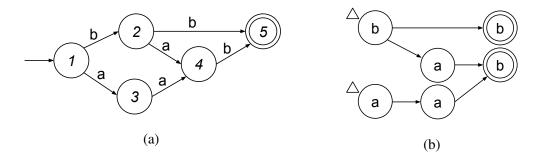

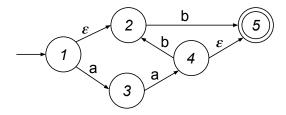

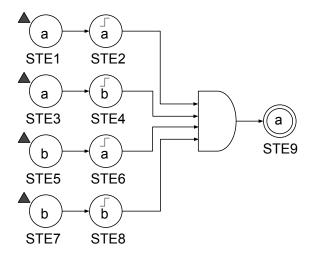

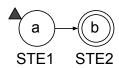

The set of all the strings accepted by an automaton is called its *language*, and the set of all the symbols appearing in these strings is called its *alphabet*. For example, the automaton whose state-diagram is shown in Figure 1 accepts the string bb while traversing the states 1,2 and 5. Its language is  $\{aab,bab,bb\}$ , and its alphabet is  $\{a,b\}$ . The alphabet of all the automata discussed throughout the rest of this chapter is  $\{a,b\}$ .

Figure 1: State-diagram of automaton to accept strings from the language {aab, bab, bb}.

In ANML, an edge transition is programmed as a *State Transition Element* (STE). An STE is represented using a circle with the edge-label placed inside it. States in the classical NFA are captured using connections between the STEs. Each STE representing an incoming edge into a state is connected to all STEs representing the outgoing edges of that state. Every STE representing an outgoing edge of the start state is marked as a *start STE*. A start STE is represented by a circle with a triangle attached to the top. Similarly, STEs representing incoming edges into an accept state are marked as *reporting STEs*. The boundary of a reporting STE is marked with double lines. The schematic representation of the ANML-NFA equivalent to the state-diagram shown in Figure 1, is presented in Figure 2.

Figure 2: Equivalent ANML-NFA for classical NFA shown in Figure 1.

The processing of a search string by the ANML-NFA can be described as follows. The symbols are processed one by one, one symbol per *symbol-cycle*. The start STE(s) are active on the first symbol-cycle. During a symbol-cycle, active STEs check the symbol against its label, and if a match occurs, activates all STEs on its outgoing edges. If a reporting STE is matched, then the string is accepted by the ANML-NFA and an output is generated.

Besides STEs, ANML-NFA can contain special processing elements called *counter* elements and *boolean* elements. These elements do not process any symbol from the data stream. Neither do they consume a symbol-cycle to complete their processing.

A counter-element is activated when STEs connected to its input line are matched in a symbol-cycle. On being activated, the counter increments the value stored in an internal *count* register by one. If the count value reaches a value stored in a *target* register, then the processing elements connected to its output line are activated for the next symbol-cycle. The target value is a 12-bit number and up to four counter elements can be cascaded together to provide a 48-bit counter.

Boolean elements can be used to emulate multiple input AND, OR, NOT, NAND, NOR, sum-of-product and product-of-sum gates. If the incoming lines of a boolean element are simultaneously activated in such a way that the boolean logic is satisfied, then the STEs connected to the outgoing lines are activated for the next symbol-cycle. Due to timing restrictions, a boolean element cannot be connected to another boolean element, and a counter element can only be connected to its input line.

These elements can be used for the compaction of automata, as well as defining automata which represent languages which are not regular. This has been discussed in detail in the next chapter.

## 2.2 Programming Resources

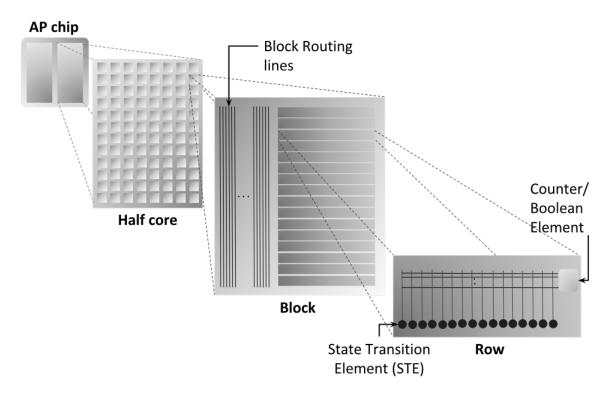

A single AP chip contains 49, 152 STEs, 768 counter elements, and 2,304 boolean elements arranged hierarchically into *rows*, *blocks*, and *half-cores*. The physical routing capability reduces as we move up the hierarchy. All 16 STEs within a single *row* can be connected to each other and to the boolean or counter element in the row. Every fourth row contains a counter element and the other three rows contain a boolean element each. However, elements from different rows need to be connected using *block routing* lines, 24 of which are shared by the 16 rows in a block. The connectivity between STEs from 96 blocks in a half-core is even more limited and is therefore avoided in our automata designs. STEs from different half-cores cannot be connected to each other, thus setting the upper limit on the size of an automaton to be the size of a half-core. The hierarchical layout of processing elements in an AP chip is shown in Figure 3.

Figure 3: Hierarchical layout of processing elements in an AP chip.

However, an AP chip does not interface with the host-processor directly. Multiple AP

chips are arranged into an Automata Processor board (AP board) which is then connected to the host-processor. Currently, development AP boards come in three form factors.

The smallest AP board contains two AP chips and connects to the host-processor over the Universal Serial Bus (USB) interface. The two AP chips are organized into a single *rank*. The rank contains a high-speed intra-rank bus which allows two separate data flows to be streamed to the two AP chips in parallel, or a common data flow to be broadcast to both the AP chips. In the latter case, the two AP chips are said to constitute a *logical core*. This provides the flexibility of either having a higher processing rate of 2 Gbps or the capability to search for a larger number of patterns against a single data flow at 1 Gbps.

The second AP board contains 32 AP chips and is connected with the host-processor using a high-speed Peripheral Component Interconnect Express (PCIe) interface. The chips are organized into 4 ranks containing 8 chips each. Similar to the previous example, all the chips in the single rank can be organized into a single logical core or into multiple logical cores of 1, 2, 4 or 8 chips. This is also done to provide flexibility. If a large number of patterns need to be programmed, and they do not fit inside a single AP chip, then a logical core with up to 8 AP chips within a rank can be used. However, in this case, the data processing rate falls to 1 Gbps for the entire rank. On the other hand, if all the patterns can be fit inside a single chip, then they can be replicated on all 8 chips on the rank 8 different streams can be processed in parallel giving a processing rate of 8 Gbps. Using the 4 ranks on the board, a large number of patterns can be handled at a cumulative processing rate of between 1 Gbps(one logical core in a single rank) and 32 Gbps (eight logical cores per rank).

The third AP board is the largest of the three and contains 48 AP chips organized into 6 ranks. It is also connected to the host-processor using a PCIe interface. Cumulatively, this AP board contains 2,359,296 STEs, 36,864 counter elements and 110,592 boolean elements. This is sufficient to accommodate thousands of patterns at the same time as we shall see in the next two chapters.

## **Chapter III**

## GENERATING EFFICIENT ANML-AUTOMATA

Having understood the processing elements in the AP, let us now look at how to convert a classical NFA expressed as a state-diagram to an *ANML-NFA*, i.e. an NFA defined in ANML. A simple method to do this was introduced in the previous chapter. This method can be extended to handle state-diagrams with even  $\varepsilon$ -transitions. The ANML-NFA derived in this way may be optimized further, which we shall see in this chapter.

Firstly, the difference in representation brings about redundancies in the ANML-NFA. For example, even if the starting state-diagram is optimal, the resultant ANML-NFA may not be so. We need to identify these redundancies and remove the same.

Secondly, The counter and boolean elements have no equivalents in the classical statediagram representation. This not only provides means to compress the ANML-NFA further, but also allows the expression of languages which are richer than the regular languages represented by classical regular expressions and NFAs.

Finally, the AP architecture has its own set of characteristics like different run-times for different operations, hardware bottlenecks, and hierarchical organizations. These characteristics place some restrictions on design of efficient ANML-NFA. We will conclude this chapter with general guidelines to design automata in adherence to the above characteristics and avoid performance bottlenecks.

## 3.1 Translating classical NFAs to ANML-NFAs

Let us revisit the simple automaton and translation technique discussed in the previous chapter. The classical and ANML representations have been reproduced in Figure 4. Each state-transition (edge) in the state-diagram is represented using an STE in the ANML-NFA. The label of the edge is programmed as the label of the STE, and shown inside the

circle representing the STE. States in the state-diagram are captured using the connections between the STEs. Each STE representing an incoming edge into a state is connected to all STEs representing the outgoing edges of that state. Every STE representing an outgoing edge of the start state is marked as a start-STE. Similarly, STEs representing incoming edges into an accept state are marked as reporting STEs. The start-STEs are delineated with a triangle at the top of the STE and perimeter of reporting STEs are demarcated using double lines.

Figure 4: Classical and ANML representation of automaton to accept strings over the alphabet  $\{a,b\}$  and from the language  $\{aab,bab,bb\}$ .

#### 3.1.1 Handling $\varepsilon$ -transitions

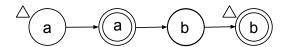

In a classical NFA, an  $\varepsilon$ -transition is defined as a spontaneous transition from one state to another without consuming any symbol from the input string. An  $\varepsilon$ -transition is depicted in a state-diagram by an edge with the  $\varepsilon$  label. For example, in Figure 5, transitions from state 1 to state 2 and state 2 to state 4 are  $\varepsilon$ -transitions.

Handling  $\varepsilon$ -transitions out of a start state was introduced in [25]. Here, we define a general technique to handle any  $\varepsilon$ -transition using the concept of  $\varepsilon$ -closure. The  $\varepsilon$ -closure of a state is defined as the set of states, containing itself and all the other states in the NFA which can be reached from that state by following only  $\varepsilon$ -transitions. For example, the  $\varepsilon$ -closure of state 1, depicted as  $\Upsilon(1)$ , is  $\{1,2\}$ . Similarly,  $\Upsilon(2) = \{2\}$  and  $\Upsilon(4) = \{4,5\}$ .

Figure 5: State-diagram of an automaton with  $\varepsilon$ -transitions.

Our technique to convert classical NFA to ANML-NFA can be extended to handle  $\varepsilon$ -transitions as follows. First, the  $\varepsilon$ -closure of every state is computed. Then, each STE representing an incoming edge into a state u should be connected to all STEs representing outgoing edges of a state v, where  $v \in \Upsilon(u)$ . If u is a start state, then all the STEs representing outgoing edges of v are marked as start STEs,  $\forall v \in \Upsilon(u)$ . Similarly, if  $\exists v \in \Upsilon(u)$ , where v is an accept state, then all the STEs representing incoming edges of u are marked as reporting STEs. The equivalent ANML-NFA to the state diagram shown in Figure 5, is shown in Figure 6.

Figure 6: Equivalent ANML-NFA of for classical NFA shown in Figure 5.

#### 3.1.2 Removing Redundancies in ANML-NFA

#### 3.1.2.1 All-input-start STE

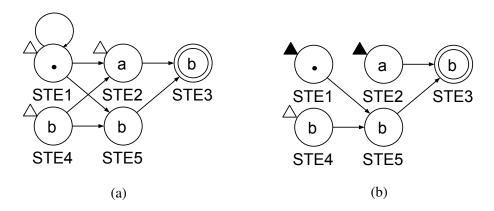

The start STE discussed until now is active only during the first symbol of the string. It is called *start-of-data* STE. However, the architecture allows a start STE to be configured as an *all-input-start* STE, which is active on every symbol of the input string. Schematically, such a start-state is depicted using a solid triangle. For example, *STE*1 and *STE*2 in Figure 7b represent all-input-start STEs.

All-input-start STEs can be used to minimize the ANML-NFA by identifying STEs which are active in every symbol-cycle. Consider the ANML-NFA shown in Figure 7a.

First, identify every start-of-data STE which has a loop to itself and whose label contains all the symbols in the alphabet (represented by \*). Such an STE is active on every symbol-cycle, and is therefore converted to an all-input-start STE. Next, consider all the start-of-data STEs connected to the outgoing edges of these all-input-start STEs. These STEs are also active on every symbol-cycle and are converted to all-input-start STEs. If any of these new all-input-start STEs also have the label \*, then the process continues in iterations until no new all-input-start STEs are found. AS a final step, all the incoming edges into any all-input-start STE are removed, as they are redundant. The optimized ANML-NFA corresponding to the one shown in Figure 7a, is shown in Figure 7b.

Figure 7: Modifying ANML-NFA using all-input-start STE.

#### 3.1.2.2 Minimizing the Number of STEs

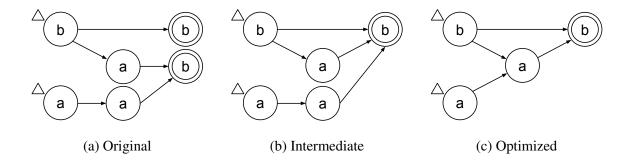

The automaton shown in Figure 1 cannot be represented by any state-diagram having less than six edges. However, its equivalent ANML-NFA, shown in Figure 8a, containing six STEs is not optimal! The optimal ANML-NFA contains four STEs as shown in Figure 8c. Amazingly, there is no way to translate the four STEs in this ANML-NFA into a classical state-diagram with four edges. This is because two of the STEs in the optimal ANML-NFA represent two edges each in the classical automaton.

The following steps may be used to identify and remove redundant STEs in an ANML-NFA:

Figure 8: Optimizing ANML-NFA to accept the words from the language  $\{aab, bab, bb\}$ .

- Identify all non-reporting STEs with no outgoing edges to any other STE. Such an STE cannot reach any reporting STE and should be removed along with all its incoming edges.

- 2. Any remaining STEs with no outgoing edges to other STEs must be reporting STEs. Merge all such STEs with the same label into a single reporting STE. For example, both the reporting STEs in Figure 2 can be merged into a single reporting STE as shown in Figure 8b.

- 3. Starting at a reporting STE, traverse backwards (following incoming edges in the reverse direction) in a breadth first fashion. For any STE, if two or more incoming edges originate from STEs with the same label, that do not have any other outgoing edges, then these edges should be merged along with the originating STEs. For example, in Figure 8c, the two STEs with label *a* connected to the reporting STE are merged into a single STE.

- 4. Repeat the above step for all reporting STEs with no outgoing edges.

It is important to remember that an all-input-start STE is different from a start-of-data STE and therefore can not be merged even if they have same label and satisfy all the other conditions mentioned in the steps above.

## 3.2 Counter Elements

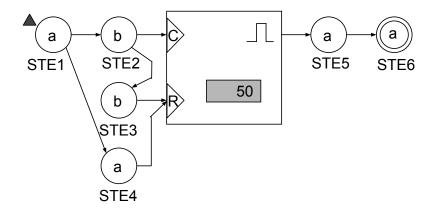

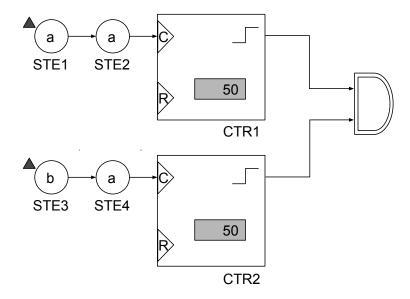

A counter element can be used to generate compact automata whenever a pattern contains a repeating sub-pattern. For example, the ANML-NFA shown in Figure 9 checks for substrings wherein the sub-pattern ab repeats 50 times consecutively followed by the sub-pattern aa, i.e. substrings accepted by the regular expression  $(ab)\{50\}aa$ . The equivalent ANML-NFA using a counter element is shown in Figure 10.

Figure 9: ANML-NFA to identify substrings accepted by the regular expression (ab)  $\{50\}aa$ .

A counter element contains a programmable 12-bit *target-value*, two input lines namely *count-line* and *reset-line*, and an *outgoing-line*. The outgoing-line can be configured to generate a *pulsed* or *latched* output. In our diagrams, a counter element is represented as a rectangle. The target-value is shown in a solid rectangle inside this rectangle. The count-line and the reset-line are shown as triangles on the left boundary, inscribed with the characters C and R respectively. The outgoing-line on the right is accompanied with the  $\square$  symbol or the  $\square$  symbol to denote the pulsed-output or the latched-output respectively.

The counter element functions as follows. The programmer sets the target-value for the counter based on the automata design. The counter element contains a *counter-value* (not shown in the ANML-NFA) which stores the current value of the counter at run-time. At the beginning of execution, the counter-value is set to 0. If during a symbol-cycle, the count-line is activated, then the counter-value is incremented by 1. However, if the reset-line is activated, then the counter-value is reset to 0. If none of the input lines are activated, then the counter-value remains unaltered. When the counter-value equals the target-value, the counter element activates its outgoing-line. If the counter element is programmed to

Figure 10: Using a counter element with *pulsed-output* to identify substrings matching the regular expression  $(ab)\{50\}aa$ .

generate a pulsed-output, the outgoing-line is activated only for the next symbol-cycle. However, if it is programmed to generate a latched-output, the outgoing-line is activated until either the counter element is reset or the end of the data-flow is encountered.

The ANML-NFA shown in Figure 10 searches for substrings which are accepted by the regular expression  $(ab)\{50\}aa$ . The occurrence of the pattern ab in the string increases the count-value by one by activating the count-line. However, the occurrence of the patterns aa or bb results in the count-value being reset to 0 by activating the reset-line. Therefore, only when the pattern ab occurs 50 times consecutively, the counter-value reaches the target-value and the outgoing-line is activated.

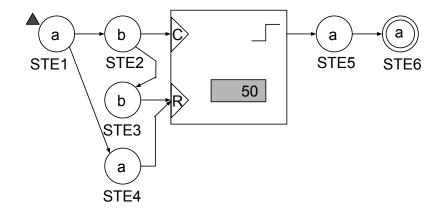

Since the counter element is programmed to generate a pulsed-output, STE5 attached to its outgoing-line is activated only for the next symbol cycle. This means STE6 reports only if the pattern aa follows exactly 50 consecutive repetitions of the pattern ab, and no more. If it is desired that the pattern aa occurs after at least 50 consecutive repetitions of the pattern ab, then the counter can be programmed with a latched-output as shown in Figure 11. In this case, STE5 is activated as long as the pattern ab continues to repeat consecutively beyond the  $50^{th}$  reiteration, i.e. the counter is not reset. Hence, this automaton finds substrings which match the regular expression  $(ab)\{50,\}aa$ .

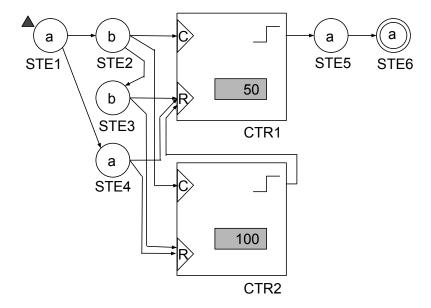

If both lower and upper bounds are desired on the number of repetitions, then two

Figure 11: Using a counter element with *latched-output* to identify substrings matching the regular expression (ab){50, }aa.

counter elements can be used as shown in Figure 12. The counter element CTR1 takes care of the lower bound (of 50), whereas CTR2 manages the upper bound (of 100). CTR1 activates STE5 on every symbol-cycle after the  $50^{th}$  consecutive repetition of the pattern ab is found. However, the output of CTR2 resets CTR1 as soon as the  $100^{th}$  consecutive repetition is encountered, and continues to do so until both CTR1 and CTR2 are reset or the end of the data-flow. Hence, this ANML-NFA reports substrings which are matched by the regular expression  $(ab)\{50,100\}aa$ .

In all the above examples, only back-to-back repetitions allow the counter-value to be incremented to the target-value. However, the counter-elements themselves do not place any such restrictions. For example, if the counter element in Figure 11 is never reset, then *STE6* would report every occurrence of the pattern *aa* after 50 occurrences of the pattern *ab* have been found. In Section 3.4, we discuss some interesting uses of such a capability.

Similar to an STE, any counter element can also be programmed to be a reporting element. Additionally, it is redundant to have more than one STE with the same label connected to the same input line of a counter-element. Therefore, the methods described in Section 3.1.2.2 to remove all redundant STEs starting with reporting STEs with the same label can also be applied to remove the redundancy in this case.

Figure 12: Using two counter elements to identify substrings matching the regular expression  $(ab)\{50,100\}aa$ .

## 3.3 Boolean Elements

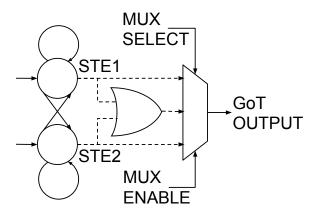

## 3.3.1 Group-of-Two (GoT)

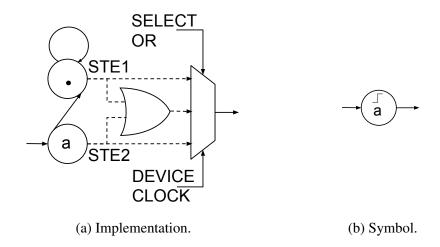

All STEs in the AP are physically organized in *Group of Twos* (GoTs) which share an *OR* gate and a 3-input multiplexer with a programmable select signal. A GoT is shown in Figure 13 along with all its routing lines. The programmable routing lines are depicted by solid lines.

Figure 13: Group of Two (GoT) STEs.

The *OR* gate in the GoT structure allows it to be configured as a *latched-STE*. A latched-STE activates the outgoing line of the GoT on every symbol-cycle subsequent to the one in which *STE*2 is matched. Figure 14a shows a GoT programmed to emulate a latched-STE programmed with the symbol *a*. For succinctness, henceforth in this paper, a latched-STE is represented using the symbol shown in Figure 14b.

Figure 14: *Latched-STE* with label *a*.

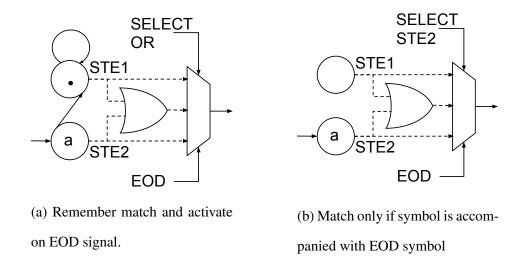

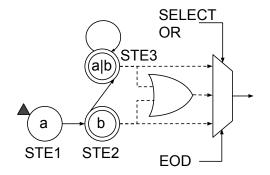

The multiplexer-select and enable lines provide further flexibility. For example, consider the programming of a GoT shown in Figure 15a. By default, the enable line is connected to the device clock of the AP. However, it can be connected to a special *End-Of-Data* (EOD) signal which can be passed at specific symbol-cycles in the data-flow. Therefore, even if *STE2* is activated and matched on any symbol-cycle, the downstream pattern matching continues only after the symbol-cycle where the EOD signal is asserted. If the matching of the label in *STE2* has to be anchored at a symbol accompanied with the EOD signal, then the connections can be made as shown in Figure 15b with the multiplexer select line choosing the output from *STE2*.

If *STE*2 in the above examples is a reporting STE, the output is generated only on symbol cycles when the EOD signal is asserted. This decreases the rate of output generation at the cost of losing information on the exact location in the input data where the match

Figure 15: Using the *select* and *enable* lines of the GoT for added flexibility.

occurred. This is useful in driving performance as discussed in Section 3.6.2.

The connections in the GoTs described above need not be explicitly defined by the user. All these features: latched/unlatched, anchored/un-anchored, reporting/non-reporting are abstracted as attributes of STEs in ANML. However, if the programmer uses the EOD signals in his/her automata designs, then he/she has to specify the symbol-cycles in which the EOD signal must be asserted, because by default it is not asserted on any symbol-cycle.

Other than the *OR* gates in the GoTs, the AP has dedicated 16-input boolean elements which can perform the *OR*, *AND*, *NOR*, *NAND*, *sum-of-product* and *product-of-sum* boolean operations. The outgoing-line of a boolean element is activated if the input lines are activated in a combination (0 for inactive and 1 for active) which satisfies the boolean operation of the element. Like all other processing elements in AP, boolean elements can also be programmed as reporting elements.

# 3.4 Handling Look-ahead Assertions

Look-ahead is an assertion defined in many modern pattern-recognition libraries such as Perl Compatible Regular Expressions (PCRE) [3] which allows the matching of a pattern in the subsequent part of the string without consuming any symbols. This allows defining

patterns succinctly which otherwise would be very complex to represent using a regular expression or classical NFA.

#### **3.4.1** Example 1

Consider a language of strings which contain all the substrings aa, ab, ba and bb. In PCRE, this can be written as (?=.\*aa)(?=.\*ab)(?=.\*ba)(.\*bb). It can be interpreted as follows: Starting at the beginning of the string, look-ahead in the string for the first occurrence of the pattern aa. If aa is found, then look-ahead for the first occurrence of the pattern ab. If ab is found, then repeat the same for the pattern ba. If all the three are found, then start consuming symbols to find the first occurrence of the pattern bb.

Figure 16 shows the equivalent ANML-NFA using a boolean *AND* element. It works as follows: *STE*1 and *STE*2 check for the pattern *aa* in the string. Since *STE*1 is an all-input start STE, the search may begin at any offset in the string. Once the pattern is found, *STE*2 which is a latched STE keeps activating the first input line of the boolean *AND* element. Similarly, *STE*3 and *STE*4 look for the pattern *ab* and so on. When all the patterns *aa*, *ab*, *ba* and *bb* have been found, all the input lines to the boolean AND element become active. The AND function is satisfied and the boolean element being a reporting element reports this occurrence.

Figure 16: Handling look-ahead assertions using a boolean AND element.

#### **3.4.2** Example 2

Though the above PCRE and ANML-NFA accept the same strings, they differ in the number of symbols consumed before the match is reported. In case of the PCRE, it is the length of the shortest prefix of the string ending with the (last) pattern *bb*. For the ANML-NFA, this number is the length of the shortest prefix containing all the four patterns.

Consider the PCRE which looks for the pattern a after the lookahead assertions have been satisfied, i.e. ((?=.\*aa) (?=.\*ab) (?=.\*ba) (.\*bb))a. This can be represented by an equivalent ANML-NFA as shown in Figure 17. Since the search for the pattern a should immediately follow the matching of pattern bb, these two are concatenated and become the new input to the boolean AND element.

Figure 17: ANML-NFA accepting the same strings as the PCRE ((?=.\*aa) (?=.\*ab) (?=.\*ba) (.\*bb))a.

# 3.5 Going Beyond Regular Languages

Counter and boolean elements provide the capability to remember information beyond the set of states which are active at any given point of time. The additional expressive power that this provides to ANML-NFA is a matter of ongoing research. For example, ANML-NFA with counter elements can emulate cellular automaton like Rule 110 which is known

to be Turing-complete. However, such a discussion is outside the purview of this paper. However let us look at an example of an ANML-NFA which defines language that are not regular, i.e. language that cannot be expressed using any classical regular expression or NFA.

### 3.5.1 Example 3

Consider a language very similar to the languages defined in Examples 1 and 2. A strings in this language contain the symbol a after all the patterns aa, ab, ba and bb have appeared at least once in the string. This pattern cannot be expressed using look-aheads in PCRE, but can be easily represented by modifying the ANML-NFA shown in Figure 16 to the one shown in Figure 18. Once all the input lines to the boolean element are activated, the AND condition is met, and STE9 is activated to check if the next symbol is a. On all subsequent symbol-cycles also, STE9 is activated by the boolean element, as all its input lines originate from latched STEs which have already been matched. Therefore, as soon as the symbol a is encountered, a match is reported.

Figure 18: ANML-NFA which accepts strings which contain the symbol *a* after all the patterns *aa*, *ab*, *ba* and *bb* have appeared at least once in the string.

#### **3.5.2** Example 4

Finally, consider the language consisting of strings where the patterns *aa* and *ba* occur at least 50 times each. Again, this language cannot be defined with regular expressions or even extended regular expression libraries like PCRE. However, the simple ANML-NFA for the same is shown in Figure 19.

Figure 19: ANML-NFA which accepts strings where the patterns *aa* and *ba* occur at least 50 times each.

# 3.6 Application Developers Notes

The programming model on the AP is as follows. ANML-NFAs defined by the user are compiled into a machine readable image which is then loaded into the AP. Once the AP has been programmed with the loaded image, the input strings are organized into a data-flow which is then streamed to the AP. Whenever, a pattern is matched an output-vector is stored inside an internal buffer to be read out to the host application running on the CPU, where it can be decoded and suitably handled. In this section, we identify aspects of the above mentioned operations which may lead to performance bottlenecks and describe general guidelines for automata-design which minimize or avoid these bottlenecks.

#### **3.6.1** Minimizing Reconfiguration Time

Compilation of ANML-NFA involves executing complex place-and-route algorithms to map elements of the user-defined ANML-NFA to physical elements on the Automata Processor board (AP board). This may take between seconds to hours based on the complexity and number of ANML-NFA to be compiled. Therefore, whenever possible, this step should be completed before-hand, and the images kept ready to be loaded at run-time. In this manner, the incurred cost at run-time is that of loading them which is in the order of 50 milliseconds.

Compilation of ANML-NFA ahead of time is possible for a variety of applications such as rule-based network intrusion detection or motif-based protein characterization. In these applications, the patterns to be looked for are known well in advance. For other applications, this might not be true. However, in some cases, although the patterns and their corresponding automata are not known ahead of time, all the required automata at run-time are copies of a few *template* ANML-NFA(s), where the copies of the same template differ only in the labels of STEs or target-values of counter elements. Such an application is defined in [62].

If the template ANML-NFA is known ahead of time, then it can be defined as an ANML-macro. The macro is compiled into an image which can be replicated easily throughout the AP board without running any place-and-route algorithms. Also, assigning the labels/target-values in all the copies of the macro can be done extremely fast. Therefore, the total time required to program the AP-board is the time required to generate the actual labels plus the time required to load the image onto the AP-board. As discussed earlier, the latter takes about 50 milliseconds. Another advantage of using macros is that they are modular in nature, making them reusable as building blocks for other ANML-NFA.

#### 3.6.2 Avoiding Stalls to Handle Output

When one or more reporting STE(s) are matched in a symbol-cycle, an *output-vector* is stored in an internal *output-buffer*. Though storing this output-vector can be completed within the same symbol-cycle, reading this vector out of the buffer to the host application may take between 91 and 291 symbol-cycles. Although the buffer can hold 1024 output-vectors at any given time, if the vectors are generated too frequently, then the output-buffer fills up and the execution has to be stalled till the buffer can be emptied sufficiently. This can considerably slow-down the execution.