## Tiling and Asynchronous Communication Optimizations for Stencil Computations

## Thesis by **Tareq Majed Yasin Malas**

In Partial Fulfillment of the Requirements

For the Degree of

#### **Doctor of Philosophy**

King Abdullah University of Science and Technology, Thuwal, Kingdom of Saudi Arabia

October, 2015

The thesis of Tareq Majed Yasin Malas is approved by the examination committee

Committee Chairperson: Professor David Keyes

Committee Member: Professor Mootaz Elnozahy

Committee Member: Professor Basem Shihada

Committee Member: Professor David Ketcheson

Committee Member: Professor Satoshi Matsuoka

Committee Member: Dr. Hatem Ltaief

Copyright ©2015

Tareq Majed Yasin Malas

All Rights Reserved

## **ABSTRACT**

Tiling and Asynchronous Communication Optimizations for Stencil Computations

#### Tareq Majed Yasin Malas

The importance of stencil-based algorithms in computational science has focused attention on optimized parallel implementations for multilevel cache-based processors. Temporal blocking schemes leverage the large bandwidth and low latency of caches to accelerate stencil updates and approach theoretical peak performance. A key ingredient is the reduction of data traffic across slow data paths, especially the main memory interface. Most of the established work concentrates on updating separate cache blocks per thread, which works on all types of shared memory systems, regardless of whether there is a shared cache among the cores. This approach is memory-bandwidth limited in several situations, where the cache space for each thread can be too small to provide sufficient in-cache data reuse.

We introduce a generalized multi-dimensional intra-tile parallelization scheme for shared-cache multicore processors that results in a significant reduction of cache size requirements and shows a large saving in memory bandwidth usage compared to existing approaches. It also provides data access patterns that allow efficient hardware prefetching. Our parameterized thread groups concept provides a controllable trade-off between concurrency and memory usage, shifting the pressure between the memory interface and the Central Processing Unit (CPU).

We also introduce efficient diamond tiling structure for both shared memory cache blocking and distributed memory relaxed-synchronization communication, demonstrated using one-dimensional domain decomposition. We describe the approach and our open-source testbed implementation details (called Girih), present performance results on contemporary Intel processors, and apply advanced performance modeling techniques to reconcile the observed performance with hardware capabilities. Furthermore, we conduct a comparison with the state-of-the-art stencil frameworks PLUTO and Pochoir in shared memory, using corner-case stencil operators. We study the impact of the diamond tile size on computational intensity, cache block size, and energy consumption. The impact of computational intensity on power dissipation on the CPU and in the DRAM is investigated and shows that DRAM power is a decisive factor for energy consumption in the Intel Ivy Bridge processor, which is strongly influenced by the computational intensity. Moreover, we show that highest performance does not necessarily lead to lowest energy even if the clock speed is fixed. We apply our approach to an electromagnetic simulation application for solar cell development, demonstrating several-fold speedup compared to an efficient spatially blocked variant. Finally, we discuss the integration of our approach with other techniques for future High Performance Computing (HPC) systems, which are expected to be more memory bandwidth-starved with a deeper memory hierarchy.

## ACKNOWLEDGEMENTS

I would like to thank sincerely my advisor Professor David Keyes for supporting my Ph.D. under the Extreme Computing Research Center (ECRC) at KAUST. I thank my parents and my wife for their continuous encouragement and for bearing with me for my preoccupation during this journey and their deep moral support at all times.

I am in debt to Georg Hager and Gerhard Wellein from Erlangen University. Their long experience in High Performance Computing and performance modeling was critical in improving our research, through our collaboration and regular meetings.

Many thanks to my fellow students and the research scientists of the ECRC for the long fruitful discussions we had and for their support.

## TABLE OF CONTENTS

| $\mathbf{E}_{2}$ | kami                   | nation Committee Approval                                          | 2          |

|------------------|------------------------|--------------------------------------------------------------------|------------|

| C                | opyri                  | $_{ m ght}$                                                        | 3          |

| $\mathbf{A}$     | bstra                  | et                                                                 | 4          |

| $\mathbf{A}$     | ckno                   | wledgements                                                        | 6          |

| Li               | st of                  | Abbreviations                                                      | 11         |

| Li               | $\operatorname{st}$ of | Figures                                                            | 13         |

| Li               | $\operatorname{st}$ of | Tables                                                             | 19         |

| 1                | Intr                   | roduction                                                          | 20         |

|                  | 1.1                    | Problem statement                                                  | 20         |

|                  | 1.2                    | Motivation                                                         | 21         |

|                  | 1.3                    | Contribution                                                       | 22         |

|                  | 1.4                    | Thesis outline                                                     | 23         |

| 2                | Bac                    | kground                                                            | <b>2</b> 4 |

|                  | 2.1                    | Stencil computations                                               | 24         |

|                  | 2.2                    | Contemporary computer processors                                   | 27         |

|                  | 2.3                    | Cache blocking                                                     | 29         |

|                  |                        | 2.3.1 Wavefront temporal blocking                                  | 29         |

|                  |                        | 2.3.2 Diamond tiling                                               | 32         |

|                  | 2.4                    | Analytic and phenomenological performance modeling                 | 34         |

| 3                | Mo                     | tivation: On spatial and temporal blocking performance limits      | 37         |

|                  | 3.1                    | Test systems: Intel Ivy Bridge and Haswell                         | 37         |

|                  | 3.2                    | Performance prediction and evaluation for pure spatial blocking $$ | 36         |

|                  |                        | 3.2.1 3D 7-point stencil with constant coefficients                | 40         |

|   |     | 3.2.2   | 3D 25-point stencil with constant coefficients             |

|---|-----|---------|------------------------------------------------------------|

|   |     | 3.2.3   | Other stencils                                             |

|   | 3.3 | Upper   | performance bounds for in-cache execution                  |

|   | 3.4 | On ter  | mporal blocking practical performance limits               |

|   |     | 3.4.1   | Single-thread wavefront diamond blocking                   |

|   |     | 3.4.2   | Cache block size model                                     |

|   |     | 3.4.3   | Memory traffic model                                       |

|   |     | 3.4.4   | Model verification                                         |

|   | 3.5 | Summ    | ary 52                                                     |

| 4 | App | oroach: | Multi-dimensional intra-tile parallelization 55            |

|   | 4.1 | Multi-  | dimensional intra-tile parallelization algorithm           |

|   | 4.2 | Girih f | framework                                                  |

|   |     | 4.2.1   | Multi-core wavefront temporal blocking                     |

|   |     | 4.2.2   | Auto-tuning                                                |

|   |     | 4.2.3   | Runtime system                                             |

|   |     | 4.2.4   | Distributed-memory parallelization                         |

| 5 | Per | forman  | ace results 69                                             |

|   | 5.1 | Frame   | works setup                                                |

|   |     | 5.1.1   | PLUTO setup                                                |

|   |     | 5.1.2   | Pochoir setup                                              |

|   |     | 5.1.3   | Girih setup                                                |

|   | 5.2 | Perfor  | mance at increasing grid size                              |

|   |     | 5.2.1   | 7-point stencil with constant coefficients                 |

|   |     | 5.2.2   | 7-point stencil with variable coefficients                 |

|   |     | 5.2.3   | 25-point stencil with constant coefficients                |

|   |     | 5.2.4   | 25-point stencil with variable coefficients                |

|   | 5.3 | Multi-  | threaded Wavefront Diamond blocking (MWD) tile sharing im- |

|   |     | pact of | n performance, memory transfer, and energy consumption 81  |

|   |     | 5.3.1   | 7-point stencil with constant coefficients                 |

|   |     | 5.3.2   | 25-point stencil with variable coefficients                |

|   |     | 5.3.3   | 25-point stencil with constant coefficients                |

|   | 5.4 | Code l  | palance and energy consumption analysis                    |

|   | 5.5 | Thread  | d scaling performance                                      |

|   |     | 5.5.1   | 7-point constant-coefficient stencil                       |

|   |     | 5.5.2   | 7-point variable-coefficient stencil                       |

|   |      | 5.5.3 25-point constant-coefficient stencil                                   | 89  |

|---|------|-------------------------------------------------------------------------------|-----|

|   |      | 5.5.4 25-point variable-coefficient stencil                                   | 89  |

|   | 5.6  | Distributed memory strong scaling performance                                 | 90  |

|   |      | 5.6.1 7-point stencil with variable coefficients                              | 91  |

|   |      | 5.6.2 25-point stencil with variable coefficients                             | 93  |

| 6 | App  | plication: Accelerating a Maxwell Equations solver for a solar                |     |

|   | cell | simulation                                                                    | 94  |

|   | 6.1  | Introduction                                                                  | 95  |

|   | 6.2  | Intra-tile parallelization implementation                                     | 99  |

|   | 6.3  | Detailed analysis of the solver's stencil codes                               | 02  |

|   |      | 6.3.1 Naïve kernel arithmetic intensity                                       | .02 |

|   |      | 6.3.2 Spatial blocking arithmetic intensity                                   | 04  |

|   |      | 6.3.3 Diamond tiling arithmetic intensity and cache size requirements 1       | 05  |

|   | 6.4  | Results                                                                       | 07  |

|   |      | 6.4.1 Thread scaling results                                                  | .09 |

|   |      | 6.4.2 Increasing grid size results                                            | 11  |

|   |      | 6.4.3 Thread group size impact on performance and memory transfers 1          | 13  |

|   | 6.5  | Summary and future work                                                       | 15  |

| 7 | Rel  | ated work                                                                     | 16  |

|   | 7.1  | Related work using separate cache block per thread                            | 18  |

|   | 7.2  | Related work utilizing cache block sharing                                    | 21  |

| 8 | Cor  | nclusion 1:                                                                   | 24  |

| 9 | Fut  | ure work and outlook                                                          | 28  |

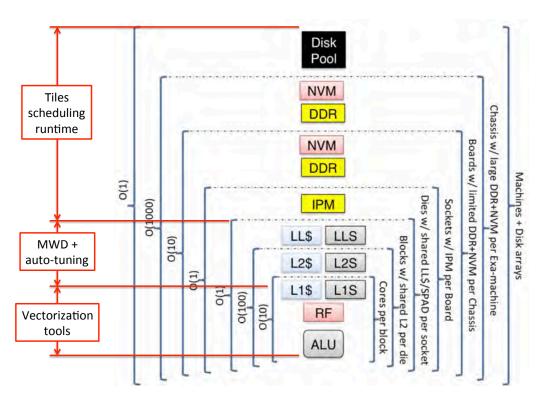

|   | 9.1  | Integrating MWD in future systems                                             | 28  |

|   |      | 9.1.1 Handling deeper memory hierarchies with MWD 1                           | 30  |

|   |      | 9.1.2 Handling long vectorization units                                       | 31  |

|   | 9.2  | Tiles software prefetching                                                    | 32  |

|   | 9.3  | Taking advantage of the memory bandwidth usage saving                         | .33 |

|   | 9.4  | Perspective on integration with accelerators                                  | 34  |

|   | 9.5  | Handling other stencil types                                                  | 35  |

|   | 9.6  | Integrating intra-tile parallelization techniques in stencil frameworks . $1$ | 37  |

|   | 9.7  | Understanding MWD behavior in the cache subsystem                             | 37  |

| Αp | pen   | dices                                                                   | 152 |

|----|-------|-------------------------------------------------------------------------|-----|

| Re | ferei | nces                                                                    | 142 |

|    | 9.11  | Handling thin domains in three-dimensional grids                        | 141 |

|    |       | finite difference PDE solvers                                           | 140 |

|    | 9.10  | Transferring temporal order derivatives to spatial order derivatives in |     |

|    | 9.9   | Krylov subspace solvers, a promising applications for MWD $$            | 140 |

|    |       | solvers with MWD                                                        | 138 |

|    | 9.8   | Handling adaptive time stepping of Partial Differential Equation (PDE)  |     |

## LIST OF ABBREVIATIONS

1WD Single-threaded Wavefront Diamond blocking

CFL Courant-Friedrichs-Lewy

CL Cache Line

CPU Central Processing Unit

DP Double Precision

DSL Domain Specific Language

ECM Execution-Cache-Memory

FDFD Finite-Difference Frequency Domain

FED Fixed-Execution to Data

FIFO First In First Out

FIT Finite Integration Technique

FMA Fused Multiply-Add FPU Floating-Point Unit

GPU Graphics Processing Unit

HPC High Performance Computing

KNC Knight's Corner

LIFO Last In First Out

LLC Last-Level Cache

LUP Lattice-site Update

MPI Message Passing Interface

MWD Multi-threaded Wavefront Diamond blocking

NUMA Non-Uniform Memory Access

PDE Partial Differential Equation PTX Parallel Thread Execution

PV Photovoltaic

RAPL Running Average Power Level

SIMD Single Instruction Multiple Data

SMX Streaming Multiprocessor

TG Thread Group

THIIM Time Harmonic Inverse Iteration Method

TLB Translation Lookaside Buffer

UMA Uniform Memory Access

## LIST OF FIGURES

| 2.1        | Different stencil update approaches for the 3-point stencil in one dimension. Fading gray boxes represent the last three updates                                                                            | 30 |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

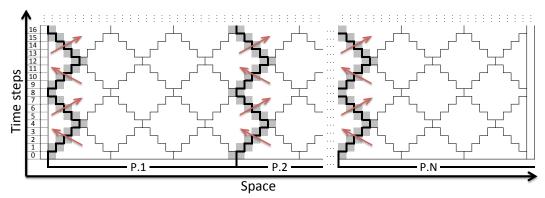

| 2.2        | Diamond tiling on a one-dimensional space grid, with arrows representing inter-tile data dependencies. The number of diamond tiles per row represents the maximum attainable concurrency (i.e., concurrency |    |

|            | limit), as the tiles in the row can be executed independently of each other.                                                                                                                                | 33 |

|            | Other                                                                                                                                                                                                       | აა |

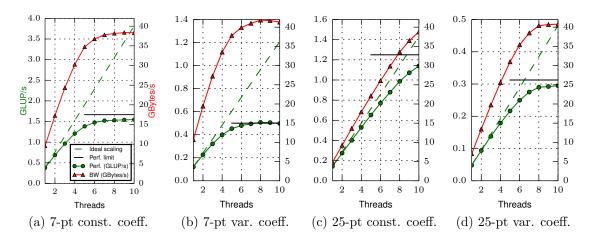

| 3.1        | Performance scaling across the cores of a chip with purely spatial blocking and data sets larger than L3 cache for the stencil algorithms shown                                                             |    |

|            | in listing 3.1 3.2 3.3 3.4. Problem sizes: $960^3$ , $680^3$ , $960^3$ , and $480^3$                                                                                                                        |    |

|            | for subfigures a, b, c, and d, respectively. STREAM COPY memory                                                                                                                                             |    |

|            | bandwidth $b_{\rm S} \approx 40{\rm GB/s}$                                                                                                                                                                  | 45 |

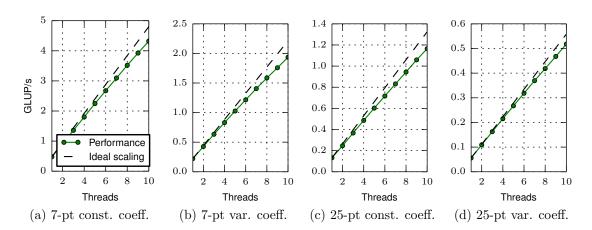

| 3.2        | Performance scaling across the cores of a chip with data sets fitting in                                                                                                                                    |    |

|            | the L3 cache for the stencil algorithms shown in listing 3.1 3.2 3.3 3.4.                                                                                                                                   |    |

|            | Problem sizes: $96 \times 96 \times 96$ , $64 \times 64 \times 48$ , $128 \times 64 \times 64$ , and $64 \times 32 \times 32$                                                                               |    |

|            | for subfigures a, b, c, and d, respectively. Variable-coefficient stencils                                                                                                                                  |    |

|            | require smaller grids to fit in cache                                                                                                                                                                       | 47 |

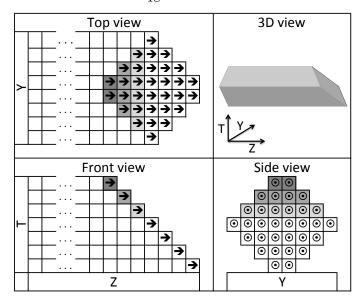

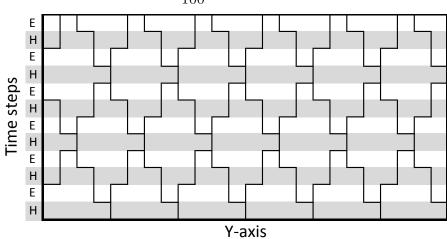

| 3.3        | Diamond tiling (along the y-axis) with single-thread wavefront tempo-                                                                                                                                       |    |

|            | ral blocking (along the $z$ -axis) in a three-dimensional space grid using wavefront width of one cell.]                                                                                                    | 48 |

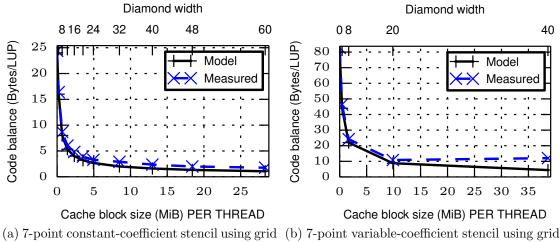

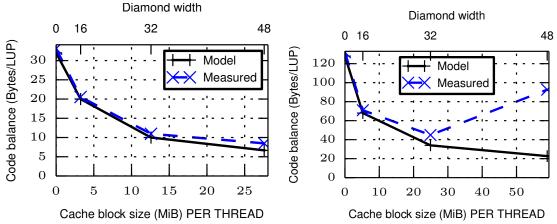

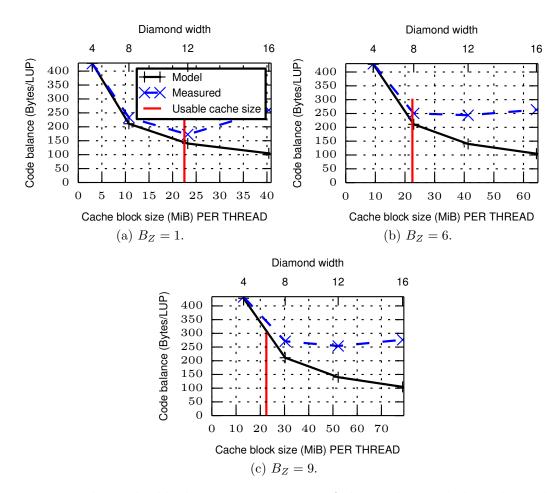

| 3.4        | Cache block size vs. modeled and measured code balance using four                                                                                                                                           | 10 |

|            | corner-case stencil operators in Intel 18-core Haswell processor. Sev-                                                                                                                                      |    |

|            | eral diamond tile sizes are evaluated using unit wavefront tile width.                                                                                                                                      |    |

|            | Cache block size and code balance are computed using the models in                                                                                                                                          |    |

|            | sections 3.4.2 and 3.4.3, respectively. All cases show accurate predic-                                                                                                                                     |    |

|            | tion of the code balance when the cache block size falls within the                                                                                                                                         |    |

|            | usable cache size (i.e., half the cache size of the processor)                                                                                                                                              | 53 |

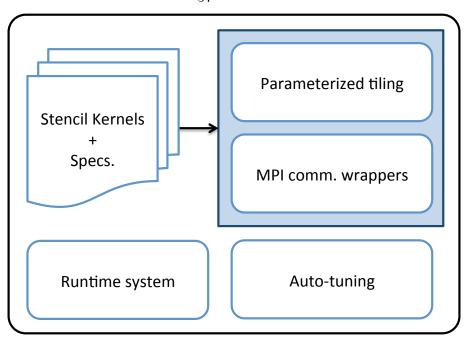

| <i>1</i> 1 | Cirih framowork diagram                                                                                                                                                                                     | 57 |

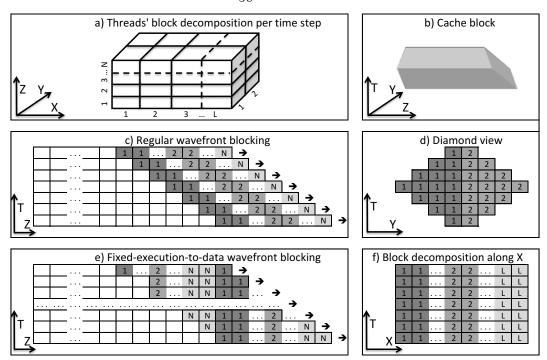

| 4.2        | Example of implementing multi-dimensional intra-tile parallelization over wavefront diamond tiles in three-dimensional grid                                                                                                           | 59  |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

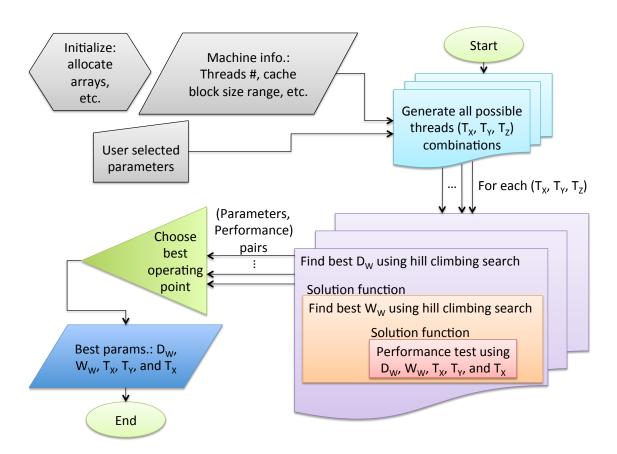

| 4.3        | Girih auto-tuner flow chart                                                                                                                                                                                                           | 63  |

| 4.4        | Distributed memory parallelization along the diamond tiling dimension. We show a diagram of the diamond tiles tessellation at the subdomain boundary in 4.4a and the pseudo code for the computation and communication order in 4.4b. | 68  |

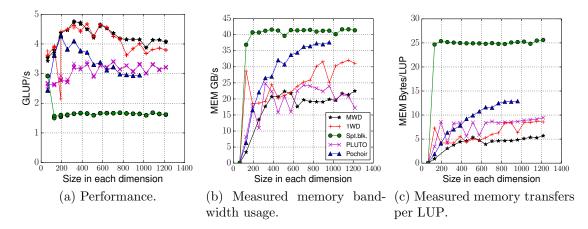

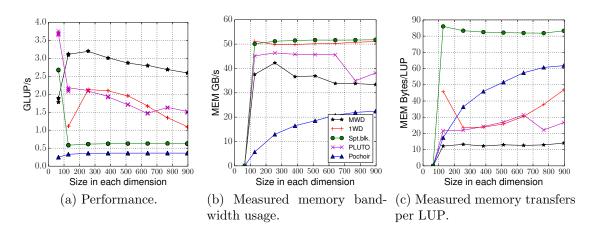

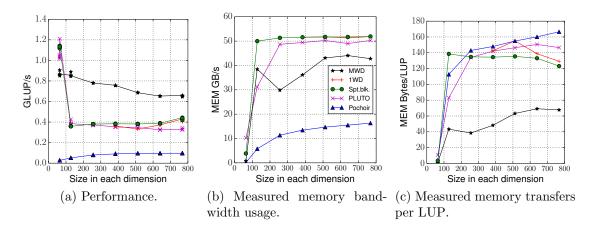

| 5.1        | Ivy Bridge 7-point constant-coefficient stencil results, using increasing cubic grid size. Showing performance and memory transfer measurements of MWD, PLUTO, Pochoir, Single-threaded Wavefront Di-                                 |     |

|            | amond blocking (1WD), and spatial blocking                                                                                                                                                                                            | 74  |

| 5.2        | Haswell 7-point constant-coefficient stencil results, using increasing cu-                                                                                                                                                            |     |

|            | bic grid size. Showing performance and memory transfer measurements                                                                                                                                                                   |     |

| <b>-</b> 0 | of MWD, PLUTO, Pochoir, 1WD, and spatial blocking                                                                                                                                                                                     | 74  |

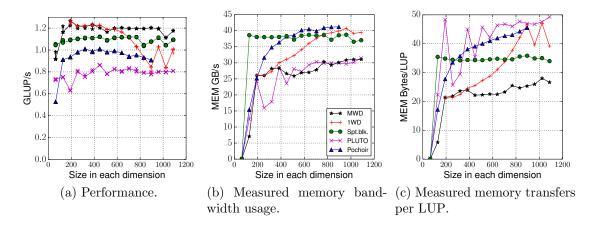

| 5.3        | Ivy Bridge 7-point variable-coefficient stencil results, using increasing                                                                                                                                                             |     |

|            | cubic grid size. Showing performance and memory transfer measure-                                                                                                                                                                     | 76  |

| 5.4        | ments of MWD, PLUTO, Pochoir, 1WD, and spatial blocking Haswell 7-point variable-coefficient stencil results, using increasing cu-                                                                                                    | 76  |

| 5.4        | bic grid size. Showing performance and memory transfer measurements                                                                                                                                                                   |     |

|            | of MWD, PLUTO, Pochoir, 1WD, and spatial blocking                                                                                                                                                                                     | 77  |

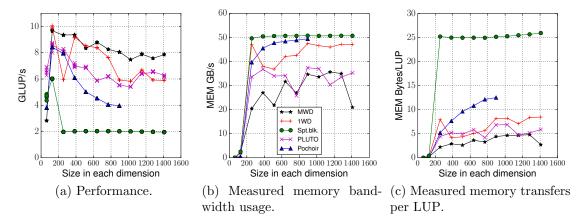

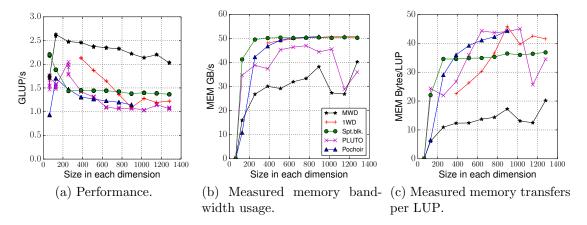

| 5.5        | Ivy Bridge 25-point constant-coefficient stencil results, using increasing                                                                                                                                                            | ' ' |

| 0.0        | cubic grid size. Showing performance and memory transfer measure-                                                                                                                                                                     |     |

|            | ments of MWD, PLUTO, Pochoir, 1WD, and spatial blocking                                                                                                                                                                               | 78  |

| 5.6        | Haswell 25-point constant-coefficient stencil results, using increasing                                                                                                                                                               |     |

|            | cubic grid size. Showing performance and memory transfer measure-                                                                                                                                                                     |     |

|            | ments of MWD, PLUTO, Pochoir, 1WD, and spatial blocking                                                                                                                                                                               | 78  |

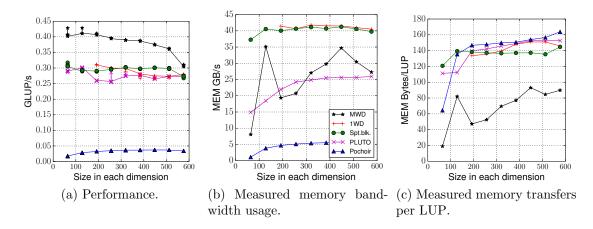

| 5.7        | Ivy Bridge 25-point variable-coefficient stencil results, using increasing                                                                                                                                                            |     |

|            | cubic grid size. Showing performance and memory transfer measure-                                                                                                                                                                     |     |

|            | ments of MWD, PLUTO, Pochoir, 1WD, and spatial blocking                                                                                                                                                                               | 79  |

| 5.8        | Haswell 25-point variable-coefficient stencil results, using increasing cu-                                                                                                                                                           |     |

|            | bic grid size. Showing performance and memory transfer measurements                                                                                                                                                                   |     |

|            | of MWD, PLUTO, Pochoir, 1WD, and spatial blocking                                                                                                                                                                                     | 80  |

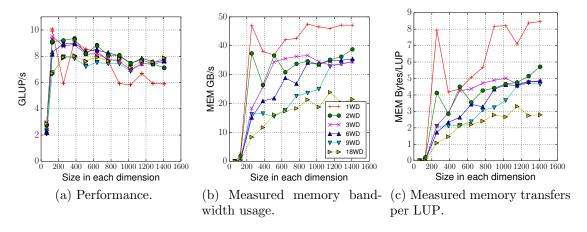

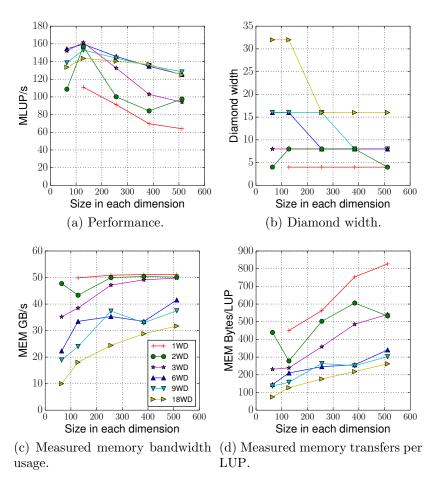

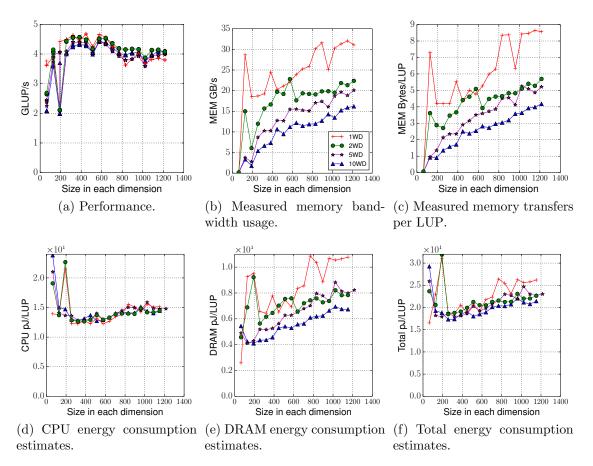

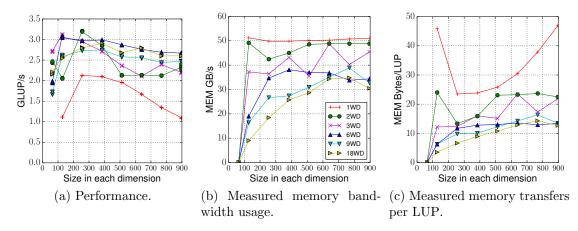

| 5.9        | Haswell performance and memory transfer measurements of the 7-point                                                                                                                                                                   |     |

|            | constant-coefficient stencil using increasing cubic grid size. We com-                                                                                                                                                                |     |

|            | pare various thread group sizes in MWD                                                                                                                                                                                                | 82  |

|      | 15                                                                                    |     |

|------|---------------------------------------------------------------------------------------|-----|

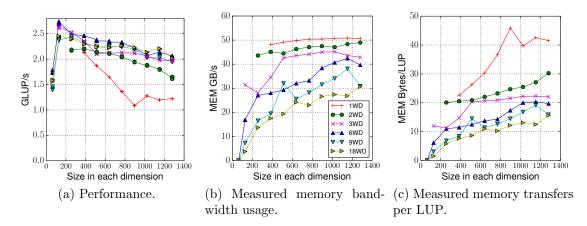

| 5.10 | Haswell performance and memory transfer measurements of the 25-                       |     |

|      | point variable-coefficient stencil using increasing cubic grid size. We               |     |

|      | compare various thread group sizes in MWD                                             | 83  |

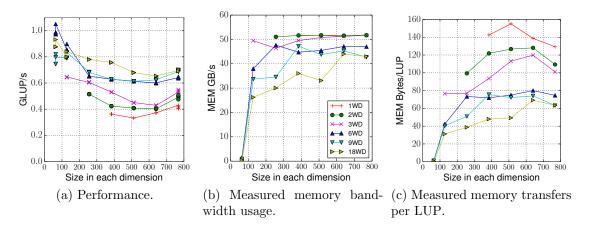

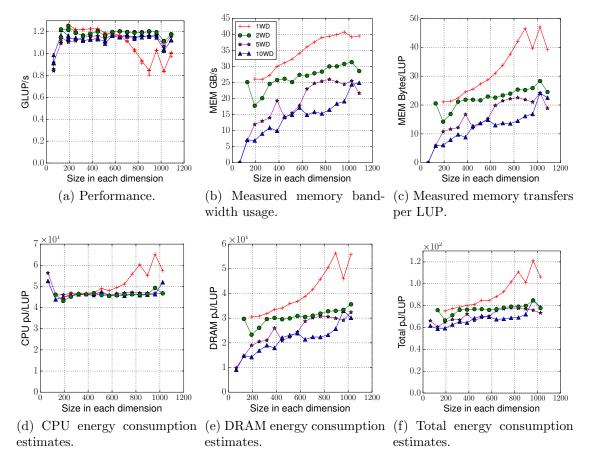

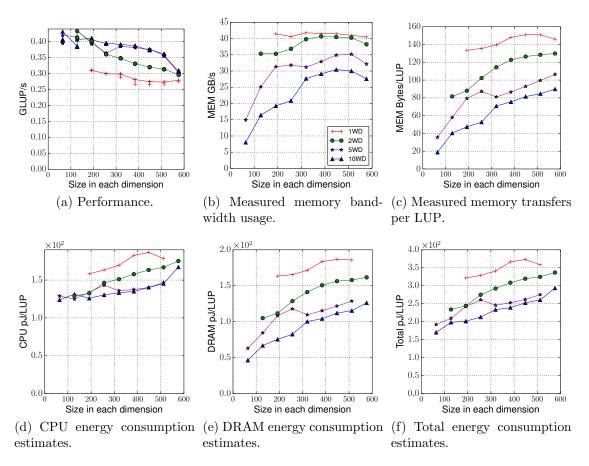

| 5.11 | Ivy Bridge performance, memory transfer measurements, and energy                      |     |

|      | consumption estimates of the 25-point constant-coefficient stencil using $$           |     |

|      | increasing cubic grid size. We compare various thread group sizes in                  |     |

|      | MWD                                                                                   | 84  |

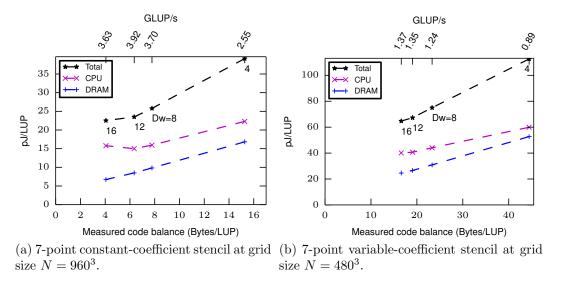

| 5.12 | Using Intel Ivy Bridge, energy vs. code balance for the seven-point                   |     |

|      | stencils at several diamond tile sizes, separately for DRAM and CPU                   |     |

|      | and as a total sum. The corresponding performance of each experiment                  |     |

|      | is shown on the top $x$ -axis. The annotation at each point represents                |     |

|      | the used diamond width. 5WD is used in the experiments                                | 86  |

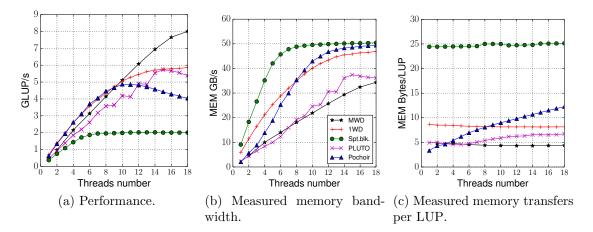

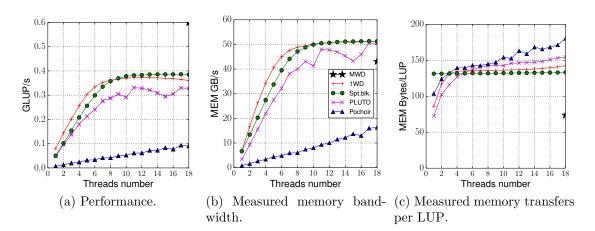

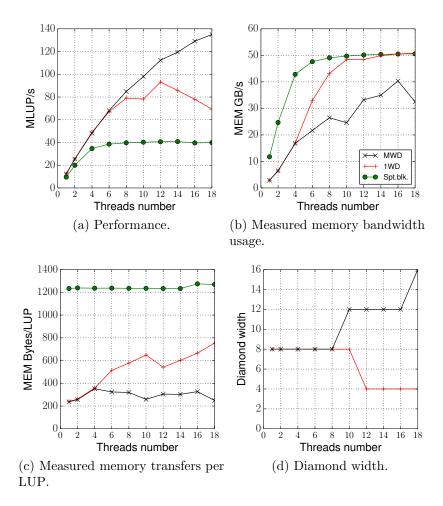

| 5.13 | Thread scaling for the 7-point constant-coefficient stencil, showing per-             |     |

|      | formance and memory transfer measurements. We compare PLUTO,                          |     |

|      | Pochoir, 1WD, MWD, and spatially blocked code variants on the 18-                     |     |

|      | core Haswell socket at a grid size of 896 <sup>3</sup>                                | 88  |

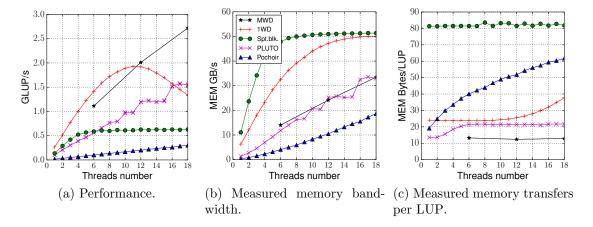

| 5.14 | Thread scaling for the 7-point variable-coefficient stencil, showing per-             |     |

|      | formance and memory transfer measurements. We compare PLUTO,                          |     |

|      | Pochoir, 1WD, MWD, and spatially blocked code variants on the 18-                     |     |

|      | core Haswell socket at a grid size of 768 <sup>3</sup>                                | 88  |

| 5.15 | Thread scaling for the 25-point constant-coefficient stencil, showing                 |     |

|      | performance and memory transfer measurements. We compare PLUTO,                       |     |

|      | Pochoir, 1WD, MWD, and spatially blocked code variants on the 18-                     | 0.0 |

| F 10 | core Haswell socket at a grid size of 896 <sup>3</sup>                                | 89  |

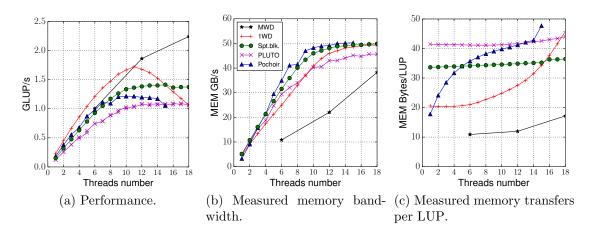

| 5.16 | Thread scaling for the 25-point variable-coefficient stencil, showing per-            |     |

|      | formance and memory transfer measurements. We compare PLUTO,                          |     |

|      | Pochoir, 1WD, MWD, and spatially blocked code variants on the 18-                     | 00  |

| F 17 | core Haswell socket at a grid size of 768 <sup>3</sup>                                | 90  |

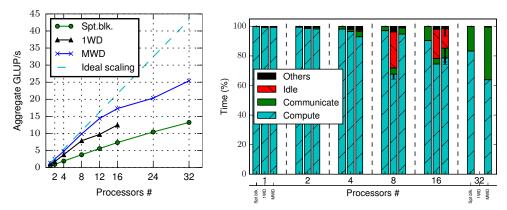

| 5.17 | Distributed memory strong scaling performance of the 7-point stencil                  |     |

|      | with variable coefficients at a grid size of 768 <sup>3</sup> . Each MPI process uses | 01  |

| E 10 | a ten core Intel Ivy Bridge processor                                                 | 91  |

| 5.18 | Distributed memory strong scaling performance of the 25-point stencil                 |     |

|      | with variable coefficients at a grid size of 512 <sup>3</sup> . Each MPI process uses | വാ  |

|      | a ten core Intel Ivy Bridge processor                                                 | 93  |

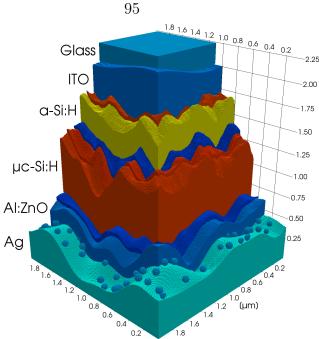

| 6.1 | Cross-section of a sample simulation setup of a tandem thin-film solar                                     |     |

|-----|------------------------------------------------------------------------------------------------------------|-----|

|     | cell. The amorphous (a-Si:H) and microcrystalline silicon ( $\mu$ c-Si:H)                                  |     |

|     | layers have textured surfaces to increase the light trapping ability of                                    |     |

|     | the cell. $SiO_2$ nano particles are incorporated to further increase light                                |     |

|     | scattering at the bottom electrode (Ag)                                                                    | 95  |

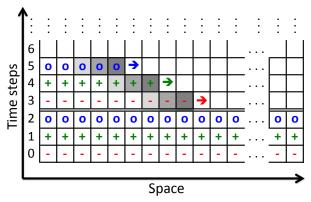

| 6.2 | Diamond tile shape along the $y$ -axis for the Time Harmonic Inverse                                       |     |

|     | Iteration Method (THIIM) stencil. Although the $\hat{\mathbf{H}}$ and $\hat{\mathbf{E}}$ fields are        |     |

|     | updated in the same iteration of the simulation code, we split them                                        |     |

|     | in our tiling implementation to achieve better data reuse and better                                       |     |

|     | diamond tile tessellation                                                                                  | 100 |

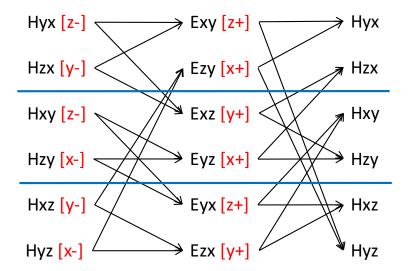

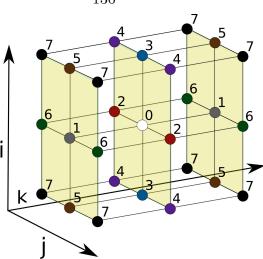

| 6.3 | $\hat{\mathbf{H}}$ and $\hat{\mathbf{E}}$ field dependencies of the THIIM stencil kernel. Each field       |     |

|     | is updated by reading six domain-sized arrays of the other field. The                                      |     |

|     | arrows indicate dependencies over the same location in the grid and                                        |     |

|     | a unit index offset. The (red) labels in square brackets indicate the                                      |     |

|     | axis and the direction of the offset. The (blue) horizontal lines split                                    |     |

|     | the components in three regions to indicate the components update                                          |     |

|     | parallelism using three threads                                                                            | 101 |

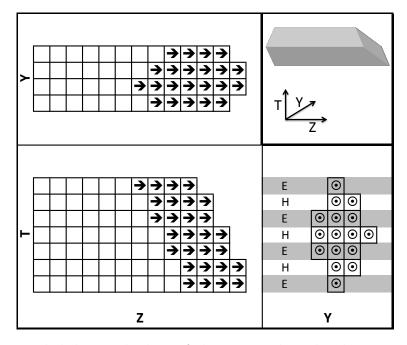

| 6.4 | Extruded diamond tiling of the THIIM kernels, showing an example                                           |     |

|     | of $D_w = 4$ and $W_w = 4$ . The data dependencies of the $\hat{\mathbf{H}}$ and $\hat{\mathbf{E}}$ fields |     |

|     | allow more data reuse in the wavefront                                                                     | 101 |

| 6.5 | The cache block size requirements of the application's kernels at three                                    |     |

|     | wavefront widths $(B_Z)$ . We use an 18-core Haswell at grid size $480^3$ ,                                |     |

|     | running a single thread with the 1WD approach. Smaller wavefront                                           |     |

|     | tile widths, which provide less concurrency along the $z$ -axis, enable                                    |     |

|     | more data reuse                                                                                            | 108 |

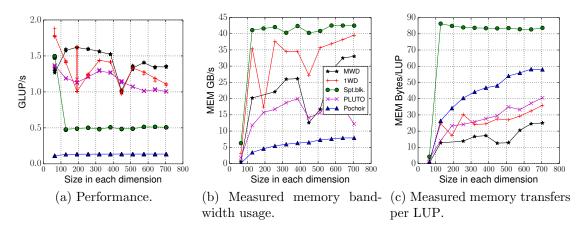

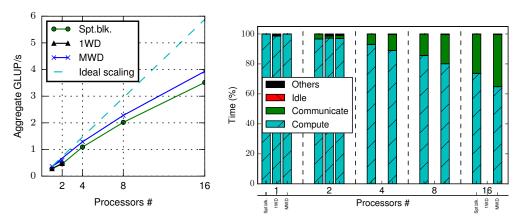

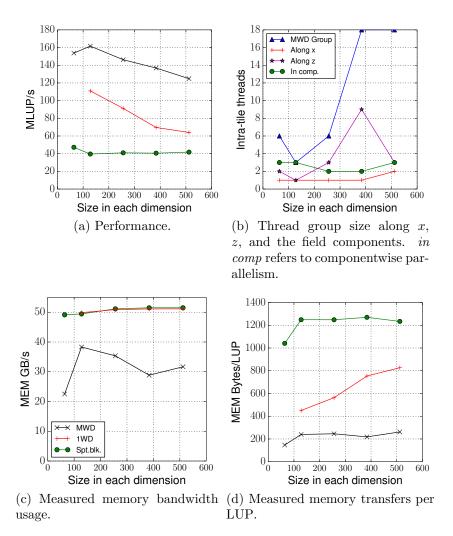

| 6.6 | The THIIM stencil performance and memory transfer measurements,                                            |     |

|     | comparing 1WD, MWD, and spatially blocked code variants on an 18-                                          |     |

|     | core Haswell socket at increasing number of threads using grid size                                        |     |

|     | $384^3$                                                                                                    | 110 |

| 6.7 | The THIIM stencil kernel performance and memory transfer measure-                                          |     |

|     | ments, comparing 1WD, MWD, and spatially blocked code variants on                                          |     |

|     | an 18-core Haswell socket at increasing cubic grid size                                                    | 112 |

| 6.8 | The THIIM stencil kernel performance and memory transfer measurements, comparing various thread group sizes in MWD on an 18-core Haswell socket at increasing cubic grid size. The results show the ability of our approach to reduce significantly the required memory bandwidth and transfer volumes |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9.1 | Outlook for integrating MWD with other techniques in future architectures. Figure with courtesy of Pete Beckman, Argonne National                                                                                                                                                                      |

|     | Laboratory                                                                                                                                                                                                                                                                                             |

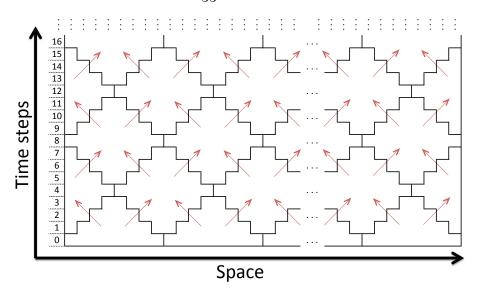

| 9.2 | Utilizing Z-ordering space-filling-curves to visit diamond tiles hierar-                                                                                                                                                                                                                               |

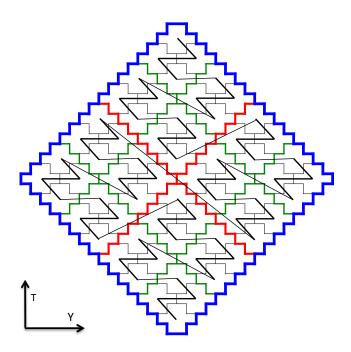

|     | chically. Four tessellation levels are shown using black, green, red, and                                                                                                                                                                                                                              |

|     | blue colors for the diamonds' boundaries of three tessellation levels.                                                                                                                                                                                                                                 |

|     | This recursive tessellation nature of diamond tiles make them good                                                                                                                                                                                                                                     |

|     | candidates for cache-oblivious algorithms                                                                                                                                                                                                                                                              |

| 9.3 | An example of box stencil operator, which extends diagonally to the                                                                                                                                                                                                                                    |

|     | axes                                                                                                                                                                                                                                                                                                   |

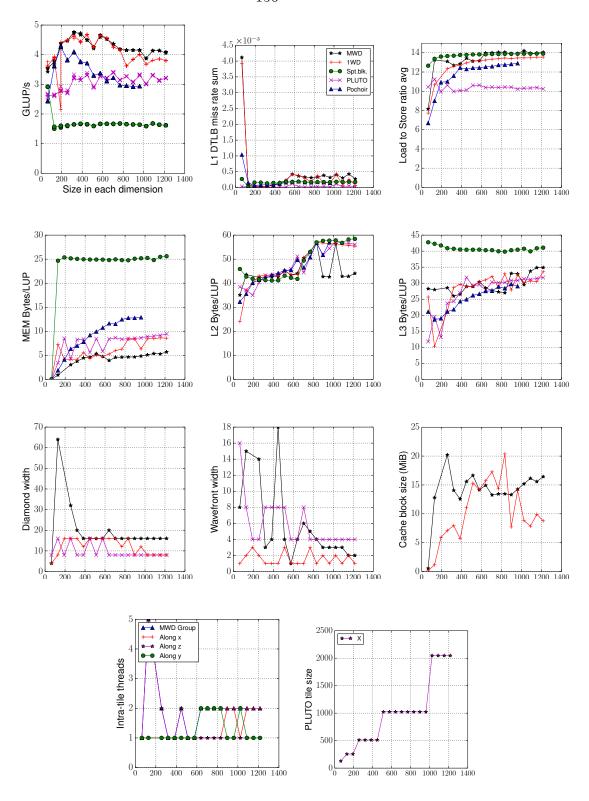

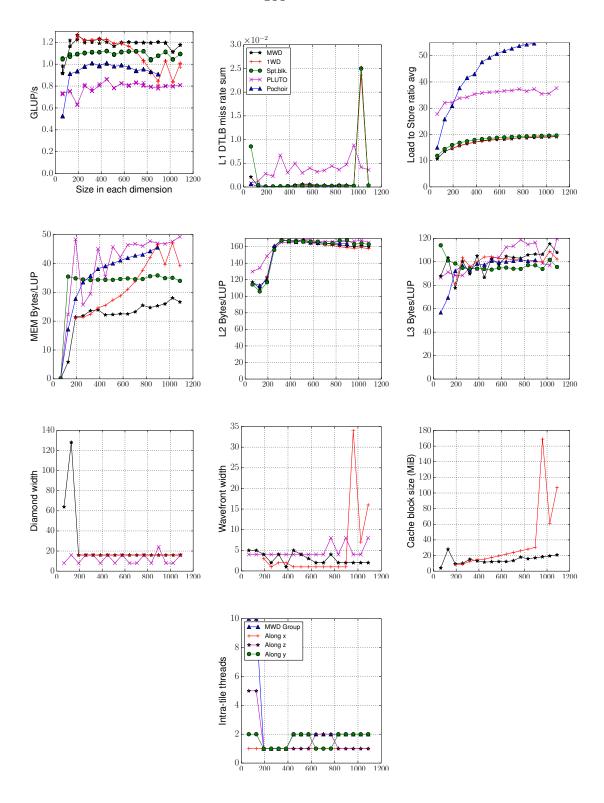

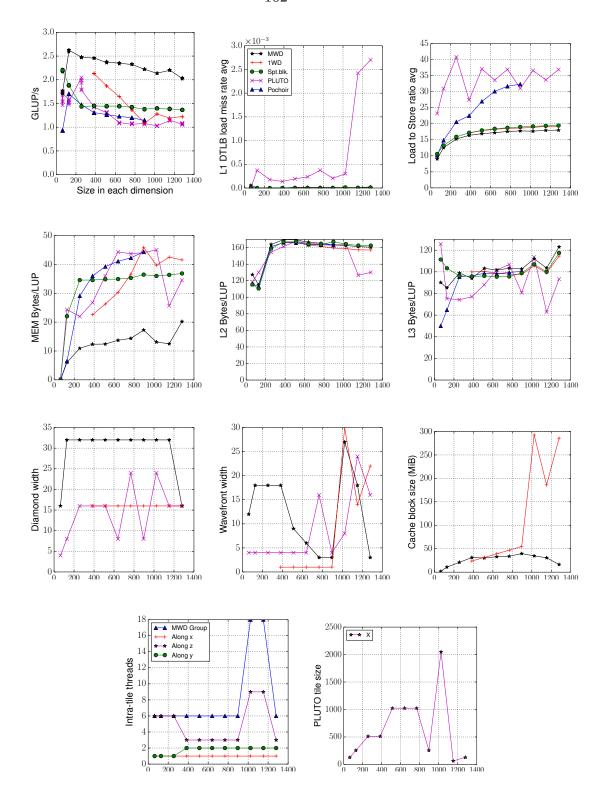

| B.1 | Ivy Bridge 7-point constant-coefficient stencil results, using increasing                                                                                                                                                                                                                              |

|     | cubic grid size. Showing various hardware counters measurements and                                                                                                                                                                                                                                    |

|     | tiling parameters of MWD, PLUTO, Pochoir, 1WD, and spatial blocking. 156                                                                                                                                                                                                                               |

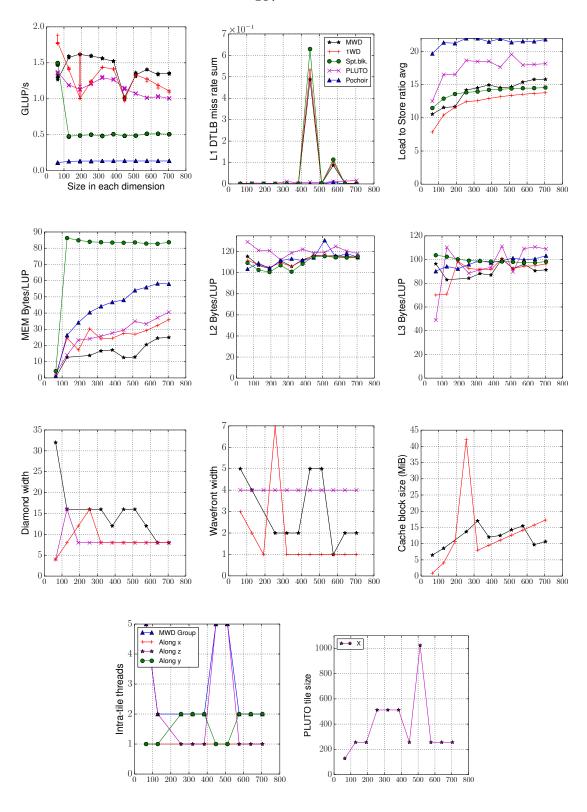

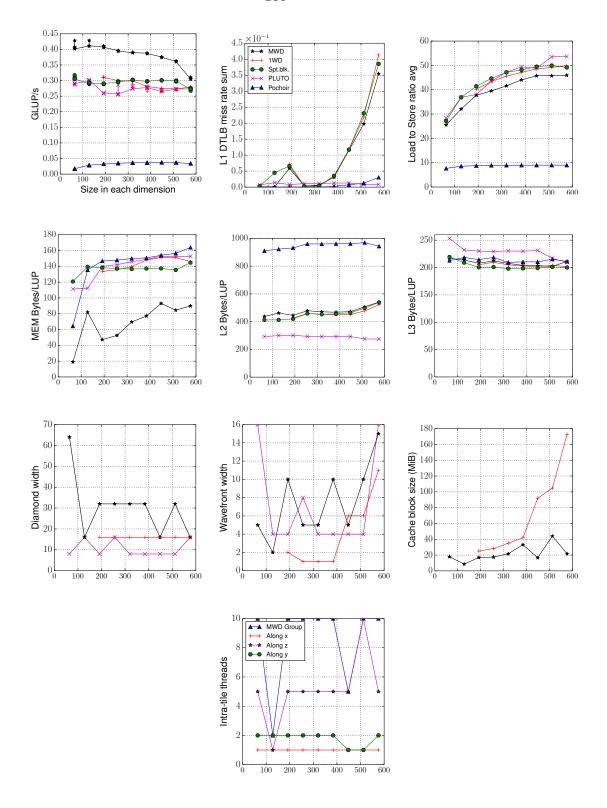

| B.2 | Ivy Bridge 7-point variable-coefficient stencil results, using increasing                                                                                                                                                                                                                              |

|     | cubic grid size. Showing various hardware counters measurements and                                                                                                                                                                                                                                    |

|     | tiling parameters of MWD, PLUTO, Pochoir, 1WD, and spatial blocking. 157                                                                                                                                                                                                                               |

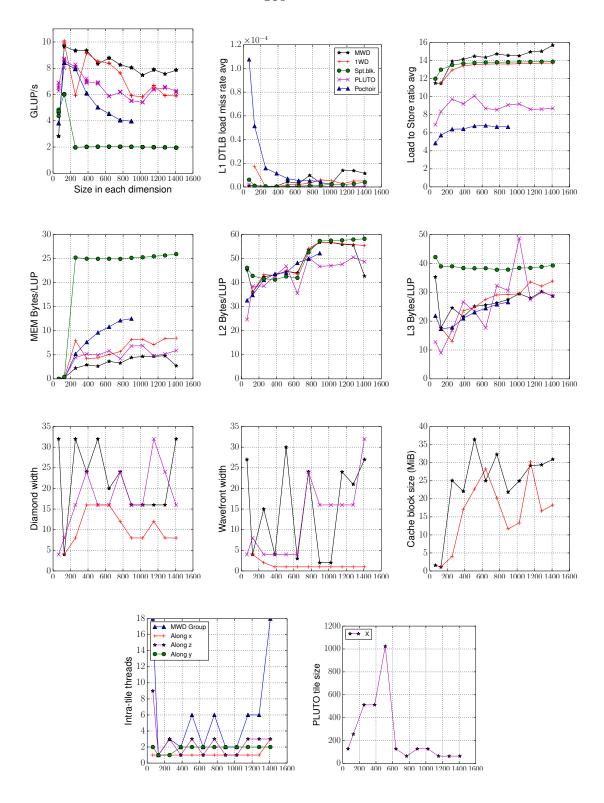

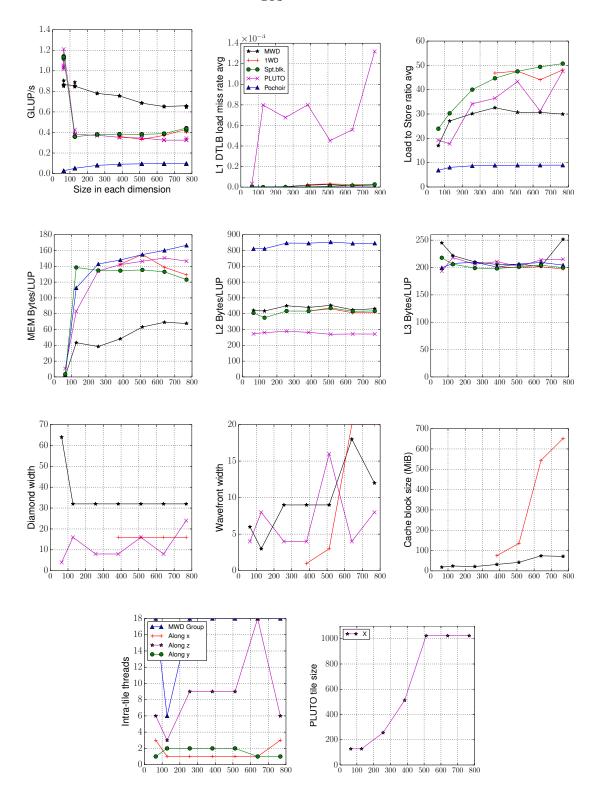

| В.3 | Ivy Bridge 25-point constant-coefficient stencil results, using increasing                                                                                                                                                                                                                             |

|     | cubic grid size. Showing various hardware counters measurements and                                                                                                                                                                                                                                    |

|     | tiling parameters of MWD, PLUTO, Pochoir, 1WD, and spatial blocking. 158                                                                                                                                                                                                                               |

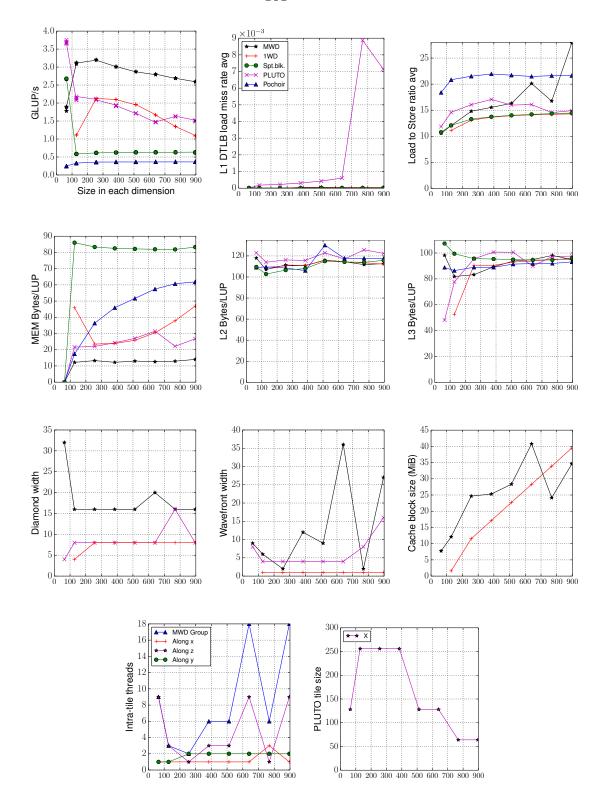

| B.4 | Ivy Bridge 25-point variable-coefficient stencil results, using increasing                                                                                                                                                                                                                             |

|     | cubic grid size. Showing various hardware counters measurements and                                                                                                                                                                                                                                    |

|     | tiling parameters of MWD, PLUTO, Pochoir, 1WD, and spatial blocking. 159                                                                                                                                                                                                                               |

| B.5 | Haswell 7-point constant-coefficient stencil results, using increasing cu-                                                                                                                                                                                                                             |

|     | bic grid size. Showing various hardware counters measurements and                                                                                                                                                                                                                                      |

|     | tiling parameters of MWD, PLUTO, Pochoir, 1WD, and spatial blocking. 160                                                                                                                                                                                                                               |

| B.6 | Haswell 7-point variable-coefficient stencil results, using increasing cu-                                                                                                                                                                                                                             |

|     | bic grid size. Showing various hardware counters measurements and                                                                                                                                                                                                                                      |

|     | tiling parameters of MWD, PLUTO, Pochoir, 1WD, and spatial blocking. $161$                                                                                                                                                                                                                             |

| B.7 | Haswell 25-point constant-coefficient stencil, using increasing cubic   |      |

|-----|-------------------------------------------------------------------------|------|

|     | grid size. Showing various hardware counters measurements and tiling    |      |

|     | parameters of MWD, PLUTO, Pochoir, 1WD, and spatial blocking            | 162  |

| B.8 | Haswell 25-point variable-coefficient stencil results, using increasing |      |

|     | cubic grid size. Showing various hardware counters measurements and     |      |

|     | tiling parameters of MWD, PLUTO, Pochoir, 1WD, and spatial blocking     | .163 |

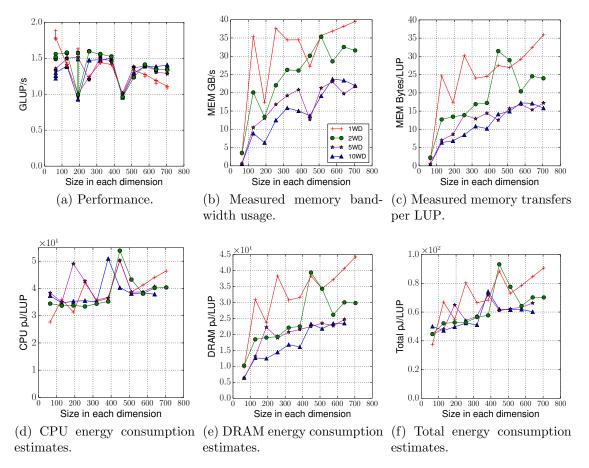

| C.1 | Ivy Bridge 7-point constant-coefficient performance, memory transfer    |      |

|     | measurements, and energy consumption estimates using increasing cu-     |      |

|     | bic grid size. We compare various thread group sizes in MWD             | 165  |

| C.2 | Ivy Bridge 7-point variable-coefficient stencil performance, memory     |      |

|     | transfer measurements, and energy consumption estimates using in-       |      |

|     | creasing cubic grid size. We compare various thread group sizes in      |      |

|     | MWD                                                                     | 166  |

| C.3 | Haswell 7-point variable-coefficient stencil performance and memory     |      |

|     | transfer measurements using increasing cubic grid size. We compare      |      |

|     | various thread group sizes in MWD                                       | 166  |

| C.4 | Haswell 25-point constant-coefficient stencil performance and memory    |      |

|     | transfer measurements using increasing cubic grid size. We compare      |      |

|     | various thread group sizes in MWD                                       | 167  |

| C.5 | Ivy Bridge 25-point variable-coefficient stencil performance, memory    |      |

|     | transfer measurements, and energy consumption estimates using in-       |      |

|     | creasing cubic grid size. We compare various thread group sizes in      |      |

|     | MWD                                                                     | 167  |

## LIST OF TABLES

| 2.1 | Contemporary processor characteristics, showing the trend of memory   |    |

|-----|-----------------------------------------------------------------------|----|

|     | bandwidth decreasing per core                                         | 28 |

| 5.1 | Phenomenological ECM models, predictions, and performance mea-        |    |

|     | surements for the four stencils under investigation with MWD at large |    |

|     | grid sizes on the Intel Ivy Bridge CPU                                | 73 |

| 5.2 | Phenomenological ECM models, predictions, and performance mea-        |    |

|     | surements for the four stencils under investigation with MWD at large |    |

|     | grid sizes on the Intel Haswell CPU                                   | 73 |

## Chapter 1

### Introduction

In this chapter we introduce the problem, motivation, and the contribution of our work. We also provide an overview of this thesis.

#### 1.1 Problem statement

In this thesis, we introduce data traversal ordering schemes that offer a substantial reduction in memory bandwidth usage and cache size requirements in the memory bandwidth demanding stencil computations on multi- and many-core processors. Performance modeling of the baseline and the proposed techniques is utilized to provide tight bounds on the achievable performance and provide sufficient understanding of the obtained performance. We investigate the benefit of our techniques on corner-case stencil kernels and a solar cell simulation application to improve their performance on both contemporary and future processors. Our proposed approach performs efficient multi-dimensional intra-tile parallelization of wavefront and diamond temporal blocking/tiling schemes. Diamond tiling provides a convenient data structure for performing domain decomposition in a distributed memory configuration. Combining wavefront blocking with diamond tiling maximizes the in-cache data reuse in three-dimensional solution domains.

#### 1.2 Motivation

The evaluation of stencil operators on Cartesian lattices is a classic kernel in computational science and engineering, arising from systems that are "born" discrete and from discretizations of PDEs, both explicit and implicit. In the implicit case the iteration index is analogous to explicit time and stencil evaluation becomes a case of sparse matrix-vector multiplication with special structure. Lattice values are updated from neighbors at a previous time step or iteration sweep with concurrency that scales linearly with the number of degrees of freedom. However, low flop-perbyte ratios put a premium on locality: regular access patterns allow high spatial locality, in the sense of packing cache blocks. The modest temporal locality within a single iteration from reuse of a value within several adjacent stencils can be enhanced across iterations, with the explicit goal of bringing the code balance, i.e., the ratio of memory data traffic to arithmetic work, closer to the machine balance, i.e., the ratio of memory bandwidth to peak arithmetic performance [1]. On modern hardware, and for most non-optimized stencil algorithm implementations, the machine balance is usually much smaller than the code balance, which leads to performance being governed by the memory bandwidth. Any reduction of code balance will thus lead to a proportional performance increase, up to a point where execution decouples from memory and other bottlenecks apply.

In future computer architectures each node may have up to a thousand shared-memory cores with: small memory bandwidth per core, small cache size per core, complex cache sharing among cores, expensive synchronization among all the cores, interaction between heterogeneous processors, and expensive intra-node lockstep synchronization after each iteration of stencil computations. The development of algorithms that can run these stencil computations efficiently on the emerging HPC systems is essential.

#### 1.3 Contribution

We propose a multi-dimensional intra-tile parallelization scheme using multi-core wavefront diamond blocking for optimizing practically relevant stencil algorithms. The results demonstrate a substantial reduction in cache block size and memory bandwidth requirements using four corner-case stencil types that represent a full range of practically important stencil computations. In contrast to many temporal blocking approaches in the literature, our approach efficiently utilizes the shared cache between threads of modern processors. It also provides a controllable tradeoff between memory bandwidth per thread and frequency of synchronization to alleviate the bottleneck at the CPU or memory interface, as needed when applying a stencil to a particular architecture. Relaxed synchronization of Message Passing Interface (MPI) messages and overlapping of computations with communication in distributed implementations is achieved through the structure of diamond tiling.

Our scheme provides cache block sharing along the leading dimension (the dimension of most rapid index advance in a Cartesian ordering) that results in better utilization of hardware prefetching to the shared cache level. We introduce a novel Fixed-Execution to Data (FED) wavefront parallelization technique that reduces the data movement in the cache hierarchy of the processor by using tiling hyperplanes that are parallel to the time dimension. Our approach achieves hierarchical cache blocking by using large tiles in the shared cache level and fitting subsets of the tiles in the private caches of the threads, providing cache blocks that span multiple cache domains. Our implementation uses an efficient runtime system to dynamically schedule tiles to thread groups. We also develop an efficient fine-grained synchronization scheme to coordinate the work of the thread groups and avoid race conditions. Finally, coupled with auto-tuning, our cache block sharing algorithm provides a rich set of run-time configurable options that allow architecture-friendly data access patterns for various setups.

#### 1.4 Thesis outline

Chapter 2 provides a background of stencil computations and temporal blocking techniques relevant to our contribution. We motivate our approach through comprehensive analysis of efficient spatial and temporal blocking techniques over stencil types representing corner cases in Chapter 3. Chapter 4 presents our main contribution, a multi-dimensional intra-tile parallelization scheme that is implemented using MWD tiling, extending previous state-of-the-art to the many-core frontier. Experimental results of our proposed approach including an extension to distributed memory are presented in Chapter 5. We also show the effectiveness of our work in a real application in Chapter 6. A review of the related work is described in Chapter 7. Finally, we conclude in Chapter 8 and present the potential extensions of our work to different applications and expected future HPC systems in Chapter 9.

## Chapter 2

## Background

We provide an introduction to stencil computations in this chapter. We also describe important memory and energy properties of contemporary processors. Cache blocking techniques are essential to improve the performance of stencil computations in contemporary processors, so we describe some very efficient cache blocking techniques in detail. To understand the efficiency of the achieved performance, given the hardware resources limits, we review two important performance modeling techniques, the Roofline and the Execution-Cache-Memory (ECM) models.

#### 2.1 Stencil computations

Regular stencil computations arise as kernels in structured grid finite-difference, finite-volume, and finite-element discretizations of partial differential equation conservation laws and constitute the principal innermost kernel in many temporally explicit schemes for such problems. They also arise as a co-principal innermost kernel of Krylov solvers for temporally implicit schemes on regular grids. In [2], they constitute the fifth of the "seven dwarfs," the class of floating point kernels that receive the greatest attention in high performance computing.

In iterative stencil computations of explicit or implicit type, each point in a multidimensional spatial grid is updated using weighted contributions from neighboring points, whose locations and weights define the stencil operator. Depending upon the application, the weights can be constant or variable in space and/or time with some or no symmetry to be exploited around the updated point.

A major demarcation exists between stencils whose coefficients are constant in space and time and those that vary, since variable coefficients can shift the dominant working set from the lattice values being updated to the coefficients themselves. In the PDE context, coefficient variability can arise from constitutive parameters (conductivities, elastic moduli, etc.) that depend upon space or time intrinsically or through dependencies on the evolving field values, themselves, the typical nonlinear case. Some models can be scaled so that the variability affects only the diagonal term of the stencil, which is then an important case to which to specialize. Whether to compute coefficients on-the-fly is a decision that affects the code balance, since it both releases all of the memory bandwidth to the lattice values and increases the flop intensity of the typical lattice update. For this reason, we incorporate examples of both constant and variable coefficient operators into our models and experiments.

Another decisive property of stencil operators is their local spatial extent, which derives from the truncation error order of the finite discretization scheme. In contemporary applications that drive fast stencil evaluations, such as seismic imaging, eighth order is used in industrial applications of which we are aware [3]. This contrasts with the second-order schemes for which the greatest amount of performance-oriented research has been done to date.

Another property of stencil operators with fundamental impact on achievable efficiency is the spatial dimension. Our contribution concentrates on the most common case of three dimensions, though our illustrations of concepts often retreat into one or two dimensions, so that space and time fronts can be visualized on planar figures. In principle, each spatial dimension may be treated in the same or in a different way with respect to partitioning and participation in wavefronts, as we show in our work

and the literature.

Our work includes stencil computation kernels that use a "Jacobi-like" update scheme where the stencil array (i.e., the data structure with read access to neighboring grid points) is not written to during the same sweep. Another possible variant is "Gauss-Seidel" update scheme, where the stencil array is adapted during the same sweep. The latter is also relevant in practice but saved for an expanded scope of work. All stencils considered here are "star stencils" of various spatial differential or truncation orders, where the stencil operator extends along one dimension at a time, without diagonal offsets. "Box stencils", "diamond stencils", and multicomponent stencils, in which multiple discrete fields interact on the same (or interlaced, staggered) lattices, are also important in practice, and can be handled with similar techniques.

The aforementioned issues put once-humble stencil evaluation in the cross-hairs of co-design and motivate our examination of several shared-memory (multi-core) and distributed-memory (message-passing) optimizations of a variety of stencils (see Code Listings 3.1, 3.2, 3.3, and 3.4, in Chapter 3) on state-of-the-art hardware. We are especially concerned with the degradation of memory bandwidth per core forecast at tomorrow's extreme scale. We test our techniques on a range of star-like stencils accommodating up to eighth-order, constant and variable coefficient (without on-the-fly recomputation), noting their salutary effects on memory pressure, power consumption, and obtainable performance, and noting the transition of hardware bottlenecks.

For the fundamental kernel of Cartesian lattice updates, this thesis merely scratches the surface of co-design. Pipelined or s-step Krylov solvers, time parallelism, and high-order temporal discretizations that are obtained by using the governing PDE to estimate high time derivatives from high space derivatives are all potentially stencil-expanding (and halo-expanding) decisions made at an upstream algorithmic stage. Their downstream consequences on stencil update performance and code balance can

be examined using the analyses and software tools introduced herein, but it remains to close the loop with analyses and tools that allow how to design the best discrete schemes in the first place.

#### 2.2 Contemporary computer processors

Computer processors usually have slow and large memory (main memory), where most or all of the application data lives, together with fast and small memory (cache memory) near the CPU to bridge the performance gap between the CPU and main memory. In the past decade, the frequency power wall forced processor designers to increase processor concurrency. More compute power is obtained by adding more CPUs instead of increasing the clock frequency of the processors. Modern processors usually have multiple levels of cache memory, with a trend of having private cache levels close to the CPUs and shared cache levels among groups of them.

One of the major challenges facing the applications is the increasing performance gap between the CPU and the memory bandwidth, as shown in Table 2.1. Stencil computations are among the important kernels that suffer from this issue. Naïve implementations of stencil computations leave the CPU idle a significant amount of time while waiting for data transfer with the main memory to complete.

The cache memory levels utilize temporal and spatial locality principles to bridge the performance gap between the memory and the CPU. Temporal locality relies on the fact that when a memory location is accessed, it is likely to be accessed again in the near future. That is, keeping the data in the cache memory makes consecutive accesses to it faster. Spatial locality relies on the fact that when a memory location is accessed, its neighbor is likely to be accessed in the near future. When the CPU request data from the main memory, its neighbor data is brought with it, to reduce the data transfer latency penalty. The cache memory size plays a significant role

| Processor [cores] | L3  | Cache<br>L2 | L1  | Mem. G<br>Theory | B/s [/core]<br>STREAM | Gflops/<br>Sec | Flops/<br>Byte |

|-------------------|-----|-------------|-----|------------------|-----------------------|----------------|----------------|

| E5-2680 [8]       | 20M | 256k        | 32k | 51.2             | 38 [4.8]              | 173            | 4.6            |

| E5-2695v2 [12]    | 30M | 256k        | 32k | 59.7             | 51 [4.3]              | 230            | 4.5            |

| E5-2699v3 [18]    | 45M | 256k        | 32k | 68               | 47 [2.6]              | 662            | 14.1           |

| IBM BG/Q [16]     | _   | 32M         | 16k | 42.6             | 29 [1.8]              | 205            | 7.1            |

| AMD 6380 [16]     | 16M | 1M          | 16k | 51.2             | 31.6 [2]              | 160            | 5.1            |

| KNC SE10P [61]    | _   | 512k*61     | 32k | 352              | 162 [2.7]             | 1060           | 6.5            |

| KNL (DRAM)        | _   | 2M/2-core   | _   | 100              | _                     | 3000+          | 30+            |

| KNL (MCDRAM)      | _   | 2M/2-core   | _   | 500              | _                     | 3000+          | 6+             |

Table 2.1: Contemporary processor characteristics, showing the trend of memory bandwidth decreasing per core.

in maintaining high data reuse near the processor to bridge the increasing gap with main memory bandwidth. Unfortunately, contemporary computer processors exhibit a trend of having fixed or smaller cache size per CPU, as shown in Table 2.1.

The latency of bringing the data from main memory to the CPU is another challenging factor to obtaining high performance. Hardware and software prefetching techniques alleviate this latency issue. Regular or contiguous memory access patterns are important to utilize the hardware prefetching units. Moreover, the hardware prefetching units of modern Intel processors stream the data within the boundaries of 4KiB Translation Lookaside Buffer (TLB) pages, making long contiguous memory accesses more important to utilize them.

In summary, careful optimization techniques are required to overcome the memory bandwidth and cache size limitations. This can be achieved through algorithms with higher data reuse in the cache memory, while maximizing the regular data access patterns for proper utilization of the prefetching units.

#### 2.3 Cache blocking

Typical scientific applications use larger grid size, on the order of GiBs, than a processor's cache memory, which is on the order of MiBs. In the "naïve" approach, the grid cells are updated in lexicographic order. Each grid cell update involves loading the neighbor grid cells to perform the stencil computation. This neighbor access results in loading the same data multiple times from main memory in each iteration, with no data reuse across iterations. As a result, "naïve" stencil computations are typically memory-bound due to their low flops/byte ratio [4].

Spatial blocking aims to maximize the in-cache data reuse within the same iteration of the grid sweep by changing the grid point update order. We describe an efficient spatial blocking strategy in details in Section 3.2.1. Temporal blocking alleviates the memory pressure by allowing even more in-cache data reuse, where several time step updates are performed to a grid point before evicting the data to main memory. We describe very efficient temporal blocking techniques from the literature, namely, wavefront and diamond blocking.

#### 2.3.1 Wavefront temporal blocking

We use the naïve update order of a 3-point stencil in one dimension to illustrate the algorithms described here, using the C language syntax:

```

for(t=0; t<T; t++) {

for(x=1; x<Nx-1; x++) {

A[(t+1)%2][x] = W1 * A[t%2][x] + W2 * (A[t%2][x-1] + A[t%2][x+1])

}}</pre>

```

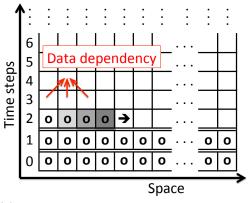

Figure 2.1a shows the naïve update order of this stencil. The fading gray color represents recently updated grid points, with the darkest assigned to the most recent update. The three "upward pointing" red arrows show the data dependency of each

(a) naïve: Lattice sites updated in chronological order, one time step at a time. Data dependencies example represented by the three "upward pointing" red arrows.

(b) Single thread wavefront traversal in space-time blocks. Wavefront tiles are updated sequentially.

(c) Multi-thread wavefront traversal in space-time blocks. The symbols/colors in the cells represent the update of different threads. Each thread updates one time step of the wavefront tile in this example. Extra spacing between the threads (i.e., steeper tile slope) allows concurrent update of the wavefront tile.

Figure 2.1: Different stencil update approaches for the 3-point stencil in one dimension. Fading gray boxes represent the last three updates.

grid point, which is important to consider at temporal blocking optimizations.

Wavefront temporal blocking is a well-known technique in the literature [5, 6, 7]. Compared to the naïve approach, the grid point update order maximizes the reuse of the most recently visited grid points while respecting the data dependencies. Figure 2.1b shows the basic idea of wavefront temporal blocking for the 3-point stencil in one dimension. Wavefront tiles traverse the space-time block in the direction of the arrows. The slope S of the wavefront tile is determined by the radius of the stencil operator R, where high-order (i.e., long-range) stencils require a smaller tile slope to respect the data dependency (S = -1/R). For example, the 3-point stencil, with stencil bandwidth unity, has S = -1. The data in the wavefront tile has to fit in the cache memory (along with the surrounding grid points accessed by the stencil operator) to achieve the desired cache memory data reuse in the wavefront approach. The time dimension block size controls the wavefront tile size to fit in the desired cache level. For example, three time steps are blocked in Figure 2.1b to illustrate the concept.

On multi-core systems one can perform single-thread wavefronts on separate spatial locations in the grid. There is no need (nor use) for any cache sharing among the threads, even if the hardware provides it. These concepts are described and implemented in [7, 8]. An explicitly multi-core aware wavefront scheme leveraging the shared cache among the threads was introduced in [9]. The wavefront tile update is pipelined over a group of threads sharing a cache memory level. This has the advantage of reducing the cache memory size requirements and allowing the use of larger cache blocks. As a result, the memory bandwidth pressure can be reduced compared to the single-thread wavefront. Fig. 2.1c shows the multi-thread wavefront variant proposed in [9], where each thread's update is assigned different symbol/color. Each thread is assigned to one or more consecutive time steps of the wavefront tile. To enable concurrent update in the wavefront tile, the slope of the wavefront is increased to

add spacing between the threads. For example, the additional cell spacing in Fig. 2.1c allows the three threads to update the wavefront tile concurrently. All threads have the same amount of work for load balancing, and they must be synchronized after each time step update to ensure correctness. A global barrier is the simplest solution for this, but a relaxed synchronization scheme may result in better performance if the workload per thread is small [10].

Combining the wavefront blocking scheme with other tiling techniques is essential in three-dimensional grids. Otherwise, using only the wavefront scheme in multiple dimensions would require much larger cache block size than typical cache sizes, when a reasonable grid size is used. Wavefront tiling is commonly combined with tiling approaches such as trapezoidal, parallelogram, or diamond tiling. These tiling approaches limit the tile size in other dimensions, such that the wavefront tile size fits in the desired cache memory. Since diamond tiling is proven to provide maximum the data reuse of a loaded spatial cache block [11], we describe it in greater detail in the next section.

Wavefront blocking is ideal when the block size in time is fixed by a different factor, for example, by the tiling approach in a different spatial dimension. By pipelining the data to the cache memory, the wavefront method loads each element once to the cache memory and performs the maximum time updates before evicting the results from the cache memory. On the other hand, loading data blocks separately and updating their elements by other tiling techniques would not allow maximum data reuse at the edges of the loaded block due to the data dependencies.

#### 2.3.2 Diamond tiling

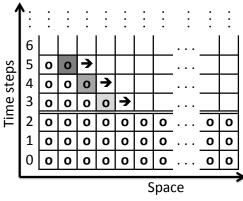

Diamond tiling has received much attention in recent years. Figure 2.2 shows the basic idea for the one-dimensional 3-point stencil. Arrows represent the data dependency across the diamond tiles. Diamond tiles that start at the same time step compose a

Figure 2.2: Diamond tiling on a one-dimensional space grid, with arrows representing inter-tile data dependencies. The number of diamond tiles per row represents the maximum attainable concurrency (i.e., concurrency limit), as the tiles in the row can be executed independently of each other.

"row of diamonds", in which the diamond tiles are independent of each other, hence can be updated concurrently. Each interior diamond tile has a data dependency on the two diamond tiles that share edges with it in the lower row of diamonds ("parents"). Sub-diamond tiles at the boundaries of the spatial domain have only one parent. The slope of the tile edges depends on the stencil radius, where  $S=\pm 1/R$ . In this work we consider diamond tile updates that do not perform synchronization with other tiles until the update is completed. Several advantages of diamond tiling make it favorable in shared memory systems: it maximizes the data reuse of the loaded data block [11], has low synchronization requirements, allows concurrent start-up in updating the diamond tiles, maintains high concurrency in transient state, and uses a unified tile shape, which simplifies the implementation.

# 2.4 Analytic and phenomenological performance modeling

Analytic performance models can answer the question what "good enough" performance means, in the sense that they predict the optimal performance of an algorithm and/or an implementation in view of the available resources. The Roofline model is a well-known example, whose principles date back into the 1980s [12] and which has received revived interest in the context of cache-based multi-core processor architectures in recent years [13]. It predicts the performance of "steady-state" loops or loop nests on a CPU, assuming that one of two possible bottlenecks apply: either the runtime is limited by the execution of instructions (execution bottleneck) or by the required data transfers through the memory hierarchy (data bottleneck), whichever takes longer. "Steady state" in this context means that start-up and wind-down effects are ignored, and that the CPU executes the same mix of instructions with the same data requirements for a long time. The assumptions behind the Roofline model are fulfilled for many algorithms in computational science that are either very data-bound or very compute-bound, i.e., whenever the data transfer and execution times differ strongly. Unfortunately, stencil algorithms with temporal blocking optimizations do not fall in this category, as we show in our results.

The ECM Model [14, 15] extends the Roofline model. In contrast to the latter, the ECM model does not assume perfect overlap between in-core and data transfer times. Instead, it assumes that the in-core execution time, i.e., the time required to execute a number of loop iterations with data coming from the L1 cache, is composed of an overlapping and a non-overlapping part. The CPU serializes the non-overlapping part with all transfer times between adjacent memory hierarchy levels down to where the data originally resided. We briefly review the model here. See [15] for more details.

The execution unit (pipeline) sets the in-core execution time  $T_{\text{core}}$  by taking the

largest number of cycles to execute the instructions for a given number of loop iterations. The non-overlapping part of  $T_{\rm core}$ , called  $T_{\rm nOL}$ , consists of all cycles in which a LOAD instruction retires. As all data transfers are in units of Cache Lines (CLs), we usually consider one "cache line's worth of work." With a double-precision stencil code, one unit of work is 8 iterations. The time for all data transfers required to execute the work unit is the "transfer time." The ECM model neglects the latency altogether, so the maximum bandwidth (cache lines per cycle) between adjacent memory hierarchy levels determines the cost for one CL transfer. For example, on the Intel Haswell architecture, one CL transfer takes one cycle between the L1 and L2 caches and two cycles between L2 and L3. Moving a 64-byte CL between memory and L3 takes 64 bytes  $\cdot f/b_{\rm S}$  cycles. Here f is the clock frequency of the CPU and  $b_{\rm S}$  is the fully saturated memory bandwidth.

If  $T_{\text{data}}$  is the transfer time,  $T_{\text{OL}}$  is the overlapping part of the core execution, and  $T_{\text{nOL}}$  is the non-overlapping part, then

$$T_{\text{core}} = \max(T_{\text{nOL}}, T_{\text{OL}})$$

and  $T_{\text{ECM}} = \max(T_{\text{nOL}} + T_{\text{data}}, T_{\text{OL}})$ . (2.1)

$T_{\text{data}}$  is the sum of the data transfer times through the memory hierarchy. If, for example, the data is in the L3 cache,  $T_{\text{data}} = T_{\text{L1L2}} + T_{\text{L2L3}}$ .

We use a shorthand notation for the cycle times in the model for executing a unit of work:  $\{T_{\text{OL}} \mid T_{\text{nOL}} \mid T_{\text{L1L2}} \mid T_{\text{L2L3}} \mid T_{\text{L3Mem}}\}$ . Adding up the contributions from  $T_{\text{data}}$  and  $T_{\text{nOL}}$  and applying (2.1) one can predict the cycles for executing the loop with data from any given memory level. For example, if the model is  $\{4 \mid |4| \mid 2 \mid 4 \mid 9\}$  cy, the prediction for L3 cache will be max (4, 4+2+4) cy = 10 cy. For predictions, we use "]" as the separator to present the information in a similar way as in the model. In the example above this would be  $T_{\text{ECM}} = \{4 \mid 6 \mid 10 \mid 19\}$  cy. It is easy to get from time to performance (work divided by time) by calculating the fraction  $P = W/T_{\text{ECM}}$ ,

where W is the work. If  $T_{\text{ECM}}$  is given in clock cycles but the unit of work is a LUP and the performance metric is LUP/s then we have to multiply by the clock speed.

For multi-core scalability, we assume that the performance is linear in the number of cores until the maximum bandwidth of a bottleneck data path is exhausted. On Intel processors the memory bandwidth is the only bottleneck. Hence, the absolute maximum performance is the Roofline prediction for memory-bound execution:  $P_{\rm BW} = I \cdot b_{\rm S}$ , with I being the computational intensity. Thus, the model allows us to predict the number of cores required to reach bandwidth saturation.