# POWER AND PERFORMANCE MODELING FOR HIGH-PERFORMANCE COMPUTING ALGORITHMS

A Thesis Presented to The Academic Faculty

by

Jee Whan Choi

In Partial Fulfillment

of the Requirements for the Degree

Doctor of Philosophy in the

School of Electrical and Computer Engineering

Georgia Institute of Technology May 2015

Copyright © 2015 by Jee Whan Choi

## POWER AND PERFORMANCE MODELING FOR HIGH-PERFORMANCE COMPUTING ALGORITHMS

## Approved by:

Professor Richard Vuduc, Committee Chair School of Computational Science and Engineering Georgia Institute of Technology

Professor Richard Vuduc, Advisor School of Computational Science and Engineering Georgia Institute of Technology

Professor George Riley School of Electrical and Computer Engineering Georgia Institute of Technology

Professor Sudhakar Yalamanchili School of Electrical and Computer Engineering Georgia Institute of Technology Professor David Bader School of Electrical and Computer Engineering Georgia Institute of Technology

Professor Linda Wills School of Electrical and Computer Engineering Georgia Institute of Technology

Professor Richard Fujimoto School of Computational Science and Engineering Georgia Institute of Technology

Date Approved: 27 March 2015

To my parents, for their sacrifice, dedication, and patience.

### ACKNOWLEDGEMENTS

First and foremost, I would like to thank my advisor, Dr. Richard Vuduc, for his support, encouragement and wisdom. He taught me the joys of research and I will solely miss the hours of discussions – which we never felt was enough – we had in his office. I can only hope to one day match his enthusiasm for research and his dedication to his students when I pursue a career in academia. His wisdom and patience that seem well beyond his years and his infectious enthusiasm in both the classroom and the research lab make him truly one–of–a–kind. I would also like to thank Agata for her support; she is most definitely an integral (and fun) part of being Rich's student.

I would also like to thank Dr. Scott Wills and Dr. Linda Wills. Scott and Linda were my Master's thesis advisors and they helped me through a very difficult time when I was making no progress on my research and was beginning to lose interest in it altogether; their patience, encouragement, and wisdom shaped me into the researcher that I am today, and for that I will forever be grateful. I greatly miss Scott's child–like energy and enthusiasm for research, and it is a great loss for the research community that he was taken away from us so prematurely.

I would like to thank the members of my Ph.D. thesis committee – Dr. George Riley, Dr. Sudhakar Yalamanchili, Dr. David Bader, and Dr. Richard Fujimoto – for their time and effort. I greatly appreciate all the valuable feedback I received during my defense, and hope to one day collaborate with and learn from them again. Among other faculty members at Georgia Tech, I would like to thank Dr. Edmond Chow and Dr. Hyesoon Kim in particular for their advice, encouragement, and feedback.

My time at Georgia Tech would not have been the same without other talented graduate students in our lab, especially Dr. Aparna Chandramowlishwaran, (soon to

be Dr.) Kenneth Czechowski, Dr. Xing Liu, Karl Jiang, Marat Dukhan, Piyush Sao, and David Noble. Without them, graduate school would not have been as enjoyable and memorable, and I thank them for all that I have learned from them, about both research and life in general. I will greatly miss the time I spent with them as a graduate student.

A special and loving thanks goes to my girlfriend Jeongmin Yun for waiting patiently for me in Korea for 8 years. This thesis would have have been possible without her emotional support and love.

Most of all, I want to thank my parents for their love and support throughout my unusually long graduate study. They have sacrificed greatly – not only during my time as a graduate student, but since the day I was born – to make my life better and I can never pay them back for all that they have done for me. Thank you so much.

## TABLE OF CONTENTS

| DE            | DIC  | ATION   | Variation ${f i}$                                                                    | ii |

|---------------|------|---------|--------------------------------------------------------------------------------------|----|

| AC            | KNO  | OWLE    | DGEMENTS i                                                                           | v  |

| LIS           | ST 0 | F TAB   | iLES i                                                                               | x  |

| LIS           | ST O | F FIG   | URES                                                                                 | x  |

| $\mathbf{SU}$ | MM.  | ARY .   |                                                                                      | ii |

| Ι             | INT  | RODU    | JCTION                                                                               | 1  |

|               | 1.1  | A Roo   | fline Model of Energy                                                                | 2  |

|               | 1.2  |         | thmic Time, Energy, and Power on Candidate High Perfor-<br>Computing Building Blocks | 4  |

|               | 1.3  | -       | ing the Energy Roofline Model for Dynamic Voltage and Fre-<br>Scaling                | 5  |

|               | 1.4  | Analys  | sis of the Fast Multiple Method Using the Energy Roofline Model                      | 7  |

| II            | PRI  | EVIOU   | JS WORK                                                                              | 9  |

|               | 2.1  | History | y                                                                                    | 9  |

|               | 2.2  | The P   | roblem                                                                               | 0  |

|               | 2.3  | Curren  | nt Research                                                                          | 1  |

| III           | ENI  | ERGY    | ROOFLINE MODEL                                                                       | 8  |

|               | 3.1  | A Basi  | c Model and its Interpretation                                                       | 9  |

|               |      | 3.1.1   | Algorithm characterization                                                           | 0  |

|               |      | 3.1.2   | Time and energy costs                                                                | 2  |

|               |      | 3.1.3   | Rooflines in time and energy                                                         | 6  |

|               |      | 3.1.4   | The balance gap                                                                      | 7  |

|               |      | 3.1.5   | Interpreting constant power                                                          | 8  |

|               | 3.2  | What    | the Basic Model Implies About Power                                                  | 9  |

|               | 3.3  | An exp  | periment                                                                             | 0  |

|               |      | 3.3.1   | Experimental Setup                                                                   | 0  |

|    |     | 3.3.2  | Intensity microbenchmarks                                                                         | 32 |

|----|-----|--------|---------------------------------------------------------------------------------------------------|----|

|    |     | 3.3.3  | Cache microbenchmarks                                                                             | 37 |

|    | 3.4 | Discus | sion, Application, and Refinement                                                                 | 41 |

|    |     | 3.4.1  | The fitted parameters                                                                             | 41 |

|    |     | 3.4.2  | Balance gaps and power caps                                                                       | 43 |

|    |     | 3.4.3  | Applying and refining the model: $FMM_U$ on the GPU $$                                            | 44 |

|    |     | 3.4.4  | Refining the performance estimate                                                                 | 45 |

|    |     | 3.4.5  | Constant power                                                                                    | 47 |

|    | 3.5 | Algori | thmic Trade-offs                                                                                  | 48 |

|    |     | 3.5.1  | Notation and key definitions                                                                      | 48 |

|    |     | 3.5.2  | A general "greenup" condition                                                                     | 49 |

|    |     | 3.5.3  | Time and energy relationships                                                                     | 50 |

|    |     | 3.5.4  | Summary of the three cases                                                                        | 53 |

|    |     | 3.5.5  | Time and Energy Trade-offs under Constant Power                                                   | 54 |

|    |     | 3.5.6  | Total energy, $E_{f,m}$                                                                           | 55 |

|    |     | 3.5.7  | Effective energy balance, $\hat{B}_{\epsilon}(I)$                                                 | 55 |

|    |     | 3.5.8  | Greenup, $\Delta E$                                                                               | 55 |

|    |     | 3.5.9  | General necessary condition for greenup                                                           | 55 |

|    |     | 3.5.10 | $\Delta E$ bounds for case 1: New algorithm is memory bound in time                               | 57 |

|    |     | 3.5.11 | $\Delta E$ bounds for case 2: baseline is memory bound but new algorithm is compute bound in time | 58 |

|    |     | 3.5.12 | $\Delta E$ bounds for case 3: baseline is compute bound in time                                   | 60 |

|    |     | 3.5.13 | Summary                                                                                           | 61 |

|    | 3.6 | Conclu | ision                                                                                             | 61 |

| IV |     |        | CHMIC TIME, ENERGY, AND POWER ON CANDIC COMPUTE BUILDING BLOCKS                                   | 63 |

|    | 4.1 | A Den  | nonstration                                                                                       | 64 |

|    | 4.2 | Model  | ing Power Cap                                                                                     | 66 |

|    | 4.3 | Experi | mental Setup and Microbenchmarks                                                                  | 69 |

|               | 4.4            | Result | s and Discussion                                         | 73        |

|---------------|----------------|--------|----------------------------------------------------------|-----------|

|               |                | 4.4.1  | Model fitting and accuracy                               | 73        |

|               |                | 4.4.2  | Interpreting memory hierarchy energy costs               | 75        |

|               |                | 4.4.3  | Constant power and power caps across platforms           | 76        |

|               |                | 4.4.4  | Power throttling scenarios                               | 79        |

|               | 4.5            | Conclu | asion                                                    | 80        |

| $\mathbf{V}$  |                |        | ORATING THE EFFECT OF DYNAMIC VOLTAGE ANI<br>NCY SCALING | )<br>84   |

|               | 5.1            | Model  | ing Dynamic Voltage and Frequency Scaling                | 85        |

|               | 5.2            | Exper  | imental Setup                                            | 88        |

|               |                | 5.2.1  | Hardware                                                 | 88        |

|               |                | 5.2.2  | Software                                                 | 90        |

|               |                | 5.2.3  | HPC candidate building block bake–off                    | 91        |

|               | 5.3            | Result | s and Discussion                                         | 96        |

|               |                | 5.3.1  | Fitting and Validation                                   | 96        |

|               |                | 5.3.2  | Autotuning for energy                                    | .00       |

|               | 5.4            | Conclu | asion                                                    | 02        |

| VI            |                | _      | ΓING THE FAST MULTIPOLE METHOD USING THE ROOFLINE MODEL  | 04        |

|               | 6.1            | Introd | uction to the Fast Multipole Method                      | .05       |

|               | 6.2            | Breaki | ing Down FMM                                             | .07       |

|               | 6.3            | Result | s and Observations                                       | .08       |

|               | 6.4            | Conclu | asion                                                    | 15        |

| VII           | COI            | NCLU   | SION                                                     | <b>17</b> |

| $\mathbf{RE}$ | $\mathbf{FER}$ | ENCE   | $2\mathbf{S}$                                            | 20        |

## LIST OF TABLES

| 1  | Summary of model parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 21  |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2  | Sample values for model parameters, based on best case (peak) capabilities of currently available systems. See table 1 for a summary of the definitions of these parameters                                                                                                                                                                                                                                                                                                                                                 | 23  |

| 3  | Platforms – TDP is Thermal design power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 31  |

| 4  | Fitted energy coefficients. Note that $\epsilon_{mem}$ is given in units of picoJoules per $Byte$ . As it happens, the $\pi_0$ coefficients turned out to be identical to three digits on GTX 580 and i7-950 which are built on 40 nm and 45 nm technologies respectively, whereas GTX 680 is built on a significantly lower technology of 28 nm                                                                                                                                                                            | 36  |

| 5  | Estimated energy costs of explicitly fetching data from L1 and L2 caches on GTX 580, and from shared memory and L2 on the GTX 680.                                                                                                                                                                                                                                                                                                                                                                                          | 41  |

| 6  | Platforms summary, with 9 systems and 12 distinct "platforms." We distinguish between manufacturer's peak (columns 3–5) and "sustained peak" using our microbenchmarks, shown parenthetically in columns 8–10. <i>Note 1</i> : In four cases, denoted by an asterisk ("*"), our fitted constant power is less than observed idle power. <i>Note 2</i> : Some data are missing; double precision support is not available on all platforms and deficiences in the OpenCL driver prevented some microbenchmarks from running. | 71  |

| 7  | List of settings and derived energy costs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 99  |

|    | 3,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 99  |

| 8  | Summary of autotuning results. "Energy lost" shows how much <i>more</i> energy the configuration chosen by our model or the "time oracle" dissipated when compared to experimentally measured minimum                                                                                                                                                                                                                                                                                                                       | 100 |

| 9  | Summary of counter events and metrics used to create a breakdown of the FMM kernel. Type "E" are events and type "M" are metrics                                                                                                                                                                                                                                                                                                                                                                                            | 109 |

| 10 | Summary of DVFS settings and input parameters used for validation                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 111 |

## LIST OF FIGURES

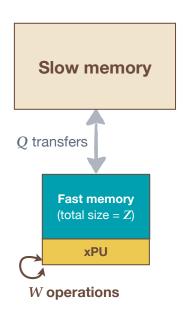

| 1 | A simple von Neumann architecture with a two-level memory hierarchy. In our first analysis, suppose that an algorithm performs $W$ arithmetic operations and $Q$ memory operations, or "mops," between slow and fast memories                                                                                                                                                                                                                                    | 19 |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

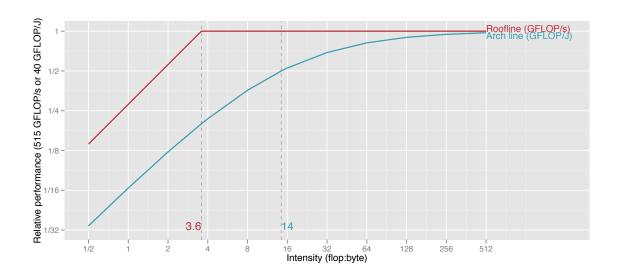

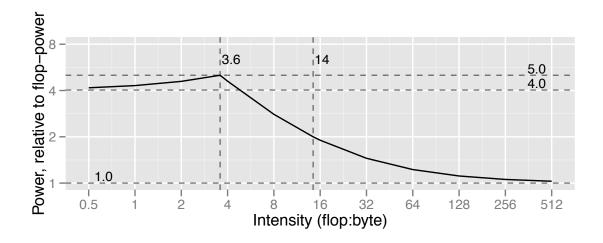

| 2 | Rooflines in time, arch lines in energy, and power lines. Machine parameters appear in table 2, for an NVIDIA Fermi-class GPU assuming constant power is 0. Dashed vertical lines show time- and energy-balance points                                                                                                                                                                                                                                           | 24 |

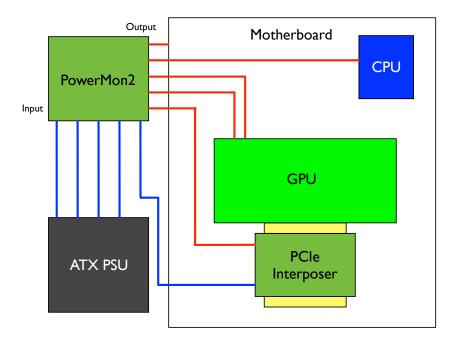

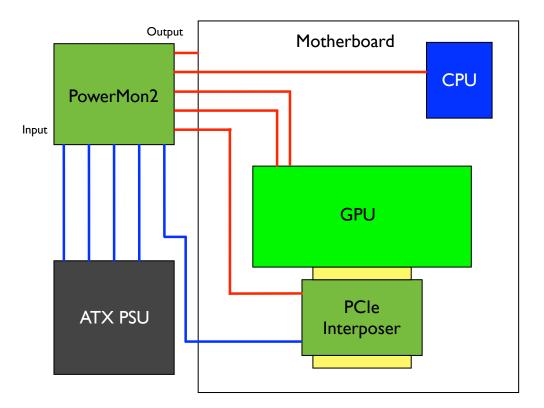

| 3 | Placement of the measurement probes, PowerMon 2 [8] and our custom PCIe interposer                                                                                                                                                                                                                                                                                                                                                                               | 32 |

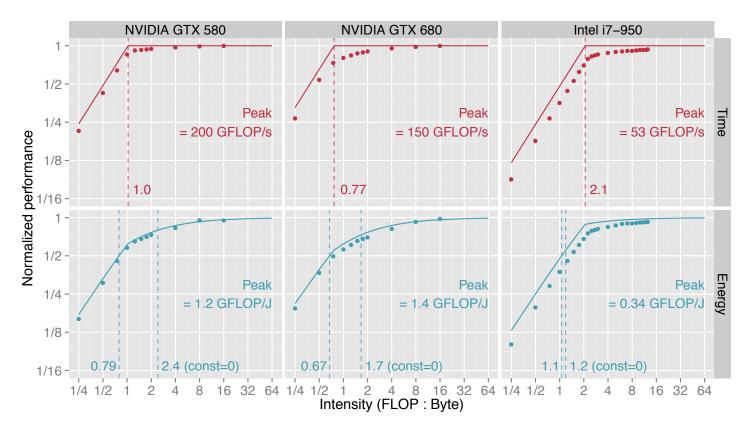

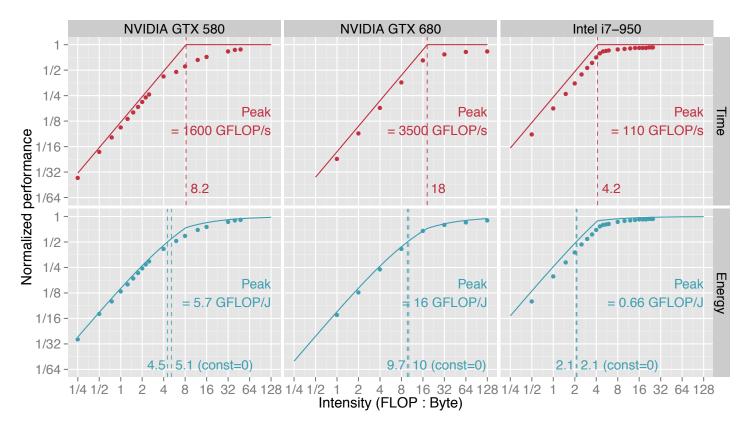

| 4 | Measured time and energy for a double-precision synthetic benchmark corroborates eqs. (3) and (5). The impact of constant energy can be profound: GPUs have $\hat{B}_{\epsilon} < B_{\tau} < B_{\epsilon}$ (see vertical dashed lines). In other words, time efficiency implies energy efficiency because of constant power, which further suggests that "race-to-halt" is a reasonable energy-saving strategy; were $\pi_0 \to 0$ , the situation could reverse | 33 |

| 5 | Same as fig. 4, but for single precision. In this case, all platforms have $\hat{B}_{\epsilon} \leq B_{\epsilon} < B_{\tau}$                                                                                                                                                                                                                                                                                                                                     | 34 |

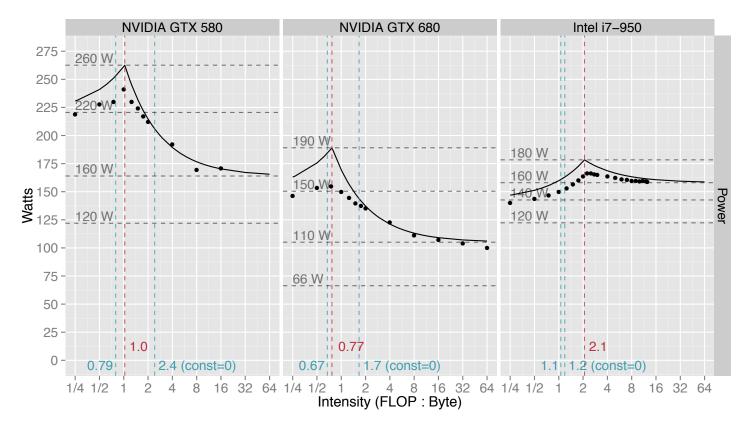

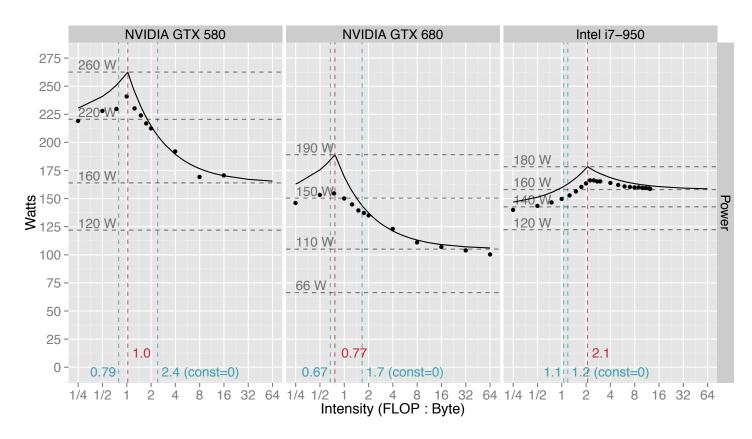

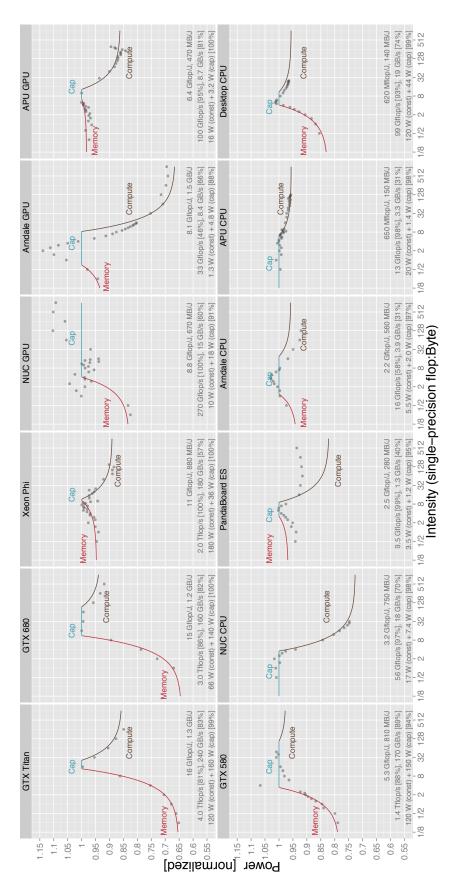

| 6 | Measured power for the double-precision microbenchmark corrobo-<br>rates the "powerline" model. On the GTX 580 platform, NVIDIA<br>reports a limit of 244 Watts, which explains the discrepancy between<br>the observed data and the predicted powerline in the single-precision<br>GTX 580 case                                                                                                                                                                 | 38 |

| 7 | Measured power for the single-precision microbenchmark                                                                                                                                                                                                                                                                                                                                                                                                           | 39 |

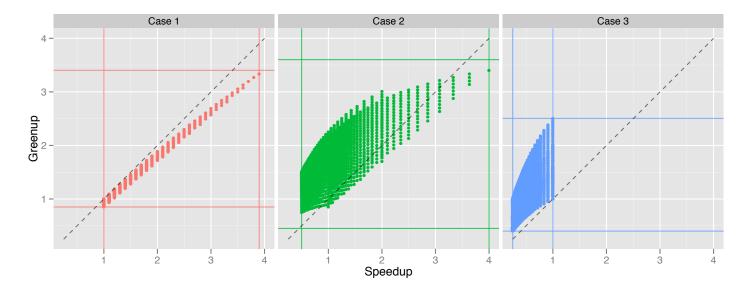

| 8 | Illustration of the speedup and greenup bounds summarized in § 3.5.4. Points correspond to $(\Delta T, \Delta E)$ pairs at particular values of $I$ , $f$ , and $m$ ; horizontal and vertical lines indicate the corresponding minimum lower bounds and maximum upper bounds on speedup and greenup, taken over all values of $I$ , $f$ , and $m$ in each case                                                                                                   | 54 |

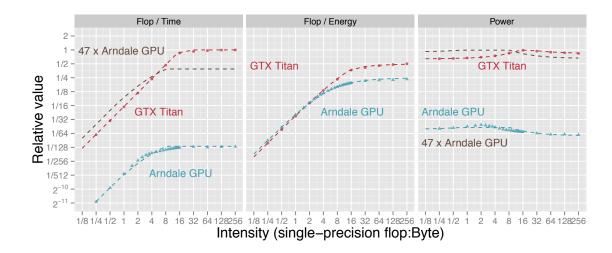

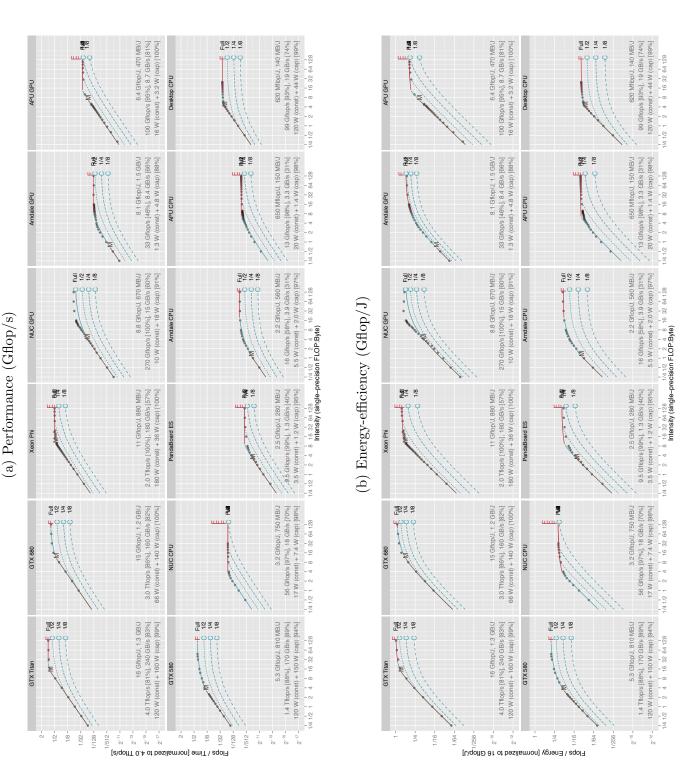

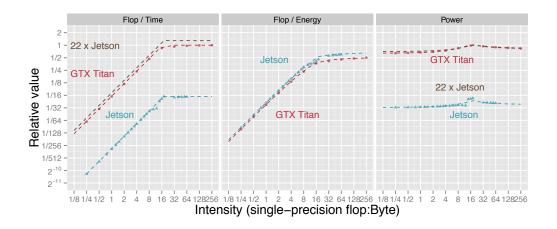

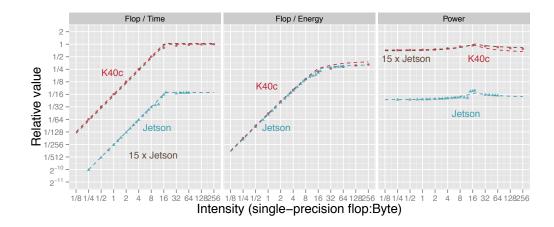

| 9  | Comparison of the time efficiency (performance), energy efficiency, and power required by a mobile GPU (from an "Arndale" Samsung Exynos 5 developer board) versus high-end gaming-grade desktop GPU (NVIDIA GTX Titan), over a range of synthetic computations with varying computational intensities (flop:Byte). Combining 47 of the mobile GPUs to match on peak power can lead to a system that outperforms the desktop GPU by up to 1.6× for relatively bandwidth bound codes (flop:Byte less than 4), but at the cost of sacrificing peak performance (less than ½) for compute-bound codes | 65  |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 10 | Placement of the measurement probes, PowerMon 2 and our custom PCIe interposer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 72  |

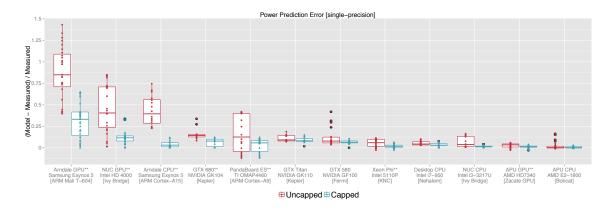

| 11 | Summary of modeling errors with respect to performance (FLOP/s). We compare the prediction errors of our prior model ("free" or uncapped; [25, 26]; § 3.1) against our new model ("capped"), which notably includes an explicit power cap. Qualitatively, the distribution of errors on all platforms improves, becoming either lower in median value or more tightly grouped. On platforms labeled by double-asterisks ("**"), the free and capped distributions differ statistically (at $p < .05$ ) by the Kolmogorov-Smirnov test [77]                                                         | 74  |

| 12 | Power (normalized). The y-axis is linear but the x-axis is logarithmic, base 2. The model appears as solid lines in up to three segments, indicating the three possible regimes: memory bandwidth bound, power bound due to capping, and compute bound. Measurements appear as solid grey dots. Platforms appear from left-to-right and top-to-bottom in decreasing order of peak energy efficiency, i.e., the most energy efficient platform is the GTX Titan, whose peak is 16 Gflop/J.                                                                                                          | 77  |

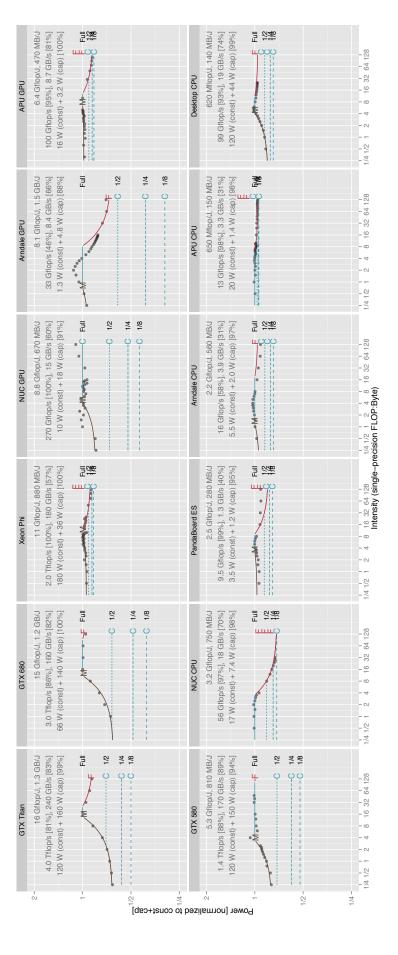

| 13 | Hypothetical power, performance, and energy efficiency as the usable power cap $(\Delta \pi)$ decreases. Note the log-log scales, base 2. Each curve represents a power cap setting: full refers to $\Delta \pi$ from table 6 and $1/k$ refers to a power cap setting of $\Delta \pi/k$ , for $k \in \{2,4,8\}$ . The curve color annotations, "F" for flop bound (compute bound), "C" for power cap bound, and "M" for memory bound                                                                                                                                                               | 82  |

| 14 | Hypothetical performance and energy efficiency as the usable power cap $(\Delta \pi)$ decreases. This figure uses same plotting and notation conventions as fig. 13                                                                                                                                                                                                                                                                                                                                                                                                                                | 83  |

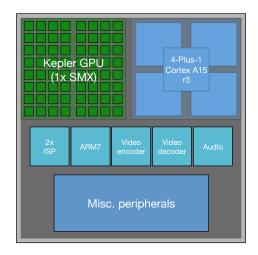

| 15 | Schematic of the NVIDIA Tegra K1 mobile processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 89  |

| 16 | $22 \times$ Jetson TK1 vs. GTX Titan                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 94  |

| 17 | $15\times$ Jetson TK1 vs. Tesla K40c                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 96  |

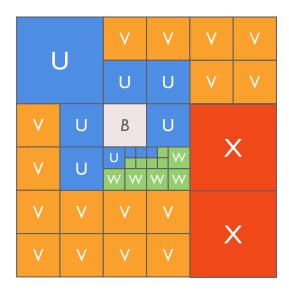

| 18 | U V W and X lists of a tree node B for an adaptive quadtree                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 106 |

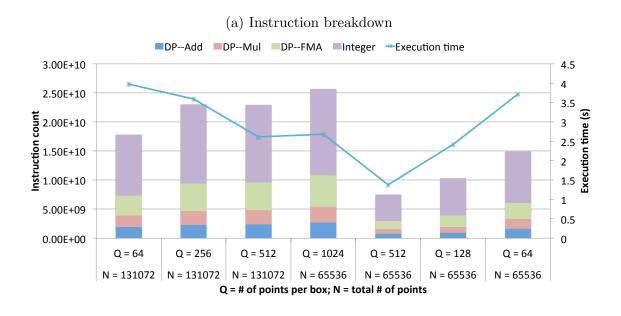

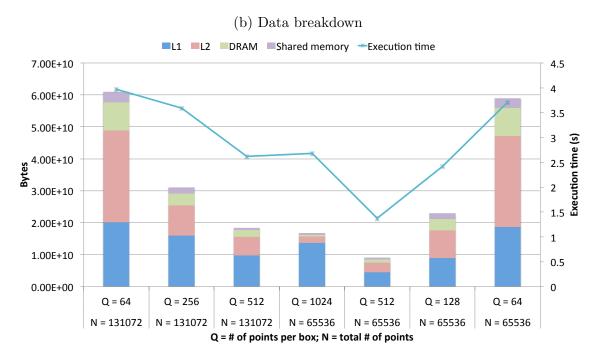

| 19 | Breakdown of the FMM kernel to component instructions and data access to different levels of the memory hierarchy                                                                                 | 110 |  |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|

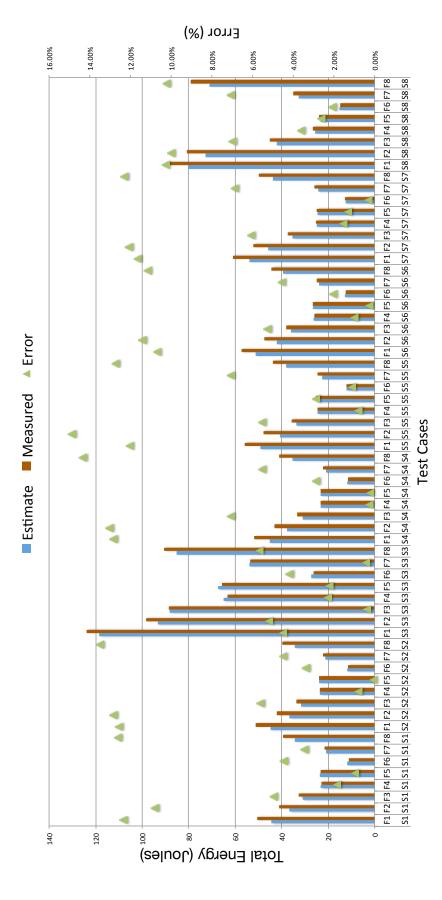

| 20 | Comparison of estimate vs. measured energy for various test cases                                                                                                                                 | 112 |  |

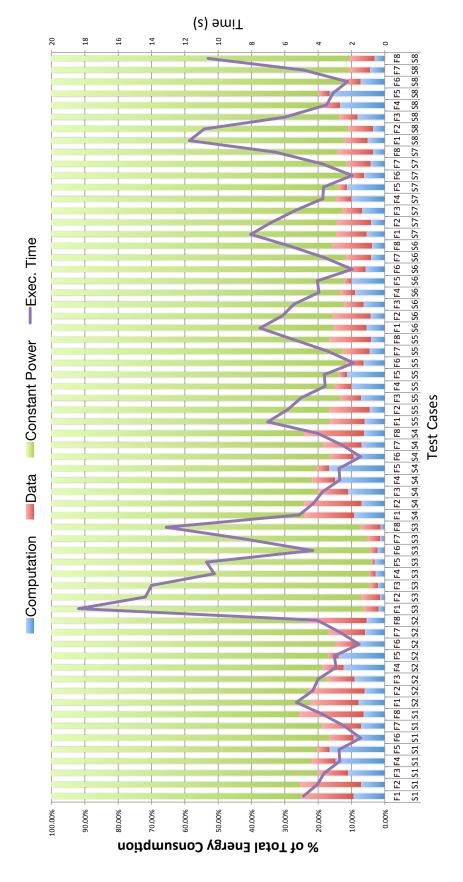

| 21 | Breakdown of energy consumption by three types: energy spent on computation (incl. integer operations), data movement (from all levels of the memory hierarchy), and constant power (or overhead) | 114 |  |

#### SUMMARY

The overarching goal of this thesis is to provide an algorithm-centric approach to analyzing the relationship between time, energy, and power. This research is aimed at algorithm designers and performance tuners so that they may be able to make decisions on how algorithms should be designed and tuned depending on whether the goal is to minimize time or to minimize energy on current and future systems.

First, we present a simple analytical cost model for energy and power. Assuming a simple von Neumann architecture with a two-level memory hierarchy, this model predicts energy and power for algorithms using just a few simple parameters, such as the number of floating point operations (FLOPs or flops) and the amount of data moved (bytes or words). Using highly optimized microbenchmarks and a small number of test platforms, we show that although this model uses only a few simple parameters, it is, nevertheless, accurate.

We can also visualize this model using energy "arch lines," analogous to the "rooflines" in time. These "rooflines in energy" allow users to easily assess and compare different algorithms' intensities in energy and time to various target systems' balances in energy and time. This visualization of our model gives us many interesting insights, and as such, we refer to our analytical model as the *energy roofline model*.

Second, we present the results of our microbenchmarking study of time, energy, and power costs of computation and memory access of several candidate compute-node building blocks of future high–performance computing (HPC) systems. Over a dozen server-, desktop-, and mobile-class platforms that span a range of compute and power characteristics were evaluated, including x86 (both conventional and Xeon Phi

accelerator), ARM, graphics processing units (GPU), and hybrid (AMD accelerated processing units (APU) and other system—on—chip (SoC)) processors.

The purpose of this study was twofold; first, it was to extend the validation of the energy roofline model to a more comprehensive set of target systems to show that the model works well independent of system hardware and microarchitecture; second, it was to improve the model by uncovering and remedying potential shortcomings, such as incorporating the effects of power "capping," multi–level memory hierarchy, and different implementation strategies on power and performance.

Third, we incorporate dynamic voltage and frequency scaling (DVFS) into the energy roofline model to explore its potential for saving energy. Rather than the more traditional approach of using DVFS to reduce energy, whereby a "slack" in computation is used as an opportunity to dynamically cycle down the processor clock, the energy roofline model can be used to determine *precisely* how the time and energy costs of different operations, both compute and memory, change with respect to frequency and voltage settings. This information can be used to target a specific optimization goal, whether that be time, energy, or a combination of both.

In the final chapter of this thesis, we use our model to predict the energy dissipation of a real application running on a real system. The fast multipole method (FMM) kernel was executed on the GPU component of the Tegra K1 SoC under various frequency and voltage settings and a breakdown of instructions and data access pattern was collected via performance counters. The total energy dissipation of FMM was then calculated as a weighted sum of these instructions and the associated costs in energy. On eight different voltage and frequency settings and eight different algorithm—specific input parameters per setting, for a total of 64 total test cases, the accuracy of the energy roofline model for predicting total energy dissipation was within 6.2%, with a standard deviation of 4.7%, when compared to actual energy measurements.

Despite its simplicity and its foundation on the first principles of algorithm analysis, the energy roofline model has proven to be both practical and accurate for real applications running on a real system. And as such, it can be an invaluable tool for algorithm designers and performance tuners with which they can more precisely analyze the impact of their design decisions on both performance and energy efficiency.

## CHAPTER I

## **INTRODUCTION**

## Contents

| 1.1 | A Roofline Model of Energy                                                                   | 2 |

|-----|----------------------------------------------------------------------------------------------|---|

| 1.2 | Algorithmic Time, Energy, and Power on Candidate  High Performance Computing Building Blocks | 4 |

| 1.3 | Adapting the Energy Roofline Model for Dynamic Voltage and Frequency Scaling                 | 5 |

| 1.4 | Analysis of the Fast Multiple Method Using the Energy  Roofline Model                        | 7 |

The overarching goal of this thesis is to develop a simple explanation, aimed at algorithm designers and performance tuners, about the relationship between time, energy, and power. For that audience, a useful model would directly connect properties of an algorithm – such as concurrency and locality – with architectural time and energy costs. It would explain whether there is any difference in optimizing an algorithm for time versus optimizing for energy, why such difference exist, and what properties of the architecture might lead to non–trivial time–energy trade–offs.

## 1.1 A Roofline Model of Energy

To address this challenge, we start from a simple analytical model grounded in the first principles of algorithm analysis. Our analysis is inspired by a similar set of thought experiments based on "Amdahl" analysis written by and for architects [59, 128, 133]. Such analyses, based on Amdahl's Law [3], offer architectural insights, but abstract away essential properties of an algorithm. By contrast, our analysis more explicitly connects algorithmic and architectural parameters. However, for clarity we pose and study an intentionally simple – but not overly so – model, with some initial experimental tests to confirm its basic form. Our analytical model is known as the energy roofline model, and below, we summarize what our model implies. These claims both reflect familiar intuition and also yield new or alternative explanations about time, energy, and power relationships.

First, when analyzing time, the usual first-order analytic tool is to assess the balance of the processing system [80, 60, 61, 12, 89, 126], where balance is the ratio of work (e.g., flops) the system can perform per unit of data transfer (e.g., bytes). To this notion of time-balance, we define an energy-balance analogue, which measures the ratio of flops and bytes per unit of energy (e.g., Joules). We compare balancing computations in time against balancing in energy.

Second, we use energy—balance to develop an energy—based analogue of the time—based roofline model [126], which can be used to visualize our model. Because time can be overlapped, while energy cannot, the energy—based "roofline" (hence, the name energy roofline model) is actually a smooth "arch line." Interestingly, if time—balance differs from energy—balance, then there are distinct notions of being "compute bound" versus "memory bound," depending on whether the optimization goal is to minimize time or to minimize energy. We can measure this difference as a time—energy balance gap. We also posit an analogous "powerline" model for power.

Third, when a balance gap exists and energy-balance exceeds time-balance, the

arch line predicts that optimizing for energy may be fundamentally more difficult than optimizing for time. It further suggest that high algorithmic energy efficiency may imply time efficiency, while the converse – that time efficiency implies energy efficiency – is not true.

Fourth, we test the basic form of the model using experiments on real CPU and GPU platforms. Using our model and these data, we show that the hypothetical balance gap described above does not yet really exist, which consequently explains why on today's platforms race—to—halt is likely to work well [6]. This raises the question for architects and hardware designers about what the fundamental *trends* in the balance gap will be: if energy—balance will eventually overtake time—balance, race—to—halt could break. We further use the experiments to highlight both the strengths and the limitations of our model and analysis.

Lastly, we ask under what general conditions we should expect an algorithmic time–energy trade–off. "Algorithmic" here stands in contrast to "architectural." Architecturally, for instance, increasing frequency reduces time, but increases energy, due to the non–linear relationship between frequency and power. What is the story for algorithms? We consider one scenario. Suppose it is possible algorithmically to trade more compute operations for less communication. One may derive a general necessary condition under which such a trade–off will improve energy efficiency. Furthermore, we show what improvements in energy efficiency may or may not require a slowdown, and by how much. Again, these conditions depend fundamentally on how time–balance compares to energy–balance.

Taken together, these theoretical analyses, supported by experiments on real platforms, can be used to improve the collective understanding of the relationship among algorithm properties and their costs in time, energy, and power.

## 1.2 Algorithmic Time, Energy, and Power on Candidate High Performance Computing Building Blocks

In this section, we extend and further validate the energy roofline model to increase its accuracy and usability. We claim three key contributions.

First, we add several important components to our model. These components include explicit modeling of a power cap and the energy cost of accessing different levels of the memory hierarchy. The power cap is especially significant, as it implies a way to predict power—throttling requirements. That is, if we wish to keep average power below some threshold, the model predicts by how much compute and memory operations should slow down. These additions come as a direct result of validating the model on real systems, where we discovered that certain systems operate under a strict power budget, and a power "cap" prevented them from achieving the expected peak performance. We also discovered that without individually accounting for the cost of accessing different levels of the memory hierarchy, it was difficult to predict energy consumption accurately for a real application.

Second, we compare the model to measurements on 12 platforms. These include x86 (both conventional, and Xeon Phi accelerators), several flavors of ARM, desktop and mobile GPUs and accelerated processing units (or APUs, such as those from AMD and other system—on—chip (SoC) manufacturers). These experiments validate the basic form of the *extended* model and yield empirical estimates of the effective energy required to perform flops and to move data. Breaking down the energy costs to these different components allows us to consider energy efficiency at different arithmetic intensity points, allowing more flexibility and analytical precision than simply dividing, say, peak performance by thermal design power (TDP). Moreover, these basic estimated constants may in and of themselves be useful reference values.

The microbenchmarks used in these measurements have been carefully tuned with the necessary architectural details in mind, in order to properly stress the targeted operations. These benchmarks, including the ones used in the previous section, have been written in an array of programming environments, including assembly [66], C (with SIMD intrinsics), CUDA [99], and OpenCL [2]. We have made these microbenchmarks available for download in a public repository as part of this thesis <sup>1</sup>.

We claim our analysis and conclusion, drawn from the extensive experimental data collected from a dozen systems, as our final contribution. It includes comparing platforms on how power is allocated between memory and processing and the potential for reconfiguring power between memory and processing to improve or adapt energy efficiency to computation. It also includes comparing platforms for power throttling scenarios, where the "usable" power (i.e., power dedicated to computation and data movement, not including overhead) is reduced to satisfy a power budget and how such action impacts performance.

Beyond specific findings and data, we emphasize the methodological aspect of this section. In particular, architects may find our high–level approach to be a useful additional way to assess systems across computations; our analysis technique aims to provide more insight than a collection of blackbox benchmarks provides but without having to know too much detail about the specific computation. Similarly, we hope algorithm designers may find ways to reason about algorithmic techniques for managing energy and power, and trade–offs, if any, against time.

# 1.3 Adapting the Energy Roofline Model for Dynamic Voltage and Frequency Scaling

So far, we have assumed a fixed cost for all operations, in both time, and energy. This allowed us to keep our model and analysis simple and easy to understand; however, in more practical settings, DVFS can have a strong impact on energy efficiency by taking advantage of superlinear reduction in power with reduced frequency (and therefore

<sup>&</sup>lt;sup>1</sup>http://hpcgarage.org/archline

voltage). We incorporate DVFS into the energy roofline model and validate it on a unique new SoC from NVIDIA.

We consider DVFS differently from how other have done in the past in that, rather than focusing on predicting "slack" in computation as an opportunity to arbitrarily lower frequency and voltage, we attempt to determine precisely by how much performance and energy of different operations change. Our new model can predict what the optimal frequency and voltage settings are for different computations, and tell us which algorithm would be better suited for a particular application under different constraints, such as a power cap. We show that our model is accurate to within 6.56% using 16–fold cross validation of our experimental data and to within 2.87% using the holdout method (2–fold cross validation).

We also evaluate and compare our new test platform, Jetson TK1, based on the Tegra K1 SoC which combines a single CUDA–capable SMX with a ARM Cortex A15 CPU, to high–end GPUs. Jetson TK1 is unique in that it is one of the first low–power platforms that can run scientific kernels and applications written in CUDA, and also in that it can vary frequency and voltage of both its processors and memory over a wide range, making it an ideal platform for DVFS studies.

We first compare Jetson TK1 to a GTX Titan, the highest—end desktop GPU from NVIDIA. In an iso—energy comparison, where we scale up the number of Jetson TK1 systems so that the aggregate TDP matches that of a single GTX Titan, we show that a 22× Jetson TK1 "cluster" outperforms GTX Titan over all arithmetic regimes in both performance and energy efficiency. When compared to a Tesla K40c GPU, the latest server—grade GPU, a cluster of 15× Jetson TK1 systems closely matches K40c in both performance and energy efficiency. Our study suggests that despite efforts in pushing mobile SoC for HPC [108, 106, 52], there is nothing fundamentally more, or less, energy efficient about low—power devices; that is, you get (in performance) what you pay for (in power).

## 1.4 Analysis of the Fast Multiple Method Using the Energy Roofline Model

As the final chapter of this thesis, we apply the energy roofline model to predicting the energy consumption of a real application on a real system. We target the fast multipole method (FMM) running on the CUDA–capable GPU of a Jetson TK1 system.

Given a system of N source particles, with positions given by  $\{y_1, \ldots, y_N\}$ , and N targets with positions  $\{x_1, \ldots, x_N\}$ , we wish to compute the N sums,

$$f(x_i) = \sum_{j=1}^{N} K(x_i, y_i) \cdot s(y_j), \quad i = 1, \dots, N$$

where f(x) is the desired potential at target point x; s(y) is the density at source point y; and K(x,y) is an interaction kernel that specifies "the physics" of the problem. For instance, the single-layer Laplace kernel,  $K(x,y) = \frac{1}{4\pi} \frac{1}{||x-y||}$ , might model electrostatic or gravitational interactions.

Evaluating these sums appears to require  $O(N^2)$  operations. The FMM instead computes approximations of all of these sums in optimal O(N) time with a guaranteed user-specified accuracy  $\epsilon$ , where the desired accuracy changes the complexity constant [54]. As such, FMM is used in a variety of scientific simulations including electromagnetic, fluid, and gravitational phenomena [14], and has been hypothesized to be of increasing importance on future exascale systems [131].

We begin our analysis by using *nvprof*, a command–line performance counter monitor provided by NVIDIA, to break down the FMM kernel to its basic operations. These operations include various floating point instructions, such as fused–multiply–add (FMA), multiply, and add, as well as integer operations, which are typically used for loops and address calculation. We also break down data access to different levels of the memory hierarchy; for GPUs these are accesses to shared memory, L1 cache, L2 cache, and main memory.

Once we have this breakdown, we simply take a weighted sum of these operations with the derived energy costs (§ 5.1–5.3) to get the final energy consumption estimate. To get the energy dissipated by constant power,  $\pi_0$ , we also need the execution time of the kernel. Although we use measured execution time in our validation, we could use the modeling and analysis technique developed in our previous work [20, 23] to get a time estimate as well. The FMM implementation used in this section is also from our previous work [20, 23], where we developed a highly tuned CPU–GPU hybrid implementation of FMM.

For validation, we take eight different voltage and frequency settings and run eight different configurations of FMM for each setting, and then compare our energy estimates with physical measurements. We observed a mean error of 6.17% and a standard deviation of 4.65%. We found that although we use very basic operations to represent our algorithm, our model can, nevertheless, yield an accurate estimate of energy consumption under various DVFS settings.

## **CHAPTER II**

## PREVIOUS WORK

#### Contents

| 2.1 | History          | 9  |

|-----|------------------|----|

| 2.2 | The Problem      | 10 |

| 2.3 | Current Research | 11 |

## 2.1 History

This is not the first time that power and cooling concerns have been raised in the history of computing. As early as 1947, ENIAC, which is considered to be the first digital computer, dissipated 174 KW using 17,468 vacuum tubes [11], a considerable amount of power considering its capability (or lack thereof). Although it consumed a large amount of power, cooling was not such a difficult problem because of the large physical size of a vacuum tube (i.e., areal power density, or watts per unit area, was relatively low).

Transition to relatively lower-power bipolar junction transistor (BJT) kept power dissipation in check. For example, the Intel 4004, the first commercially available microprocessor, was produced in 1971 and had a similar compute capability as the ENIAC while only dissipating a few watts. However, during the 1980s increasingly denser transistor integration led to a rapid rise in power dissipation and density. Power delivery and cooling once again became a concern and companies such as IBM

and Cray produced liquid-cooled supercomputers in order to meet high performance targets [78].

In the early 1990s transition from bipolar to complementary metal-oxide-semiconductor (CMOS) transistors once again brought a temporary relief from power challenges. CMOS transistors had the appealing behavior of dissipating power only during switching transitions. The complementary gate structure meant that early gates drew little or no current between transition points because in a stable state the gate has no clear path to ground. Although some initially considered CMOS too slow for widespread use in high–performance computing, when power concerns became too great to deal with, widespread adoption of CMOS brought technology improvements that significantly improved their performance.

#### 2.2 The Problem

Initially, most of the power dissipated by CMOS transistors came from switching (this is known as *dynamic* power). Due to the imperfect nature of transistors, there was also some *leakage* of current even when the transistor was not switching, or "turned off" (i.e. the supply voltage was below some threshold voltage). At first, this contributed only an insignificant amount of power (this is known as *leakage* or *static* power).

For decades, supply voltage dropped steadily with each technology generation [65, 64, 67] and because of its cubic influence on dynamic power, processor designers were able to keep the overall areal power density in check. However, when supply voltage is lowered, gate delay increases, and therefore the threshold voltage has to be lowered as well in order to maintain performance. Unfortunately, lowering threshold voltage has an *exponential* influence on leakage power; since no exponential can last forever, what was initially insignificant now makes up a significant proportion of the total power budget. Moreover, there is a limit to how low the threshold voltage can be set

and once this limit is reached, changing supply voltage can only trade off power for performance, and scaling performance and maintaining constant areal power density will no longer be feasible. That is, more performance will necessarily mean more power consumption.

For future supercomputers, operational costs of powering and cooling the system are expected to exceed the cost of building them. Currently, the most "green" supercomputer in the world is the L-CSC supercomputer at the GSI Helmholtz Center for Heavy Ion Research which consists of Intel Xeon CPUs and AMD FirePro GPUs and is capable of processing 5.3 GFLOPs for every watt of power [53]. However, the next generation of supercomputers, expected to come into service around 2018 and perform at Exa-FLOPS levels, has been capped at 20 MW in power [42]. This is approximately equivalent to performing at 50GFLOPS/W. So, in order to build the next generation of supercomputers, the research community must come up with a way to improve power efficiency by a factor of 10 within the next few years! Considering that we have already hit a wall, this is a daunting task.

#### 2.3 Current Research

The perspective of this work is algorithms, rather than architecture, systems, or embedded software, where time, power, and energy are traditionally studied (see the survey of Kaxiras et al. [72].) Our work is perhaps most similar to a recent work by Demmel et al. [34, 33, 49]. However, our model is more parsimonious and, as such, clarifies a number of issues such as the notion of a balance gap or why race-to-halt works on current systems. At a more technical level, we also differ in that we assume computation-communication overlap and have furthermore tried to validate the basic form of our model with experiments.

Additional algorithmic theory work The algorithms community has also considered the impact of energy constraints, particularly with respect to exploiting

scheduling slack and there have been numerous other attempts to directly explore the impact of energy constraints on algorithms. These include new complexity models, including new energy-aware Turing machine models [121, 88, 68, 10]; this body of work addresses fundamental theoretical issues but is hard to operationalize for practical algorithm design and tuning. Other algorithmic work takes up issues of frequency scaling and scheduling [79, 5, 4]. Such models are particularly useful for exploiting slack to reduce energy by, for instance, reducing frequency of non-critical path nodes.

Systems-focused frequency scaling In more practical software-hardware settings, the emphasis is usually on reducing energy usage through Dynamic Voltage and Frequency Scaling (DVFS). DVFS attempts to minimize energy consumption with little or no impact in performance by scaling down the frequency (and therefore the voltage) when processor speed does not limit performance [47, 44, 71, 46, 114, 84, 1]. This work suggests a different flavor of time-energy trade-off, which comes from the superlinear scaling of power and energy with frequency, than what we consider in this paper. Among these, the work by Lively et al. uses principle component analysis (PCA) method to model execution time and power consumption using a small set of performance counters, which is then used to determine the appropriate DVFS and dynamic concurrency throttling (DCT) settings. It is, however, not explicit about algorithmic features such as intensity.

Dynamic concurrency throttling is a technique that limits the number of active cores to reduce energy consumption [27, 19, 28, 74], and is particularly effective when employing an additional core brings a limited performance improvement but a significant increase in power. This technique is, like DVFS, system–centric and does not provide algorithmic insight into energy efficiency.

Microbenchmarking studies Kestor et al. [75] and Molka et al. [93] have developed a microbenchmarking methodology similar to our own. In particular, Kestor et

al. focus on measuring energy costs due to the memory hierarchy and communication. Our modeling approach differs, with power caps being its most notable distinction.

Diop et al. present a microbenchmark—based modeling technique for chip multiprocessors (CMP) and AMD APUs [35]. However, unlike ours, the microbenchmarks used in their work are not explicit about algorithmic properties and their methodology requires additional performance information from the Multi2Sim simulator [122] and performance monitoring counters (PMC).

Czechowski et al. also use microbenchmarks to evaluate a set of Intel CPUs that span a range of microarchitecture and process technology generations [31]. The authors demonstrate that various microarchitectural improvements in recent generations of Intel processors, and subsequent increase in the complexity of these "big cores," have contributed to improving both performance and energy efficiency. Their work is more focused on processor comparison than modeling, and is specific to only Intel processors.

Profiling and observation-based studies There are a number of empirical studies of time, power, and energy in a variety of computational contexts, such as linear algebra and signal processing [36, 43, 16, 48, 86, 41, 37, 13, 56]. One notable example is the work of Dongarra et al., which observes the energy benefits of mixed precision [36]; another is the study by Blem et al. [13] that debunks the myth that complex instruction set computing (CISC) instructions are inherently less energy efficient than reduced instruction set computing (RISC) instructions.

Esmaeilzadeh et al. measure chip power for a variety of applications, with a key high-level finding being the highly application-dependent behavior of power consumption [41]. They create abstract profiles to capture the differing characteristics of these applications. However, they do not ascribe specific properties of a computation in a way that programmers or algorithm designers can use to understand and change

time-energy behavior.

Tools Although we adopted PowerMon 2 [8] as our measurement infrastructure, there are numerous other possibilities. Perhaps the most sophisticated alternative is PowerPack [48], a hardware-software "kit" for power and energy profiling. However, the infrastructure is relatively elaborate and expensive to acquire, in contrast to PowerMon 2. In future studies, we expect to be able to use even simpler measurement methods based on vendor-provided hardware support. These include Intel hardware counters for power [109] and NVIDIA's Management Library for power measurement [100]. However, unlike Intel's tool, NVML only provides power consumption monitoring for the entire GPU, including the memory. Also, NVML on certain GPU models show a number of anomalous behaviors that require correction [17]

In terms of tools that help with energy efficiency, there is eprof [111] that can pinpoint energy–hungry sections of code, and other methods that attempt to reduce energy consumption through various hardware features [90, 91].

Other modeling approaches The direct inspiration for this paper comes from studies of architecture-cognizant extensions to Amdahl's Law, balance, and the time-based roofline [32, 29, 59, 128, 133, 80, 60, 61, 12, 89, 126, 70, 73].

However, there are numerous other approaches. For instance, numerous recent studies have developed detailed GPU-specific models [62, 7, 132]; though these models are capable of directly predicting time, they require very detailed characterizations of the input program and/or intimate knowledge of the GPU microarchitecture. As such, it is nontrivial to translate the output of these models into actionable algorithmic or software changes. There are also numerous models that try to incorporate power and energy [46, 85, 119, 63, 114, 118, 115, 96, 57]. However, like the time-based models, much of this work is systems centric, abstracting away algorithmic properties.

Simulators for power and energy Other efforts to model power dissipation include CACTI [127], McPAT [82], and GPUWattch [81] simulators. The underlying models derive from device—level estimates of power dissipation for caches and processor cores. The tools enable design—space exploration by quantifying the cost of new features and materials over different process technology generations. However, CACTI and McPAT are only validated against other simulators or against a breakdown of TDP published by the vendors. GPUWattch validates against real measurements but only on NVIDIA GPUs. Also, it was noted by Nowitzki et. al [97] that all of these simulators are often overfitted to certain benchmarks or configurations for validation purposes, and can therefore have significant modeling errors. An interesting question may be to what extent these tools corroborate, complement or contradict our experimental data and modeling approach.

Low-power system for HPC Interest in embedded/mobile SoC for HPC has grown rapidly in recent years. The most notable and perhaps the largest work is the Mont Blanc project [108] which attempts to build a supercomputer from low-power, low-performance ARM SoCs. However, there are numerous others that also employ mobile SoC for HPC [45, 69, 117, 52, 87, 106, 95, 116, 107], as well as those that use them for more general-purpose applications such as computer vision and speech processing [55, 125, 124, 113, 22]

Notably, Fürlinger et al. [45] assembled a cluster of ARM Cortex-A8 based systems (Apple TV) to test the viability of an ARM-based system for HPC using the LIN-PACK benchmark. In the work by Reddi et. al [69], the authors consider low-power atom processor as an alternative to conventional server processors in the context of search engines. A study by Stanley-Marbell et. al [117] compares ARM, Atom, and Freescale systems in the context of dense linear algebra, graphs, and MapReduce. These studies are typically limited to specific systems or applications and cannot

easily be extended to a wider range of architectures and workloads.

Architectural studies In the work by Hameed et al. [58], the authors use H.264 decoder as a case study to compare general purpose processors to ASICs in terms of energy efficiency. The authors show that ASICs achieve orders of magnitude higher energy efficiency by reducing instruction overhead that typically make up over 90% of the energy cost associated with each computation.

Others have found ways to *circumvent* the energy problem altogether by designing general purpose processors that use a different paradigm. Esmaeilzadeh et al. [38] propose a new architecture and programming framework for off-loading portions of annotated code that does not require exact computation to accelerators that approximates the result using neural networks. In [104, 105], the authors propose processors that are designed specifically for the sole purpose of computing matrix multiplication.

These solutions are unique and innovative, but less practical in the foreseeable future. One distinction of our study is its analysis of off-the-shelf components, which may be better suited to near-term design space exploration and experimentation.

Design space exploration for energy efficiency Hardware–software co–designing where traditional architecture design space exploration is tightly coupled with application tuning can lead to energy–efficient systems [92, 83]. In particular, Libuschewski et al. formulate this challenge as an optimization problem and utilize an evolutionary algorithm to automatically reach the optimal solution.

Others have proposed "overprovisioning" as a viable solution to tackling limited power budget for supercomputers [103, 40, 39]. Patki et al. [103] predict that in the future supercomputing centers will buy more compute capacity than can be used, and, instead of running them simultaneously as before, allow users to customize the system to the application to achieve better performance. The idea of "dark silicon" proposed by Esmaeilzadeh et al. [40, 39] suggests that we will not be able to power

all transistors simultaneously (hence, there will be "dark" or unpowered transistors) in the future. In that case, these unpowered transistors may become specialized units and will only be turned on when the application can benefit from them, which is similar to the idea behind overprovisioning.

Metrics Our models reason directly about the basic measures of time, energy, and power. When considering trade-offs and multiobjective optimization, other metrics may be better suited. These include the energy delay product (EDP) and generalizations [51, 9], FLOP/s per Watt (i.e., flops per Joule) [112], and The Green Index [120].

## CHAPTER III

## ENERGY ROOFLINE MODEL

#### Contents

| 3.1 | A Basic Model and its Interpretation     | 19 |

|-----|------------------------------------------|----|

| 3.2 | What the Basic Model Implies About Power | 29 |

| 3.3 | An experiment                            | 30 |

| 3.4 | Discussion, Application, and Refinement  | 41 |

| 3.5 | Algorithmic Trade-offs                   | 48 |

| 3.6 | Conclusion                               | 61 |

In this section, we describe the energy roofline model and demonstrate how this model can help guide analysis and tuning for energy efficiency. In § 3.1, we derive the basic model and define new terms, such as the energy-balance and the time-energy balance gap of a system. We also show how our model can be visualized using rooflines in energy (or arch lines), analogous to the rooflines in time [126], to aid in algorithmic energy-efficiency analysis. In § 3.2 we show how the balance gap impacts average power and discuss our experimental setup and microbenchmarks in § 3.3. In § 3.4, we discuss our fitted parameters and experimental result. We also apply our model to a real application to see how closely the model can predict energy consumption, and discuss why our predictions are not accurate and what can be

Figure 1: A simple von Neumann architecture with a two-level memory hierarchy. In our first analysis, suppose that an algorithm performs W arithmetic operations and Q memory operations, or "mops," between slow and fast memories.

done to remedy it. We conduct a hypothetical study on work–communication trade–off, where we reduce communication in exchange for extra computation, to test its viability for saving energy § 3.5. Finally, we give our conclusion in § 3.6.

## 3.1 A Basic Model and its Interpretation

Assume the simple architecture shown in fig. 1. This architecture has a processing element, labeled "xPU", as well as two levels of memory, namely, an infinite slow memory and a fast memory of finite capacity. This system roughly captures everything from a single functional unit (xPU) attached to registers (fast memory), to a manycore processor (xPU) attached to a large shared cache (fast memory). Further assume that the xPU may only perform operations on data present in the fast memory. As such, an algorithm for this architecture must explicitly move data between slow and fast memories.

### 3.1.1 Algorithm characterization

Let W be the total number of "useful" compute operations that the algorithm performs and let Q be the total amount of data it transfers between the slow and fast memories. (Table 1 summarizes all of the parameters of our model.) By useful, we mean in an algorithmic sense; for example, we might only count flops when analyzing matrix multiply, or comparisons for sorting, or edges traversed for a graph traversal algorithm. For simplicity, we will assume W is measured in units of scalar flops. (That is, a 4-way SIMD add is 4 scalar flops; a FMA is two scalar flops.) We will also refer to W as the total work of the algorithm. Regarding Q, we will for simplicity not distinguish between loads and stores, though one could do so in principle. We will refer to Q as mops measured in some convenient storage unit, such as a word or a byte.

In a typical algorithm analysis, both W and Q will of course depend on characteristics of the input, such as its size n;<sup>1</sup> in addition, Q will depend on the size of the fast memory. We discuss these dependences momentarily.

For performance analysis and tuning, we may measure the algorithm's computational intensity, which is defined as  $I \equiv W/Q$ . Intensity has units of operations per unit storage, such as flops per word or flops per byte. Generally speaking, a higher value of I implies a more "scalable" algorithm. That is, it will have more work than mops; therefore, it is more likely to improve as the architecture's compute throughput increases, which happens as cores increase or SIMD lanes widen.

What should we expect about the value of I? Recall that Q depends on fast memory capacity, which we denote by Z units of storage (words or bytes), as shown in fig. 1. Therefore, intensity will also depend on Z. A well-known result among

<sup>&</sup>lt;sup>1</sup>That is, imagine a  $W(n) = \mathcal{O}(n)$  style of analysis. However, unlike the traditional forms of such analysis, we will also want to characterize constants and costs much more precisely whenever possible.

Table 1: Summary of model parameters

| Variable                                                                | Description                                                                                           |

|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| $\overline{W}$                                                          | # of useful compute operations, e.g., # of flops                                                      |

| Q                                                                       | # of main memory operations ("mops")                                                                  |

| I                                                                       | Intensity, or $W/Q$ (e.g., flops per byte)                                                            |

| $	au_{ m flop}$                                                         | Time per work (arithmetic) operation, e.g., time per flop                                             |

| $	au_{ m mem}$                                                          | Time per mop                                                                                          |

| $B_{	au}$                                                               | Balance in time, $\tau_{\text{\tiny mem}}/$ $\tau_{\text{\tiny flop}}$ (e.g., flops per byte)         |

| $\epsilon_{	ext{flop}}$                                                 | Energy per arithmetic operation                                                                       |

| $\epsilon_{	ext{mem}}$                                                  | Energy per mop                                                                                        |

| $B_{\epsilon}$                                                          | Balance in energy, $\epsilon_{\text{mem}}/\epsilon_{\text{flop}}$ (e.g., flops per Joule)             |

| $\epsilon_0$                                                            | Constant energy per flop                                                                              |

| $\hat{\epsilon}_{	ext{flop}} \equiv \epsilon_{	ext{flop}} + \epsilon_0$ | Minimum energy to execute one flop                                                                    |

| $\eta_{	ext{flop}}$                                                     | Constant-flop energy efficiency, $\frac{\epsilon_{\text{flop}}}{\epsilon_{\text{flop}}+\epsilon_0}$   |

| $\pi_0$                                                                 | Constant power, e.g., Joule per second = Watts                                                        |

| $\pi_{	ext{flop}}$                                                      | Baseline power per flop excluding constant power, $\frac{\epsilon_{\text{flop}}}{\tau_{\text{flop}}}$ |

| $\hat{B}_{\epsilon}(I)$                                                 | Effective energy-balance $(\pi_0 \ge 0)$                                                              |

| $T_{ m flops}$                                                          | Total time to perform arithmetic                                                                      |

| $T_{ m mem}$                                                            | Total time to perform mops                                                                            |

| T                                                                       | Total time                                                                                            |

| $E_{\mathrm{flops}}$                                                    | Total energy of arithmetic                                                                            |

| $E_{\scriptscriptstyle  m mem}$                                         | Total energy of mops                                                                                  |

| $E_0$                                                                   | Total "constant" energy                                                                               |

| E                                                                       | Total energy                                                                                          |

| <i>P</i>                                                                | Average power                                                                                         |

| Z                                                                       | Fast memory size (e.g., words, bytes)                                                                 |

|                                                                         |                                                                                                       |

algorithm designers is that no algorithm for  $n \times n$  matrix multiply can have an intensity exceeding  $I = \mathcal{O}\left(\sqrt{Z}\right)$  [70]. Consequently, if we improve an architecture by doubling Z, we will improve the inherent algorithmic intensity of a matrix multiply algorithm by no more than  $\sqrt{2}$ . Contrast this scenario to that of just summing all of the elements of an array. Intuitively, we expect this computation to be memory bandwidth bound if the array is very large. Indeed, it has an intensity of  $I = \mathcal{O}(1)$ , that is, a constant independent of problem size or Z. Thus, increasing Z has no effect on the intensity of this kind of reduction. In short, the concept of intensity measures the inherent locality of an algorithm.

#### 3.1.2 Time and energy costs

Next, we translate the abstract W and Q into concrete time and energy costs. We will distinguish between the costs of performing work versus that of data transfer. Furthermore, our model of energy cost will have two significant differences from our model of time cost, namely, (i) time costs may be overlapped whereas energy may not; and (ii) we must burn constant energy, which is an additional minimum baseline energy on top of operation and data movement costs. These distinctions are critical, and together determine whether or not one should expect an algorithmic time—energy trade—off (see § 3.5).

More formally, suppose  $T_{\text{flops}}$  and  $T_{\text{mem}}$  are the total time (seconds) to execute all work operations and all mops, respectively. Further assume, *optimistically*, that overlap is possible. Then, the total time T is

$$T \equiv \max\left(T_{\text{flops}}, T_{\text{mem}}\right). \tag{1}$$

Similarly, suppose that  $E_{\text{flops}}$  and  $E_{\text{mem}}$  are the total energy (Joules) for work and mops. In addition, let  $E_0(T)$  be the constant energy of the computation. Constant energy is the energy that must be expended for the duration of the computation, which we will further assume is a fixed cost independent of the type of operations

Table 2: Sample values for model parameters, based on best case (peak) capabilities of currently available systems. See table 1 for a summary of the definitions of these parameters.

|                         | Representative values                                                                                                                                                                                                      |  |  |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Variable                | NVIDIA "Fermi" GPU [123]                                                                                                                                                                                                   |  |  |