# Novel Doherty Power Amplifier Design for Advanced Communication Systems

FANG, Xiaohu

A Thesis Submitted in Partial Fulfillment

of the Requirements for the Degree of

Doctor of Philosophy

in

**Electronic Engineering**

The Chinese University of Hong Kong

May 2015

### Abstract

As modern communication system demands higher spectrum efficiency and data rate, new communication standard using complex modulation scheme has emerged and led to transmitting signal with ever-increasing Peak-to-Average Power Ratio (PAPR). Moreover, the co-existence of different standards requires RF transceivers to support signal transmission at multiple carrier frequencies. Therefore, wideband operation and efficient amplification of high PAPR signal are prime requirements for base-station PA design.

For efficiency enhancement, the Doherty Power Amplifier (DPA) [1] has been regarded as the most popular approach due to its circuit simplicity and moderate linearity. Three innovative DPA design techniques relating to the enhancement of operating bandwidth, high efficiency range and power utilization factor (PUF) are proposed in this work.

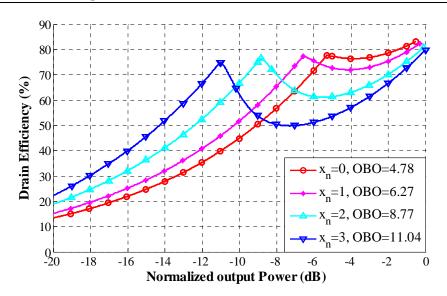

In the first demonstration, a novel DPA configuration with Complex Combining Load (CCL) is presented to extend the high efficiency range of the amplifier. Theoretical analysis of dynamic load span, current ratio and drain efficiency reveals that complex combining load can offer a new degree of freedom to boost the Output Back-off (OBO) of DPA. For verification, a 2GHz, equal-cell, GaN HEMT-based DPA is simulated, prototyped and measured with both complex and resistive combining loads. Under Continuous Wave (CW) excitation, measurement results show that the CCL DPA can attain an OBO of 9.1 dB which is 3.6 dB higher than that of the RCL design. In addition, by the use of single-carrier WCDMA signal with PAPR of 9.6 dB and at an average output power of 33.2 dBm, the CCL design is found to deliver an average drain efficiency of 57.4%.

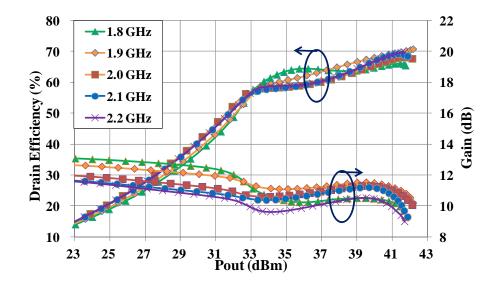

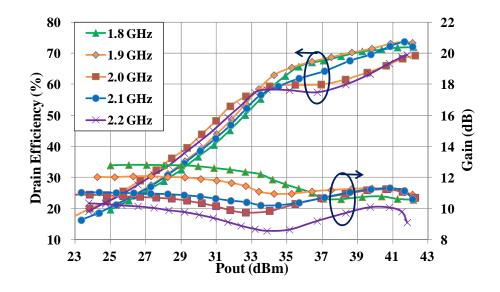

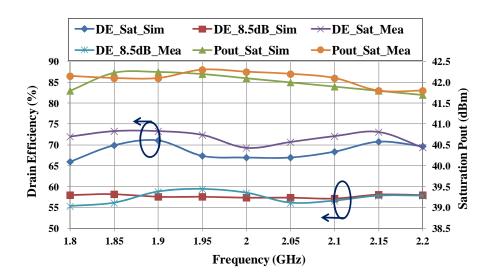

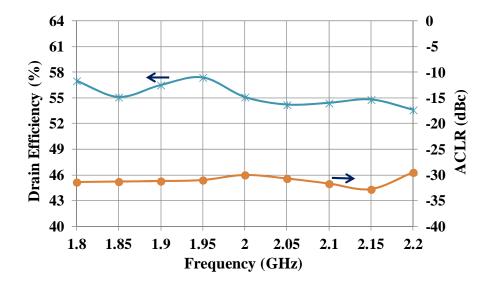

The second design presents a novel technique to extend the bandwidth and efficiency range of DPA by the adoption of frequency-varying Complex Combining Load and proper input current control strategy. For verification, a 42 dBm, 1.8-2.2 GHz DPA with OBO of 8.5 dB was designed, built and characterized. Under CW stimulation, a back-off efficiency (8.5 dB) of 55-59% and saturation efficiency of 69-73% were observed over the entire bandwidth. With single carrier WCDMA signal excitation (PAPR of 9.6 dB), an average drain efficiency of 53-58% was obtained at 33.5 dBm average output power and Adjacent Channel Leakage Power Ratio (ACLR) of around -30 dBc.

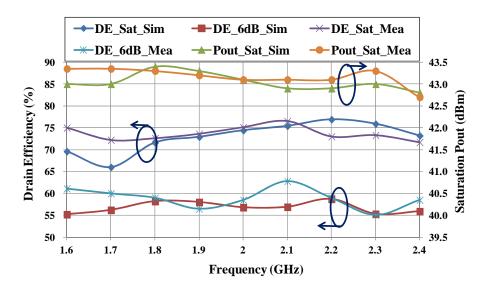

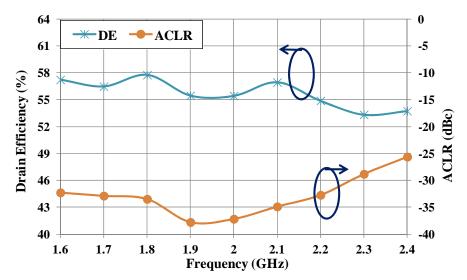

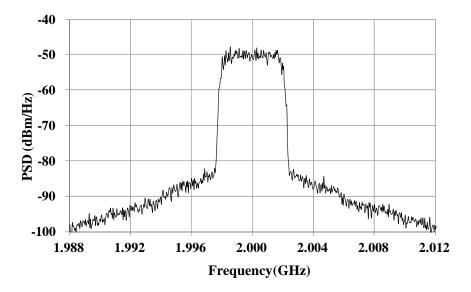

In the last technique, a novel DPA configuration with auxiliary transformer is presented for broadband operation. Theoretical analysis reveals that the presented design can offer enhanced PUF and wideband Doherty behavior. Based on the proposed theory, a 1.6-2.4 GHz, 20 W DPA with improved PUF is designed, simulated and measured. Under CW excitation, measurement results indicate that the presented DPA can achieve a PUF of 0.94, good Doherty behavior over the entire frequency band with a 6 dB back-off efficiency of 55-64% and saturated efficiency of 68-76%. In addition, by the use of single-carrier WCDMA signal (centered at 2 GHz) with PAPR of 6.6 dB and at an average output power of 37 dBm, an average drain efficiency of 56% is obtained with ACLR of better than – 37 dBc.

随着无线通信的蓬勃发展,新的通信标准不断出现,频谱利用率和数据传 输速率提高的同时,传输信号的带宽和均峰比也不断增加。此外,多种通信标 准共存的现状要求收发机能够在多个载波频率,高效率地传输不同格式的信号。 因此,宽带运行和高效的放大高均峰比信号成为了基站功率放大器设计的基本 要求。

Doherty 功率放大器结构简单,增加效率的同时能保持中等线性度,故而受到了广泛关注。本文囊括了三个有关增加 Doherty 放大器工作带宽、延展高效率区或提高功率利用因子的创新设计。

第一个设计中,复数合路阻抗被用于扩宽 Doherty 放大器的高效率区。关 于动态阻抗范围,电流比因子和漏极效率的理论分析说明,复数合路阻抗可以 当作新的自由度来增加放大器的高效率区。为了验证有关理论,以 2GHz 为工作 频点,我们使用了相同的基于 GaN 工艺的晶体管,分别设计了使用复数合路阻 抗和纯实数合路阻抗的 Doherty 放大器。连续波测试结果显示,使用复数合路 阻抗的 Dohety 放大器能够提高 9.1dB 的输出回退范围,比基于纯实数合路阻抗 的传统设计要高 3.6dB。此外,使用单载波、均峰比 9.6dB 的 WCDMA 信号的测试 显示,基于复数合路阻抗的设计在输出功率为 33.2dBm 时,其平均漏极效率高 达 57.4%。

第二个设计中使用了随频率变化的复数合路阻抗,通过控制漏极电流,来 同时增加 Doherty 放大器的工作带宽和高效率区。为了验证有关理论,我们设 计了输出功率 42dBm、工作带宽 1.8-2.2GHz、输出回退区 9dB 的 Doherty 放大 器。连续波测试结果显示,在 8.5dB 回退点处,该设计在 8.5dB 回退点和饱和

iii

输出点的漏极效率分别高达 55-59%和 69-73%。使用单载波、均峰比 9.6dB 的 WCDMA 信号的测试显示,该设计在输出功率为 33.5dBm 时,其平均漏极效率高达 53-58%,邻道抑制比也能保持在-30dBc。

最后一个设计中,一种在辅助支路加入变换器的 Doherty 结构被用于宽带 放大。理论分析显示了该结构能够增加功率利用因子,并提供宽带 Doherty 特 性。为了验证有关理论,我们设计了输出功率 20W、工作带宽 1.6-2.4GHz、功 率利用因子得到改善的 Doherty 放大器。连续波测试结果显示,该设计的功率 利用因子高达 0.94,所有频点均可得到良好的 Doherty 效率特性,该设计在 6dB 回退点和饱和输出点的漏极效率分别高达 55-64%和 68-76%。在 2GHz 处,使用 单载波、均峰比 6.6dB 的 WCDMA 信号的测试显示,该设计在输出功率为 37dBm 时,其平均漏极效率高达 56%,邻道抑制比低于-37dBc。

### Acknowledgements

First and foremost, I would like to express my sincere gratitude to my supervisor, Prof. Michael Kwok Keung CHENG, who paved the way for me toward the realm of RF and microwave circuit design. His rigorous research attitude, profound knowledge and extraordinary foresight push me to the cutting edge of my research field. Everything I learnt from Prof. Michael Kwok Keung CHENG will always be my lifetime treasures.

Also, it gives me great pleasure to thank Prof. Ke-Li Wu for all the guidance and helpful instructions. Special thanks to our lab technician, Mr. Leo Fung, who help me in every possible aspect of my research. I do not know how to thank him enough for being such a nice person.

Moreover, I must thank all my research-mates, colleagues and lifetime friends: Dr. Wei Li, Mr. Edward Yeung, Dr. Luyu Zhao, Dr. Hai Hu, Dr. Xi Wang, Mr. Meng Huang, Mr. Dacheng Wei, Mr. Jonathan Chik, Mr. Chenxi Zhai, Mr. Tommy Hung, Mr. Zhenyuan Zhang, Mr. Ping Zhao, Ms. Yuhang Dou, Mr. Yang Jiang, Mr. Zhiliang Li, for all the fruitful corporations and discussions.

Last but not least, my sincere gratitude goes to my families. My parents bring me up with unlimited love, and support me unconditionally throughout my life. My wife, Zhang Xiaoya, enriches my life with her love and vigor, and my lovely daughter, her birth gives me endless joy and pleasure.

## CONTENTS

| Abstracti                                               |

|---------------------------------------------------------|

| Acknowledgementv                                        |

| Table of Contentsvi                                     |

| List of Figuresx                                        |

| List of Tablesxvii                                      |

| CHAPTER 1 INTRODUCTION1                                 |

| 1.1 Design Challenges of RF Power Amplifier1            |

| 1.1.1 Peak-to-Average Power Ratio (PAPR)2               |

| 1.1.2 Wideband operation4                               |

| 1.2 Performance Evaluation of RF Power Amplifier5       |

| 1.2.1 Output power                                      |

| 1.2.2 Efficiency7                                       |

| 1.2.3 Linearity                                         |

| 1.2.4 Power Utilization Factor                          |

| 1.3 Motivation and outline of this work11               |

| References13                                            |

| CHAPTER 2 CLASSICAL THEORY ON HIGH EFFICIENCY POWER     |

| AMPLIFIER DESIGN14                                      |

| 2.1 Traditional operation modes: Class A, AB, B and C14 |

| 2.2 High Efficiency mode: class F20                     |

| 2.3 The switching mode: Class E                                    |

|--------------------------------------------------------------------|

| 2.4 Efficiency Enhancement Techniques                              |

| 2.4.1 Doherty amplifier                                            |

| 2.4.2 Envelope Elimination and Restoration Technique               |

| 2.4.3 Outphasing Technique                                         |

| References                                                         |

| CHAPTER 3 LITERATURE REVIEW ON ADVANCED DOHERTY POWER              |

| AMPLIFIER DESIGN                                                   |

| 3.1 Recent works on DPA design with extended high efficiency range |

| 3.2 Recent works on DPA design with extended operating bandwidth43 |

| References                                                         |

| CHAPTER 4 EXTENSION OF HIGH EFFICIENCY RANGE OF DOHERTY            |

| AMPLIFIER BY USING COMPLEX COMBINING LOAD50                        |

| 4.1 Theory of Complex Combining Load (CCL) DPA50                   |

| 4.1.1 Formulation of OBO under ideal Doherty operation51           |

| 4.1.2 Dynamic load span under complex combining load53             |

| 4.1.3 Derivation of operation parameters and drain loads           |

| 4.1.4 Determination of the phase of I <sub>dA</sub> 60             |

| 4.1.5 Derivation of drain efficiency curve61                       |

| 4.2 Circuit Design and Simulation                                  |

| 4.2.1 Extended DPA design for maximum efficiency and PUF63         |

| 4.2.2 Extended DPA design for optimum efficiency and linearity67   |

| 4.3 Experimental Verification                                                |

|------------------------------------------------------------------------------|

| 4.3.1 CW Signal Measurement70                                                |

| 4.3.2 Two-tone Signal Measurement72                                          |

| 4.3.3 Modulated Signal Measurement74                                         |

| 4.4 Conclusion75                                                             |

| References76                                                                 |

| CHAPTER 5 BROADBAND, WIDE EFFICIENCY RANGE, DOHERTY                          |

| AMPLIFIER DESIGN USING FREQUENCY-VARYING COMPLEX                             |

| COMBINING LOAD                                                               |

| 5.1 Proposed Methodology79                                                   |

| 5.1.1 S-Parameter Formulation of Matching Networks80                         |

| 5.1.2 Optimum broadband performance extraction                               |

| 5.2 Design and Simulation                                                    |

| 5.2.1 Drain Bias Selection and Optimum Load Extraction                       |

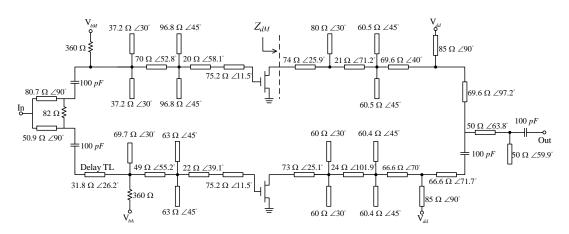

| 5.2.2 Frequency-varying CCL and Output Matching Network Design85             |

| 5.2.3 Extraction of Current Relationship and Input Matching Network Design87 |

| 5.2.4 Simulation Result of Frequency-varying CCL DPA                         |

| 5.3 Experiments and Results                                                  |

| 5.4 Conclusion                                                               |

| References                                                                   |

| CHAPTER 6 IMPROVING POWER UTILIZATION FACTOR OF BROADBAN      | D  |

|---------------------------------------------------------------|----|

| DOHERTY AMPLIFIER BY USING BAND-PASS AUXILIAR                 | Y  |

| TRANSFORMER9                                                  | 5  |

| 6.1 Theory9                                                   | 5  |

| 6.1.1 PUF of Conventional DPA configurations9                 | 96 |

| 6.1.2 Enhanced PUF by using Auxiliary Transformer9            | 18 |

| 6.1.3 Optimal Phase Control for Broadband Operation10         | )1 |

| 6.1.4 Drain Voltage Profiles and Efficiency Performance       | 4  |

| 6.2 Circuit Design and Simulation10                           | )5 |

| 6.2.1 Bias Selection and Optimum Drain Load Extraction10      | 6  |

| 6.2.2 Design of Output Matching Network of Auxiliary Device10 | )7 |

| 6.2.3 Output Matching of Main Device and Combining Network11  | 0  |

| 6.2.4 Proposed DPA: Simulation Results11                      | .1 |

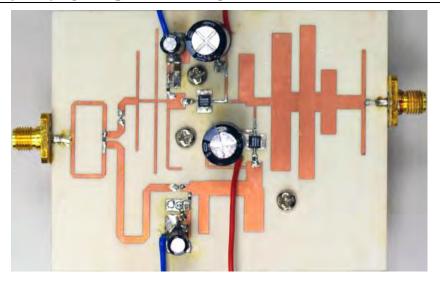

| 6.3 Experimental Verification                                 | 5  |

| 6.3.1 CW Signal Measurement11                                 | 5  |

| 6.3.2 Modulated Signal Measurement11                          | 7  |

| 6.4 Conclusion12                                              | 0  |

| References12                                                  | 20 |

| CHAPTER 7 CONCLUSIONS AND FUTURE WORKS12                      | :3 |

| 7.1 Conclusions                                               | 23 |

| 7.2 Recommendation for Future Research12                      | 24 |

| List of Publications                                          | 6  |

## **List of Figures**

| Fig. 1.1 The simplified diagram of transmitter1                                      |

|--------------------------------------------------------------------------------------|

| Fig. 1.2 Time domain waveform of the envelope of a typical WCDMA signal2             |

| Fig. 1.3 The Probability Density Function of modulated signals with various formats: |

| (a) EDGE signal; (b) WCDMA signal; (c) LTE signal                                    |

| Fig. 1.4 Simplified diagram of RF PA6                                                |

| Fig. 1.5 The typical output power performance as a function of input power           |

| Fig. 1.6 Theoretical drain efficiency behavior of the Class A PA7                    |

| Fig. 1.7 Evaluation of average drain efficiency under modulated signal               |

| Fig. 1.8 Input and output spectrum of PA (Two-tone test): (a) Input; (b) Output9     |

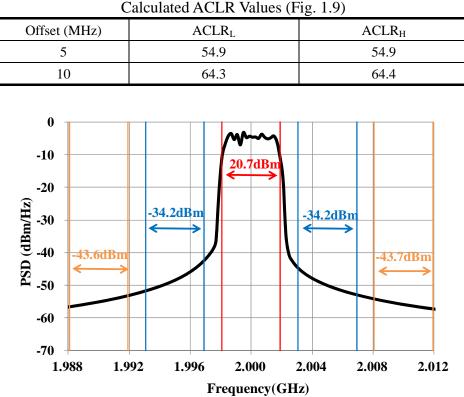

| Fig. 1.9 Output Spectrum density of typical PA under complex modulated signal10      |

| Fig. 2.1 Simplified diagram of PA14                                                  |

| Fig. 2.2 Traditional operation modes: (a) Class A; (b) Class AB; (c) Class B; (d)    |

| Class C16                                                                            |

| Fig. 2.3 Fourier analysis of drain current                                           |

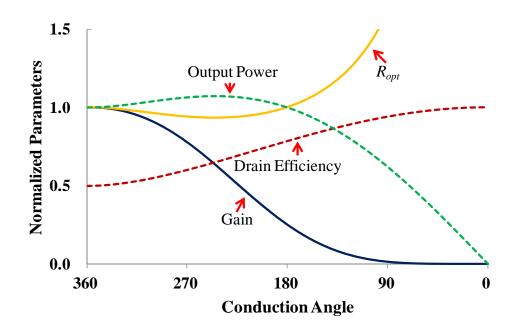

| Fig. 2.4 Calculated maximum output power, drain efficiency , optimum drain load      |

| and gain as the function of conduction angle18                                       |

| Fig. 2.5 Theoretical gain performace as a function of normalized output power under  |

| different operation mode19                                                           |

| Fig. 2.6 Simplified diagram of Class F amplifier20                                      |

|-----------------------------------------------------------------------------------------|

| Fig. 2.7 Drain voltage flatting process from Class B to Class F: (a) Class B; (b) Class |

| F with 3rd harmonic peaking; (c) Class F with 3rd and 5th harmonic peaking; (d)         |

| Class F with infinite odd harmonics21                                                   |

| Fig. 2.8 The simplified diagram of class E amplifier23                                  |

| Fig. 2.9 Theoretical drain current and voltage waveforms of Class E amplifier under     |

| 50% duty cycle23                                                                        |

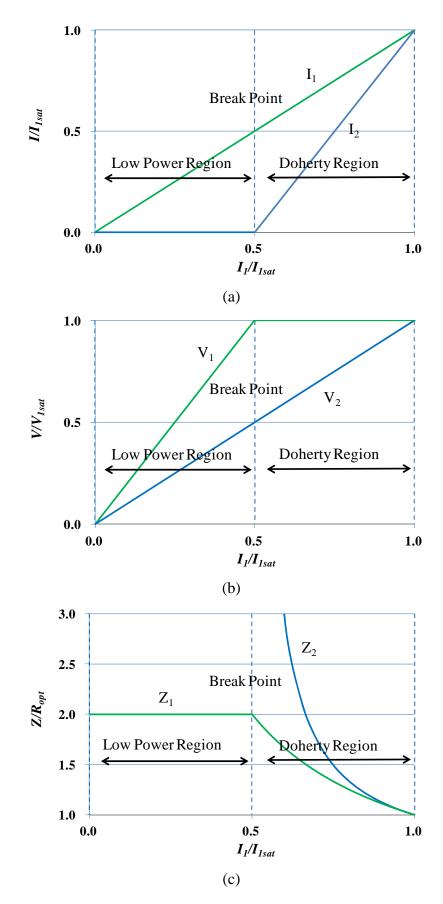

| Fig. 2.10 Simplified diagram of the Doherty amplifier26                                 |

| Fig. 2.11 Typical drain efficiency behavior of the Doherty amplifier27                  |

| Fig. 2.12 Parameter Profiles for Doherty operation: (a) Drain current; (b) Drain        |

| Voltage; (c) Drain load;29                                                              |

| Fig. 2.13 The basic diagram of Envelope Elimination and Restoration (EER)               |

| technique                                                                               |

| Fig. 2.14 The basic diagram of the outphasing technique                                 |

| Fig. 2.15 Chireix Outphasing Amplifier: (a) Without compensation for the complex        |

| load; (b) With compensation for the complex load                                        |

| Fig. 2.16 Drain efficiency behaviors of the Chireix Outphasing Amplifier under          |

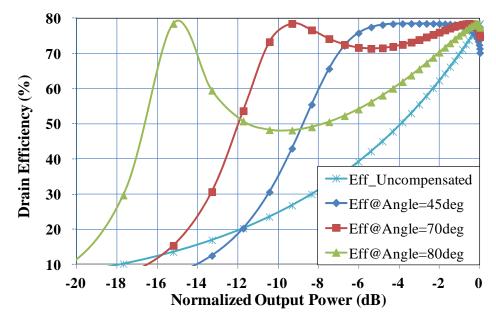

| various compensation angles                                                             |

| Fig. 3.1 Simplified diagram of classical Doherty amplifier                              |

| Fig. 3.2 Simplified diagram of multi-way Doherty amplifier                              |

| Fig. 3.3 Theoretical drain efficiency behavior of the asymmetrical DPA and the        |

|---------------------------------------------------------------------------------------|

| multi-way DPA40                                                                       |

| Fig. 3.4 Simplified diagram of multi-stage Doherty amplifier40                        |

| Fig. 3.5 Theoretical drain efficiency behavior of the 3-stage DPA with gate periphery |

| ratio of 1:3:441                                                                      |

| Fig. 3.6 Current profiles of a 3-stage DPA with gate periphery ratio of 1:3:441       |

| Fig. 3.7 Circuit diagram of the modified 3-stage Doherty amplifier41                  |

| Fig. 3.8 Block diagram of DPA43                                                       |

| Fig. 3.9 Theoretical broadband drain efficiency behavior of DPA under classical       |

| configuration44                                                                       |

| Fig. 3.10 Theoretical broadband drain efficiency behavior of DPA under classical      |

| configuration46                                                                       |

| Fig. 3.11 Optimum saturation k and $\theta_d$ versus operating frequency47            |

| Fig. 3.12 Optimum current profiles: (a) magnitude ratio $k$ ; (b) phase difference    |

| $\theta_d$                                                                            |

| Fig. 4.1 Efficiency behavior of ideal Doherty amplifier51                             |

| Fig. 4.2 Simplified schematic of DPA with complex combining load52                    |

| Fig. 4.3 Designated load and input impedances of OMN <sub>M</sub> 54                  |

| Fig. 4.4 Simplified circuit topology of the proposed DPA55                            |

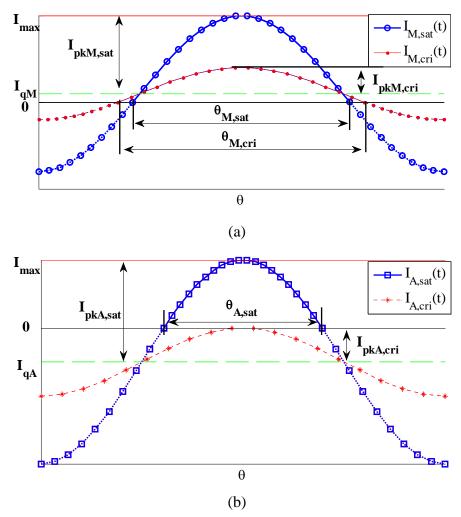

| Fig. 4.5 Drain current waveforms: (a) Main device; (b) Auxiliary device56             |

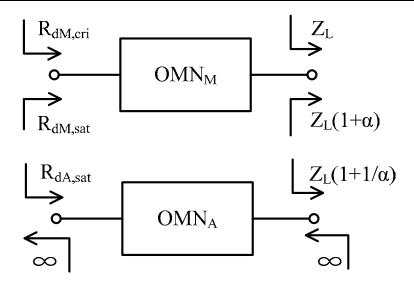

| Fig. 4.6 Design targets (impedance levels) of matching networks60                     |

| Fig. 4.7 Theoretical drain efficiency behavior                                         |

|----------------------------------------------------------------------------------------|

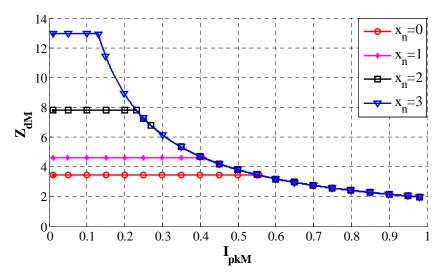

| Fig. 4.8 Calculated $Z_{dM}$ versus $I_{pkM}$                                          |

| Fig.4.9 Schematic diagram of the proposed CCL-lin DPA64                                |

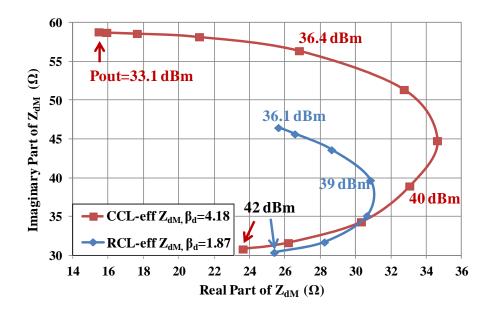

| Fig. 4.10 Simulated load trace of $Z_{dM}$ (Doherty region) of the CCL-eff and RCL-eff |

| DPAs65                                                                                 |

| Fig.4.11 Simulated efficiency and gain performance of the CCL-eff and RCL-eff          |

| DPAs as a function of output power with CW signal                                      |

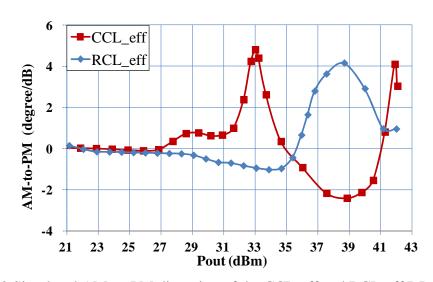

| Fig. 4.12 Simulated AM-to-PM distortion of the CCL-eff and RCL-eff DPAs as a           |

| function of output power with CW signal67                                              |

| Fig.4.13 Simulated drain efficiency and gain performance of the CCL-lin DPA at         |

| multiple frequencies (CW)                                                              |

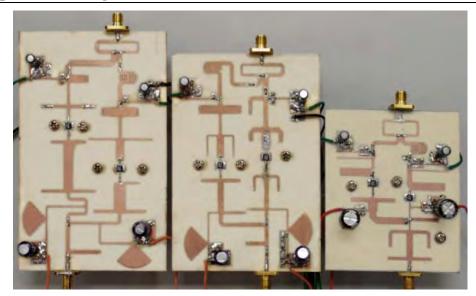

| Fig. 4.14 Photograph of the CCL-eff DPA (left), RCL-eff DPA (middle) and CCL-lin       |

| DPA (right)69                                                                          |

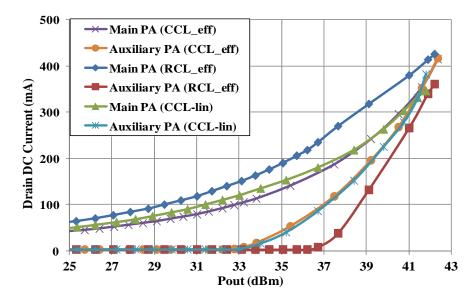

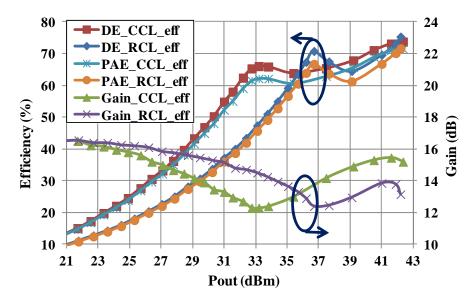

| Fig. 4.15 Measured drain dc current consumption versus output power of all designs     |

| (CW)70                                                                                 |

| Fig. 4.16 Measured efficiency and gain performance of the CCL-eff and RCL-eff          |

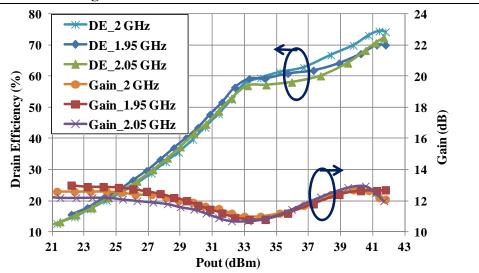

| DPAs (CW)70                                                                            |

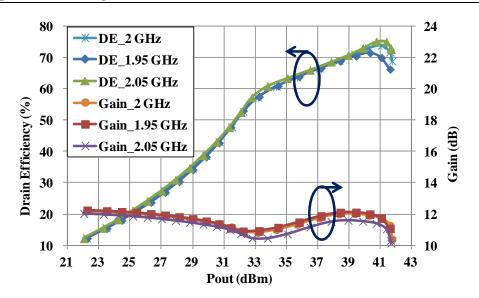

| Fig. 4.17 Measured drain efficiency and gain performance of the CCL-lin DPA at         |

| multiple frequencies (CW)71                                                            |

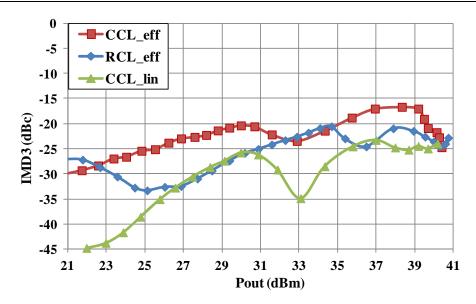

| Fig. 4.18 Measured IMD3 performance of all designs (two-tone)72                        |

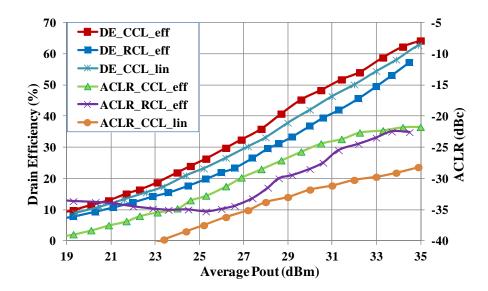

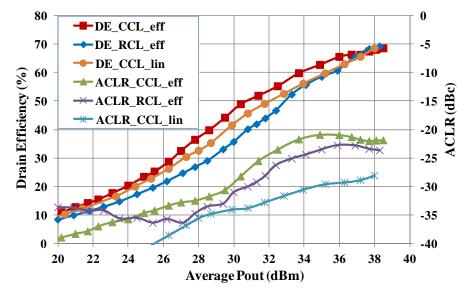

| Fig. 4.19 Measured average drain efficiency and ACPR of all designs (9.6 dB PAPR       |

| WCDMA)73                                                                               |

| Fig. 4.20 Measured average drain efficiency and ACPR of all designs (6.6 dB PAPR       |

|----------------------------------------------------------------------------------------|

| WCDMA signal)73                                                                        |

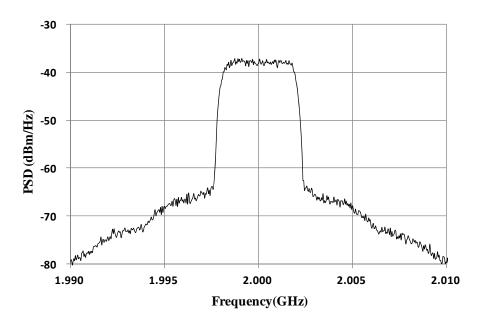

| Fig. 4.21 Measured spectrum of WCDMA signal (9.6 dB PAPR) of the CCL-lin               |

| design at an average output power of 33.2 dBm74                                        |

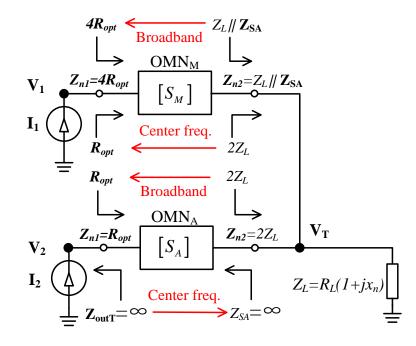

| Fig. 5.1 Simplified circuit diagram of DPA and impedance transformation                |

| relationships of the output matching networks                                          |

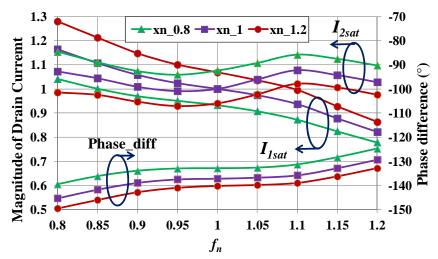

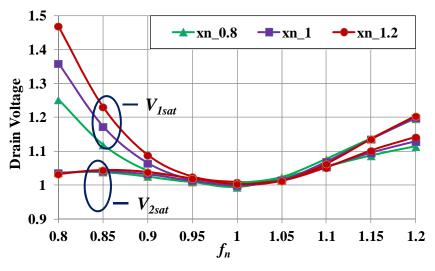

| Fig. 5.2 Drain current control (magnitude and phase difference)                        |

| Fig. 5.3 Optimum saturation drain voltage                                              |

| Fig. 5.4 Optimum saturation output power and PUF                                       |

| Fig. 5.5 Designed output matching networks: (a) $OMN_M$ ; (b) $OMN_A$ ; (c) $OMN_C$ 86 |

|                                                                                        |

| Fig. 5.6 Simulated matching performance and phase response: (a) $OMN_M$ ; (b)          |

| Fig. 5.6 Simulated matching performance and phase response: (a) $OMN_M$ ; (b) $OMN_A$  |

|                                                                                        |

| OMN <sub>A</sub>                                                                       |

| Fig. 6.1 Simplified schematic of Doherty power amplifier96                               |

|------------------------------------------------------------------------------------------|

| Fig. 6.2 Proposed DPA configuration with auxiliary transformer                           |

| Fig. 6.3 Proposed DPA with non-ideal transformer: (a) Simplified version; (b)            |

| Equivalent circuit                                                                       |

| Fig. 6.4 Calculated phase difference as a function of frequency102                       |

| Fig. 6.5 Saturation drain voltage of main device versus frequency103                     |

| Fig. 6.6 Saturation drain voltage of auxiliary device versus frequency103                |

| Fig. 6.7 Calculated drain voltage of proposed topology104                                |

| Fig. 6.8 Calculated drain voltage of conventional topology105                            |

| Fig. 6.9 Drain efficiency of the proposed and conventional designs106                    |

| Fig. 6.10 Design Targets of output matching networks: (a) Auxiliary device ; (b)         |

| Main device108                                                                           |

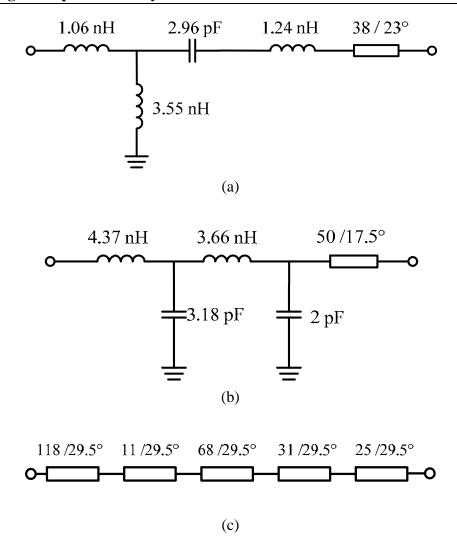

| Fig. 6.11 Circuit topologies for auxiliary matching network: (a) Band-pass ; (b)         |

| Low-pass 1; (c) Low-pass 2 (line impedance in ohm)109                                    |

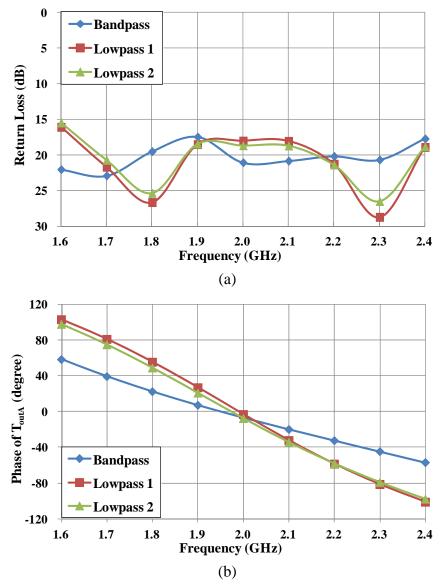

| Fig. 6.12 Simulation results of different circuit topologies: (a) Return Loss; (b) Phase |

| response110                                                                              |

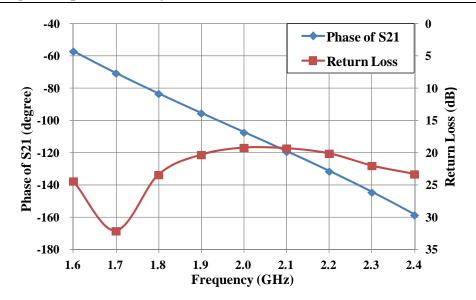

| Fig. 6.13 Simulated Return Loss and phase response of OMN <sub>M</sub> 111               |

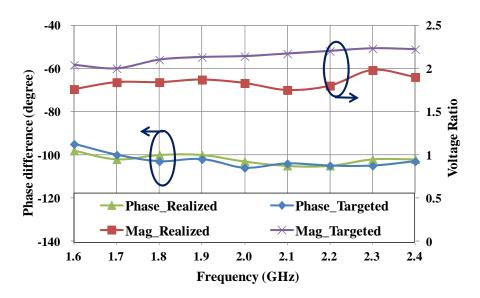

| Fig. 6.14 Extracted and realized voltage ratio and phase difference by                   |

| simulation112                                                                            |

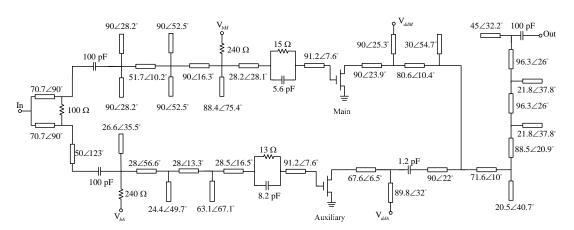

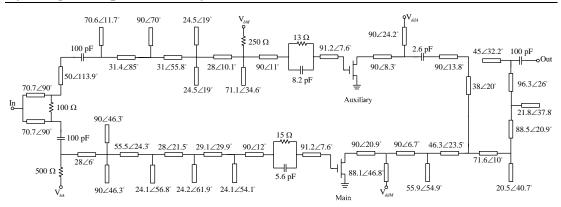

| Fig. 6.15 Schematic diagram of the proposed DPA (line impedance in                       |

| ohm)113                                                                                  |

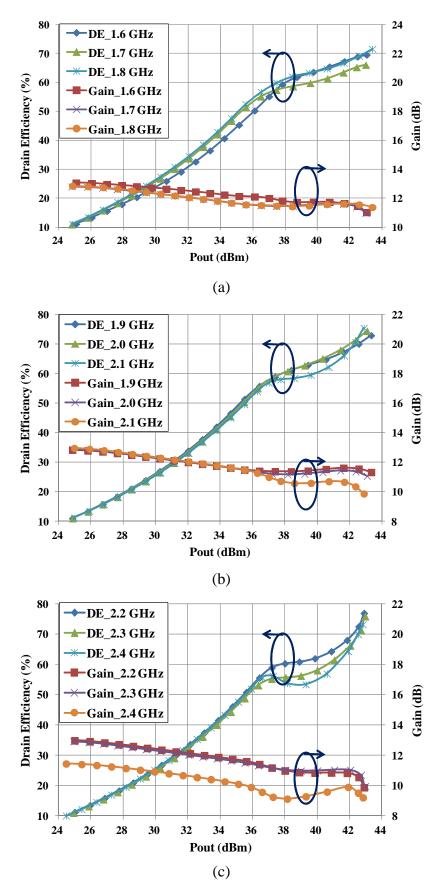

| Fig. | 6.16 Simulated drain efficiency and gain performance of the proposed DPA: (a) |

|------|-------------------------------------------------------------------------------|

|      | 1.6-1.8 GHz; (b) 1.9-2.1 GHz; (c) 2.2-2.4 GHz114                              |

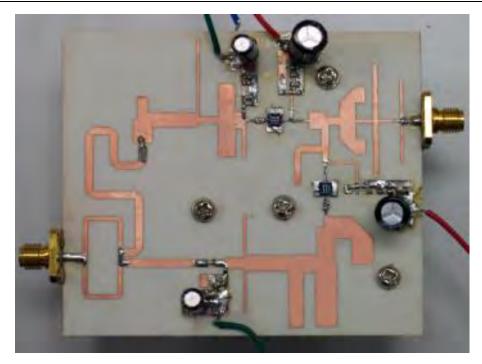

| Fig. | 6.17 Photograph of the fabricated DPA115                                      |

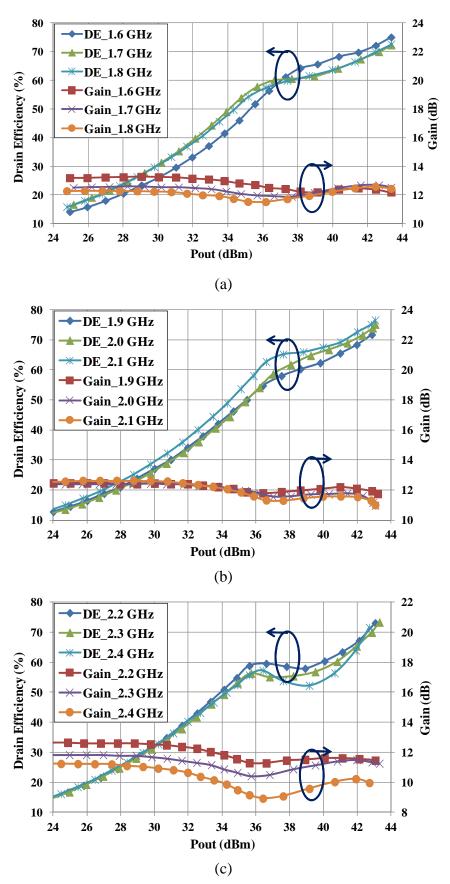

| Fig. | 6.18 Measured drain efficiency and gain performance of the proposed DPA: (a)  |

|      | 1.6-1.8 GHz; (b) 1.9-2.1 GHz; (c) 2.2-2.4 GHz116                              |

| Fig. | 6.19 Measured and Simulated drain efficiency (at saturation level and 6 dB    |

|      | back-off) and saturation output power117                                      |

| Fig. | 6.20 Measured average drain efficiency and ACLR (WCDMA test signal at an      |

|      | average output power of 37 dBm)118                                            |

| Fig. | 6.21 Measured output spectrum of proposed design (WCDMA test signal at 2      |

|      | GHz with an average output power of 37 dBm)118                                |

## List of Tables

| Table 1.1 The Service Frequency Band of Various Communication Standard of China            |

|--------------------------------------------------------------------------------------------|

| Unicom5                                                                                    |

| Table 1.2 Calculated ACLR Values (Fig. 1.9)    10                                          |

| Table 2.1 Summary of voltage component amplitudes and the corresponding                    |

| enhancement22                                                                              |

| Table 2.2 Summary of PA performance under various operation mode ( $V_{max}=I_{max}$       |

| =1)                                                                                        |

| Table 4.1 Computed Operation Parameters for $I_{qM} = 0.02 I_{MAX}$                        |

| Table 4.2 Optimum Input and Output Loads of Main and Auxiliary Devices (CCL                |

| DPA)                                                                                       |

|                                                                                            |

| Table 4.3 Simulation and Measurement Results of the Proposed and the                       |

| Table 4.3 Simulation and Measurement Results of the Proposed and the      Conventional DPA |

| -                                                                                          |

| Conventional DPA66                                                                         |

| Conventional DPA                                                                           |

# **Chapter 1**

## Introduction

### **1.1 Design Challenges of RF Power Amplifier**

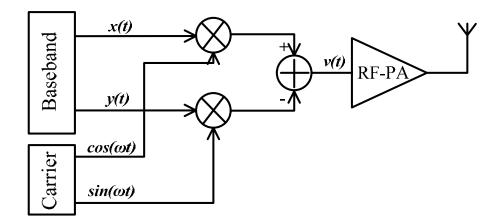

As the key component of transmitter (Fig. 1.1), RF power amplifier has been extensively studied for decades [1]-[3]. Ideally, a traditional PA should amplify the input signal to the desired power level, without consuming too much dc power or sacrifice of signal quality. As modern communication system evolves for higher spectrum efficiency and data transmission rate, the emergence of new communication standards with advanced signal formats lead to two major challenges in PA design, namely: 1) the efficient amplification of signal with high Peak-to-Average Power Ratio (PAPR); and 2) the support of wideband operation (wide bandwidth and multi-carrier).

Fig. 1.1 The simplified diagram of transmitter

#### **1.1.1 Peak-to-Average Power Ratio (PAPR)**

In the study of RF PA design, one of the most important parameters is the Peak-to-Average Power Ratio (PAPR) of signals, which is defined as the ratio of signal peak power to average power. In general, the modulated signal v(t) can be written as:

$$v(t) = A(t) \cdot \cos[\omega t + \theta(t)]$$

(1.1)

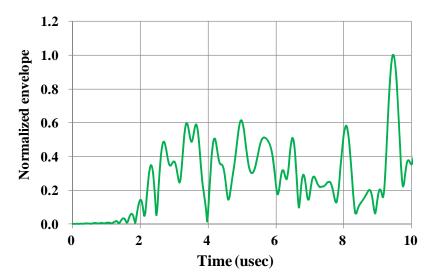

where A(t) and  $\theta(t)$  are the envelope and phase function of the signal. Fig. 1.2 shows the time domain waveform (envelope variation) of a typical WCDMA channel. Since the instantaneous power level (envelope) of a complex modulated signal is changing with time, the Probability Density Function (PDF) is commonly used to illustrate the energy distribution of the signal.

Fig. 1.2 Time domain waveform of the envelope of a typical WCDMA signal

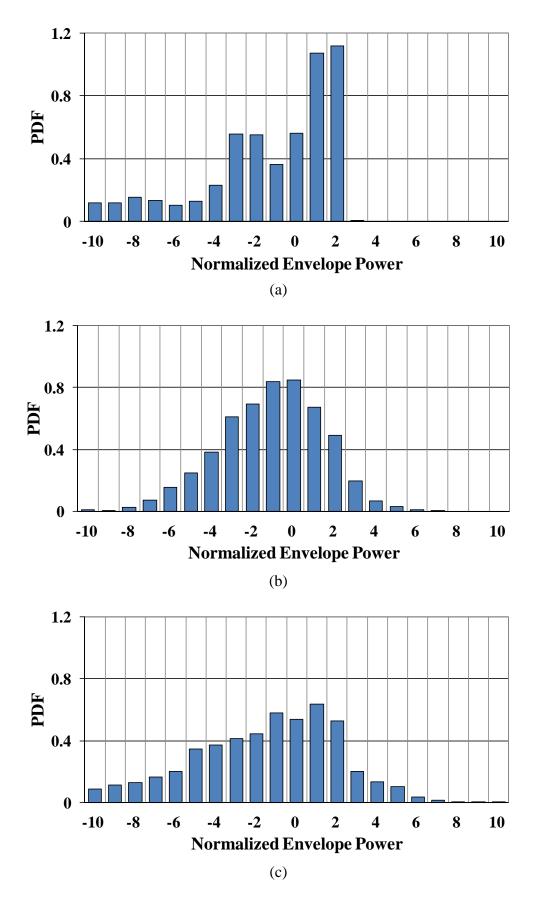

Fig. 1.3 shows the PDF of modulated signals of various formats (EDGE, WCDMA, LTE). Although the use of signal with constant-envelope (i.e. 2G GMSK system) can largely increase the efficiency of RF PA (operating near saturation), the associated

Fig. 1.3 PDF of modulated signals with various formats (envelope power normalized to average power): (a) EDGE signal; (b) WCDMA signal; (c) LTE signal.

channel capacity is rather poor (low data rate). As the mobile services become popular, the surge in data-rate demands higher spectrum efficiency as well as channel capacity. Therefore, in 2.5G EDGE system and 3G WCDMA system, advanced modulation schemes has been introduced, to improve spectrum efficiency but with the major drawback of non-zero PAPR value (3-6 dB). In the latest LTE system, the introduction of Orthogonal Frequency Division Multiplexing (OFDM) can further increase the data-rate and reduce the impact of multipath fading and interference. However, the multicarrier basis of OFDM significantly raises the value of signal PAPR to almost 10 dB.

The increased PAPR has caused a serious problem: if the modulated signal is amplified by a PA with full rated output power (maximum efficiency), the signal will be largely distorted due to the nonlinearity of PA. However, if the drive power level is backed off from the saturation (eliminate the distortion), the efficiency of PA will drop substantially, which lead to increased heat dissipation. For instance, the amplification of WCDMA signal by the conventional class AB PA (with power back-off) has an overall efficiency of below 20%. Therefore, efficient amplification of high PAPR signal has become a major challenge in PA design.

#### **1.1.2 Wideband operation**

It is well known that the available data transmission rate is proportional to signal bandwidth. Besides, the evolution of new communication standards also brings along signal with aggregated bandwidth. For example, in the LTE advanced system, the

| Generation | Format  | Working Band (MHz)   |                      |

|------------|---------|----------------------|----------------------|

| 2G         | GSM     | Up link: 909-915     | Down link: 954-960   |

| 2G         | GSM     | Up link: 1745-1755 I | Down link: 1840-1850 |

| 3G         | WCDMA   | Up link: 1940-1955 I | Down link: 2130-2145 |

| 4G         | LTE-FDD | Up link: 1755-1765 I | Down link: 1850-1860 |

| 4G         | LTE-FDD | Up link: 1955-1980 I | Down link: 2145-2170 |

| 4G         | LTE-TDD | 2300-2320            |                      |

| 4G         | LTE-TDD | 2555-2575            |                      |

Table 1.1The Service Frequency Band of Various Communication Standard of China Unicom

signal bandwidth can be as large as 100MHz.

Moreover, due to various reasons, multiple communication standards (2G/3G/4G) will co-exist for some time. Table 1.1 lists the frequency bands of mobile service offered by China Unicom. It is clear that, signals of different formats are transmitted at different frequency bands. Therefore, a wideband PA supporting multiple communication bands can reduce hardware complexity and implementation cost (compared to one PA for each standard).

#### **1.2 Performance Evaluation of RF Power Amplifier**

Apart from the major challenges (efficiency and bandwidth mentioned above), other operation factors of PA, including output power, linearity and Power Utilization Factor (PUF), are equally essential in practice. In this section, the performance evaluation of PA is briefly summarized.

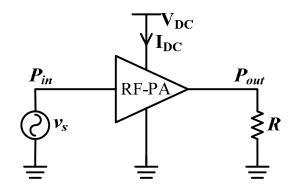

Fig. 1.4 Simplified diagram of RF PA

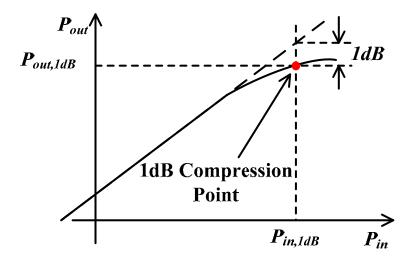

Fig. 1.5 The typical output power performance as a function of input power

#### **1.2.1 Output power**

The output power of PA normally refers to the fundamental power or the average power level over the band of interest transmitted to the load (Fig. 1.4). Fig. 1.5 depicts the typical output power performance of PA as a function of input power. The 1dB compression point ( $P_{out, 1dB}$ ) is often used to indicate the power handling capacity of PA, and is defined as (all output power are measured in dBm):

$$P_{out,linear} - P_{out,1dB} = 1dB \tag{1.2}$$

Fig. 1.6 Theoretical drain efficiency behavior of the Class A PA

#### **1.2.2 Efficiency**

An efficient PA will not only decrease power consumption, but also lower down the heat dissipation and simplify the cooling system. Therefore, efficiency has been considered as one of the most critical parameters in PA design. Referring to Fig. 1.4, the dc power consumption, Drain Efficiency (DE) and Power Added Efficiency (PAE) can be obtained by the following expressions:

$$P_{dc} = V_{dc} I_{dc} \tag{1.3}$$

$$DE = \frac{P_{out}}{P_{dc}} \tag{1.4}$$

$$PAE = \frac{P_{out} - P_{in}}{P_{dc}}$$

(1.5)

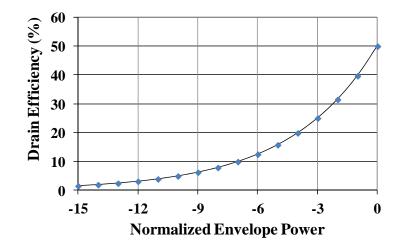

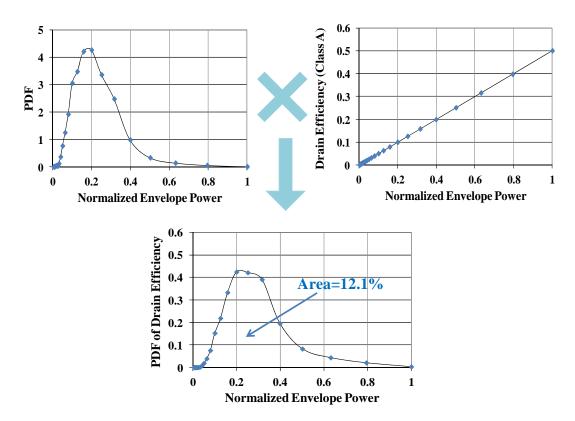

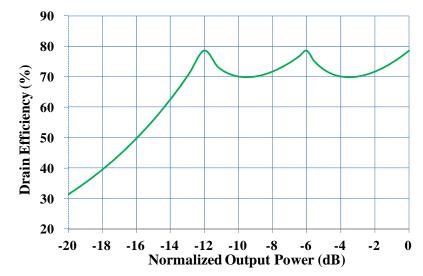

Fig.1.6 shows the theoretical drain efficiency behavior of class A PA under CW stimulation. For modulated signal, the average drain efficiency will depend on both efficiency curve of PA as well as the probability distribution function of the transmitted signal:

Average

$$DE = \int_{0}^{P_{MAX}} DE(p) \cdot PDF(p) \cdot dp$$

(1.6)

As shown in Fig. 1.7, the average drain efficiency of conventional class A PA with WCDMA signal excitation (6dB PAPR) is only 12%.

Fig. 1.7 Evaluation of average drain efficiency under modulated signal

#### **1.2.3 Linearity**

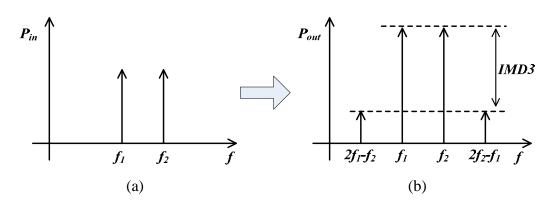

Due to the nonlinear characteristics of transistors, distortion component (IMD) will be generated at the output of PA. Third order Inter-modulation Distortion (IMD3) is commonly used to characterize the linearity of PA. Under a two-tone input signal (Fig. 1.8), IMD3 is defined as:

$$IMD3_{L} = P_{out}(f_{1}) - P_{out}(2f_{1} - f_{2})$$

(1.7)

$$IMD3_{H} = P_{out}(f_{2}) - P_{out}(2f_{2} - f_{1})$$

(1.8)

Fig. 1.8 Input and output spectrum of PA (Two-tone test): (a) Input; (b) Output.

For complex modulated signal test, Adjacent Channel Leakage Ratio (ACLR) is introduced to account for the effect of spectrum re-growth (Fig.1.9). It is defined as the ratio between the regenerated power in the adjacent channel and the power of desired signal:

$$ACLR_{L(H)} = \frac{\int\limits_{L(H)} P_{out}(f) \cdot df}{\int\limits_{B} P_{out}(f) \cdot df}$$

(1.9)

Based on the spectrum shown in Fig.1.9, the corresponding values of ACLR (low and upper bands) are evaluated and listed in Table 1.2.

#### **1.2.4 Power Utilization Factor**

Since the microwave transistor is usually considered to be the most expensive component in PA construction, the full utilization of device capacity is thus highly desirable. Consequently, Power Utilization Factor (PUF) [1], is introduced as a measure of the effective use of device capacity (with reference to the same device operating in class A mode):

$$PUF = \frac{P_{out(Class under study)}}{P_{out(Class A)}}$$

(1.10)

9

Table 1.2 Calculated ACLR Values (Fig. 1.9)

Fig. 1.9 Output Spectrum density of typical PA under complex modulated signal

$P_{out}$  is determined by the breakdown voltage ( $V_{max}$ ), the fully open-channel drain current ( $I_{max}$ ) and the operation mode of the device. For Class A operation, the maximum available power is simply given by (maximum fundamental voltage and current swing of  $V_{max}/2$  and  $I_{max}/2$ ):

$$P_{out(Class A)} = \frac{V_{\max} I_{\max}}{8}$$

(1.11)

For cost effectiveness, the PUF should be made as large as possible by proper selection of bias point as well as the optimal control of drain voltage and current waveforms.

## 1.3 Motivation and outline of this work

As introduced in Section 1.1, wideband operation and efficient amplification of high PAPR signal are prime requirements for base-station PA design. It is well known that conventional PA architectures suffer from poor overall efficiency and thus generate excessive heat dissipation. Various techniques have been proposed for efficiency enhancement, and Doherty Power Amplifier (DPA) [4] has been regarded as the most popular approach due to its circuit simplicity and moderate linearity. Although the adoption of DPA for narrowband applications with low PAPR signal has been successfully demonstrated in the past decade, two major limitations are still required to be solved for advanced communication systems:

1. Classical Doherty amplifier can offer high efficiency range of 6 dB only, which is considered to be inadequate as many modern communication standards are having signal formats with ever-increasing value of PAPR. Therefore, the high efficiency range of DPA needs to be extended for further efficiency enhancement.

2. In theory, the classical DPA configuration can achieve high efficiency at saturation over wide frequency band. However, the back-off efficiency degrades substantially due to the narrowband nature of simple quarter-wavelength transformer. In [5], a modified configuration was suggested to extend the bandwidth of DPA, but at the expense of PUF (0.5). Therefore, a wideband DPA configuration with improved PUF is highly attractive.

In this thesis, three novel ideas relating to DPA designs with extended high efficiency range or bandwidth are presented. In the first work, DPA design with Complex Combining Load (CCL) is presented to extend the high efficiency range of DPA. With the replacement of conventional resistive combining load by complex combining load, the high efficiency region of DPA can be extended without multi-cell or asymmetrical implementation. As the fixed CCL method is not favorable for wideband operation, a new DPA design using frequency-varying CCL is exploited with special input current control. Finally, to improve PUF performance, a new DPA configuration using band-pass auxiliary transformer has been investigated. For comparison purpose, the broadband performance of the proposed and conventional topologies are analyzed and simulated. Issues relating to the realization of matching networks and optimum phase control are also addressed.

The contents are organized as follows: In chapter 2, the classical theory on high efficiency PA design is introduced. Chapter 3 reviews some resent DPA design methodologies for the enhancement of high efficiency range or bandwidth. The complex combining load method which can boost high efficiency range without the need of asymmetrical or multi-cell configuration is introduced in Chapter 4; This method is extended in Chapter 5 to include frequency varying complex combining load for improvement in the operating bandwidth; In Chapter 6, a band-pass auxiliary transformer is introduced to the design of broadband Doherty amplifier with attained PUF of almost unity. Finally, conclusions are drawn in Chapter 7 with topics for future research.

### Reference

- [1] S. Cripps, *RF Power Amplifiers for Wireless Communications*. 2nd ed. Norwood, MA: Artech House, 2006.

- [2] P. Reynaert and M. Steyaert, *RF Power Amplifiers for Mobile Communications*, ser. Analog Circuits and Signal Processing. Amsterdam, The Netherlands: Springer, 2006.

- [3] Paolo Colantonio, Franco Giannini and Ernesto Limiti, *High Efficiency RF and Mircowave Solid State Power Amplifiers*. John Wiley & Sons, Ltd, 2009.

- [4] W. H. Doherty, "A new high efficiency power amplifier for modulated waves," Proc. IRE, vol. 24, no. 9, pp. 1163–1182, Sep. 1936.

- [5] Y.-T. Wu and S. Boumaiza, "A modified Doherty configuration for broadband amplification using symmetrical devices," *IEEE Trans. Microw. Theory Techn.*, vol. 60, no. 10, pp. 3201–3213, Oct. 2012.

## Chapter 2

# **Classical Theory on High Efficiency Power Amplifier Design**

This chapter covers some basic theories of traditional PA configuration, high efficiency operation modes and some commonly used efficiency enhancement techniques.

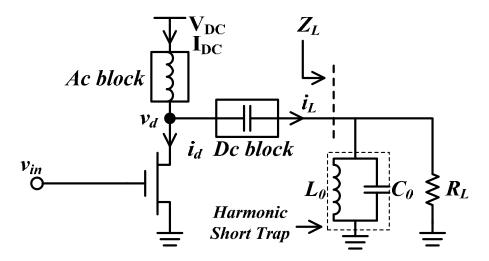

Fig. 2.1 Simplified diagram of PA

### 2.1 Traditional operation modes: Class A, AB, B and C

Fig. 2.1 shows the simplified circuit diagram of RF PA. The shunt LC tank is used as the harmonic trap to create a low impedance (short-circuit) for the proper drain load termination at all harmonic frequencies. As a result, we have

$$Z_{L} = \begin{cases} R_{L} & f = f_{0} \\ 0 & f = 2f_{0}, 3f_{0} \cdots \end{cases}$$

(2.1)

For the sake of simplicity, the following assumptions are used:

1) The drain source breaddown voltage  $V_{max}$  and fully opened channel drain current  $I_{max}$  are normalized to be 1;

2) The threshold gate voltage is assumed to be 0. The maximum drive level  $V_{inmax}$  (corresponds to saturation current  $I_{max}$ ) is assumed to be 1;

3) The transistor is modeled as a voltage controlled current source with unity transconductance ( $i_d = v_{in}$ ), zero output conductance and zero knee voltage;

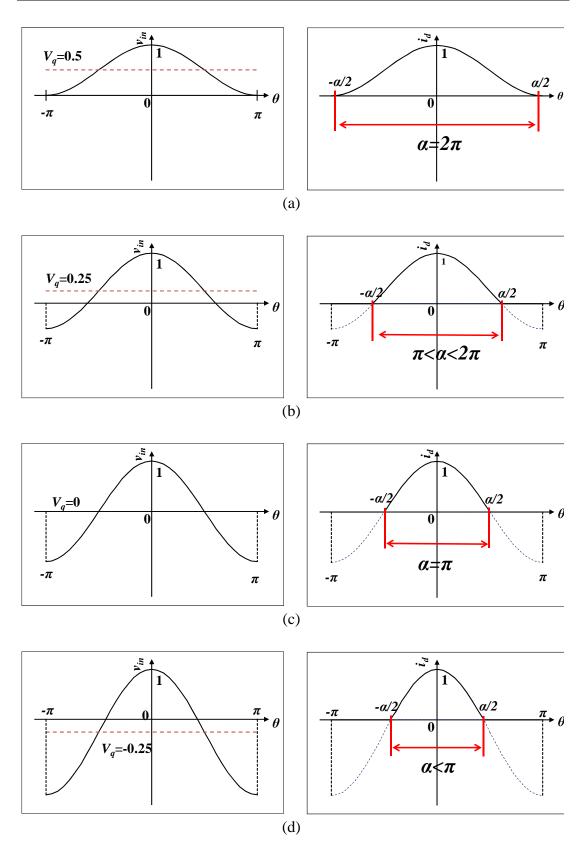

Referring to Fig. **2.**2, the conventional operation modes of PA is classified by the conduction angle which represent the relative conduction time of device inside a RF cycle. For an input signal with the form of:

$$v_{in} = V_q + V_{pk} \cos(\theta) \tag{2.2}$$

where  $V_q$ ,  $V_{pk}$  are the gate quiescent bias and RF swing of the input signal respectively. If the gate drive signal is always above the threshold voltage (Fig. 2.2(a)), then the transistor will conduct all the time with the conduction angle  $\alpha = 2\pi$ . If  $V_q < V_{pk}$ , over a certain period of RF cycle, the gate voltage could fall to below the threshold voltage (the transistor is cut off with zero drain current). Based on the value of conduction angle, the amplifier can be classified as: class A with  $a=2\pi$  (Fig. 2.2(a)), class AB with  $\pi < a < 2\pi$  (Fig. 2.2(b)), class B with  $\alpha = \pi$  (Fig. 2.2(c)) and class C with  $a < \pi$  (Fig. 2.2(d)), and the drain current of the reduced conduction angle modes can be written as:

$$i_{d} = \begin{cases} I_{q} + I_{pk} \cos(\theta) & -\alpha / 2 \le \theta \le \alpha / 2\\ 0 & \pi < \theta < -\alpha / 2 ; \alpha / 2 < \theta < \pi \end{cases}$$

(2.3)

in which  $I_{q(pk)}=V_{q(pk)}$ , and  $\cos(a/2)=-I_{q'}/I_{pk}$ . The gerenal expression for drain current

Fig. 2.2 Traditional operation modes: (a) Class A; (b) Class AB; (c) Class B; (d) Class C

(inside conduction period) can therefore be written as:

$$i_d = \frac{I_{\max}}{1 - \cos(\alpha/2)} (\cos(\theta) - \cos(\alpha/2))$$

(2.4)

For class A operation, it is obvious that  $I_{dc}=I_1=I_{max}/2$ . For the other reduced conduction angle modes, the time domain waveform of  $i_d$  are truncated sinewave, and the dc componnet, fundamental and high order harmonic component have to be extracted with Fourier Analysis:

$$I_{dc} = \frac{1}{2\pi} \int_{-\alpha/2}^{\alpha/2} \frac{I_{\text{max}}}{1 - \cos(\alpha/2)} \cdot (\cos(\theta) - \cos(\alpha/2)) d\theta$$

(2.5)

$$I_n = \frac{1}{\pi} \int_{-\alpha/2}^{\alpha/2} \frac{I_{\max}}{1 - \cos(\alpha/2)} \cdot (\cos(\theta) - \cos(\alpha/2)) \cdot \cos(n\theta) d\theta$$

(2.6)

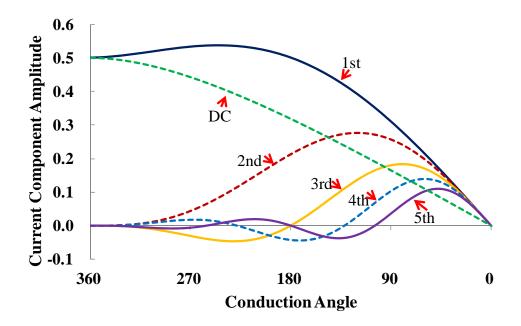

Fig. 2.3 shows the plots of  $I_{dc}$  and  $I_n$  (n=1, 2,  $\cdots$  5) as a function of  $\alpha$ . Subsequently, the drain voltage can be expressed as:

$$v_{ds} = V_{DC} - i_d Z_L = V_{DC} - I_1 R_L \cos(\theta) = V_{DC} - V_{d1} \cos(\theta)$$

(2.7)

where  $V_{d1}$  is the fundamental drain voltage swing. Consider that  $v_{ds}$  should be confined in [0,  $V_{max}$ ], to maximize output power we have:

$$V_{DC} = V_{d1} = V_{\max} / 2 \tag{2.8}$$

Subsequently, the optimum drain load for maximum output power is given by:

$$R_{opt} = V_{DC} / I_1 \tag{2.9}$$

Finally, the output power, dc consumption and drain efficiency can be calculated as follows:

$$P_{out} = V_{d1}I_1 / 2 \tag{2.10}$$

$$P_{dc} = V_{DC} I_{DC} \tag{2.11}$$

$$DE = P_{out} / P_{dc} \tag{2.12}$$

Fig. 2.3 Fourier analysis of drain current

Fig. 2.4 Calculated maximum output power, drain efficiency , optimum drain load and gain as the function of conduction angle

For comparison purposes, a normalized gain  $(=P_{out}/P_{in})$  is also evaluated under the assumption of  $P_{in} = 0.5V_{pk}^2$ . Fig. 2.4 shows the variation of maximum output power (normalized with respect to class A mode), drain efficiency, optimum drain

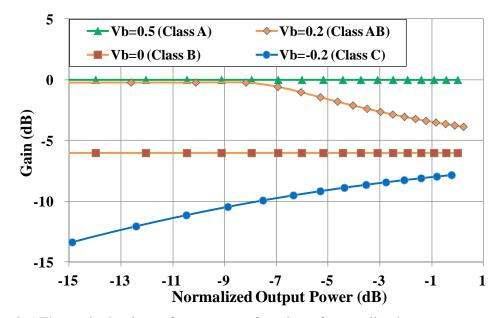

Fig. 2.5 Theoretical gain performace as a function of normalized output power under different operation mode

load and gain as the function of  $\alpha$ . It is clear that as  $\alpha$  decreases, drain efficiency increases monotonically with substantial reduction of gain. The output power slightly increases initially (class AB region), and falls back to class A level with class B operation, and drops sharply under class C operation.

Fig. 2.5 shows the gain performace as a function of normalized output power under different operation mode. In the ideal case, class AB mode will exhibit gain compression while class A and B modes have entirely linear response. However, with real devices, the low quesicent bias of device in class AB mode can generate a certain amount of gain expansion [1] which cancells out the gain compression, and eventually lead to linear operation similar to class A mode. In summary, class AB mode can provide the best tradeoff between effficiency, gain, output power and linearity, thus is the most frequently adopted mode in practice.

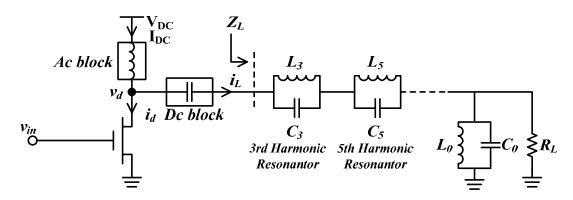

Fig. 2.6 Simplified diagram of Class F amplifier

## 2.2 High Efficiency mode: class F

In the previous section, several operation modes of PA has been analysed under the condition that all harmonic components of the drain voltage are set to zero. For the partipular class B mode of half-period conduction time, the efficiency can be improved to 78.5%. This section introduces class F operation which employs odd harmonic voltages to enhance both efficiency and output power. As the drain voltage is reshaped from sinewave to square wave, the drain efficiency can achieve a theoretical value of 100%.

Fig. 2.6 shows the simplified diagram of class F amplifier. The parallel renonators are inserted to create the required odd harmonic voltage. Hence, the drain voltage can be writen as:

$$V_d = V_{dc} - V_{d1}\cos(\theta) + V_{d3}\cos(3\theta) - V_{d5}\cos(5\theta) + \cdots$$

=  $V_{dc}[1 - k_1\cos(\theta) + k_3\cos(3\theta) - k_5\cos(5\theta) + \cdots]$  (2.13)

The flattening process of drain voltage waveform is shown in Fig. 2.7. If a small amount of third harmonic (with positive  $k_3$ ) is introduced under class B operation (Fig. 2.7 (a)), the peak-to-peak swing of the composite waveform would be reduced

Fig. 2.7 Drain voltage flatting process from Class B to Class F: (a) Class B; (b) Class F with 3rd harmonic peaking; (c) Class F with 3rd and 5th harmonic peaking; (d) Class F with infinite odd harmonics

from the orginal value of  $V_{max}$ . Therefore, the presence of third harmonic allows the increase of fundamental ampliftude from  $V_{max}/2$  to a higher level, thus enhancing the output power. On the other hand, the reshaped waveform also reduces the heat dissipation (higher drain efficiency) as the overlapping (time-domain waveforms) between the drain voltage and current (Fig. 2.7(b)) is reduced. The addition of fifth harmonic has a similar effect on the shaping of voltage waveform (Fig. 2.7(c)). Finally, with infinite odd harmonics, a square wave (Fig. 2.7(d)) can be formed (with zero overlap between voltage and current), which implies 100% conversion between

#### **Chapter 2 Classical Theory on High Efficiency Power Amplifier Design**

| Summary of votage component amplitudes and the corresponding emancement |         |        |          |             |                 |  |

|-------------------------------------------------------------------------|---------|--------|----------|-------------|-----------------|--|

| Class                                                                   | k1      | k3     | k5       | Peak DE (%) | Normalized Pout |  |

| В                                                                       | 1       |        |          | 78.5        | 1               |  |

| F3                                                                      | 9/8     | 1/8    |          | 88.4        | 1.125           |  |

| F5                                                                      | 75/64   | 25/128 | 3/128    | 92.0        | 1.172           |  |

| F∞                                                                      | $4/\pi$ | 4/3π   | $4/5\pi$ | 100         | 1.273           |  |

Table 2.1 Summary of voltage component amplitudes and the corresponding enhancement

dc power to rf power with zero heat dissipation, zero harmonic power and 100% drain efficiency. Table 2.1 summarizes the amplitude coefficient extracted by the maximum flat condition [2] and the corresponding enhancement performances in power and efficiency.

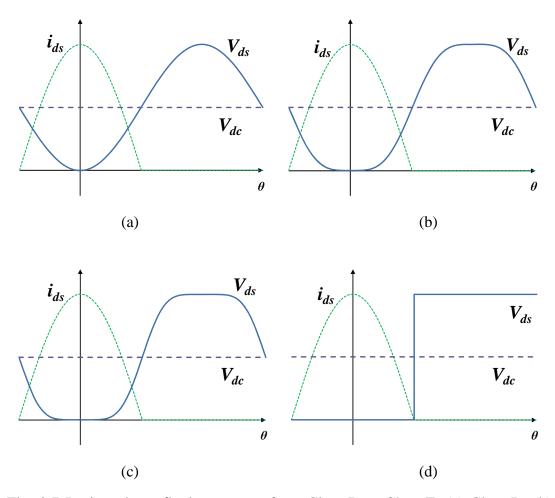

## 2.3 The switching mode: Class E

Compared to the previous PA designs, the major feature of Class E PA is the strong nonlinearity due to the switching mode behavior. Although the Class AB and C do not process strictly linear gain performance, amplitude of the input and output signals are still related. In Class E operation, the transistor is modeled as a switch, thus the standalone Class E PA is not suitable for amplifying AM signal. However, for constant envelope signal with only phase information, Class E PA can be applied with theoretical drain efficiency as high as 100%. Moreover, Class E PA is commonly employed in the Envelope Elimination & Restoration (EER) Technique (to be covered in Section 2.4).

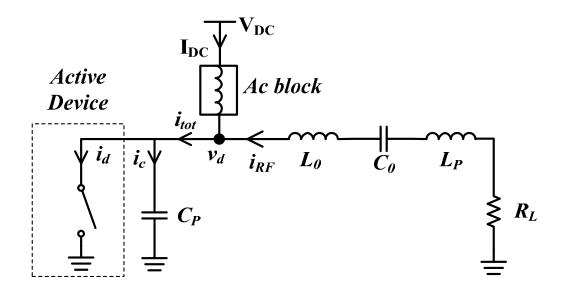

Fig. 2.8 shows the simplified diagram of class E PA. The series  $L_0$ - $C_0$  resonator is used to suppress the high-order harmonic current in  $i_{rf}$  (only the fundamental

Fig. 2.8 The simplified diagram of class E amplifier

Fig. 2.9 Theoretical drain current and voltage waveforms of Class E amplifier under 50% duty cycle

component is kept):

$$i_{RF} = I_{RF}\sin(\theta) \tag{2.14}$$

Therefore, the total current (Fig. 2.9(a)) flows to the switch and capacitor:

$$i_{tot} = I_{DC} + I_{RF}\sin(\theta) \tag{2.15}$$

In the switch-ON period, all the current flows to the device branch with zero current across the shunt capacitor. Reversely, all the current flows to the capacitor in the switch-OFF period. Fig. 2.9(b) and (c) depicts the time domain waveform of  $i_d$  and  $i_c$ , which can be written as:

$$i_{d} = \begin{cases} I_{DC} + I_{RF} \sin(\theta) & Switch - ON \ Period \\ 0 & Switch - ON \ Period \end{cases}$$

(2.16)

$$i_{c} = \begin{cases} 0 & Switch - ON \ Period \\ I_{DC} + I_{RF} \sin(\theta) & Switch - ON \ Period \end{cases}$$

(2.17)

Fig. 2.9(d) shows the waveform of  $v_d$  which can be calculated from the time domain integration of  $i_c$ . Although the device is modelled as a lossless switch, the switching loss would still exist (non-zero drain voltage when the switch is turned on). Therefore, the Zero Voltage Switching (ZVS) is imposed to minimize the switching loss:

$$v_d \Big|_{turn-on} = 0 \tag{2.18}$$

On the other hand, in practical case, the switch transition time between on and off state is not zero, and the overlap of voltage and current in this duration would lead to heat dissipation. Therefore, the Zero Voltage Derivative Switching (ZVDS) is also imposed, which helps to minimize the switch current when device turns on:

$$\frac{dv_d}{d\theta}\Big|_{turn-on} = 0 \tag{2.19}$$

| Summary of PA performance under various operation mode ( $V_{max}=I_{max}=1$ ). |          |          |             |              |  |  |  |

|---------------------------------------------------------------------------------|----------|----------|-------------|--------------|--|--|--|

| Class                                                                           | $V_{dc}$ | $I_{dc}$ | Peak DE (%) | Maximum Pout |  |  |  |

| В                                                                               | 0.5      | 0.318    | 78.5        | 0.125        |  |  |  |

| F                                                                               | 0.5      | 0.318    | 100         | 0.159        |  |  |  |

| Е                                                                               | 0.281    | 0.349    | 100         | 0.098        |  |  |  |

Table 2.2 Summary of PA performance under various operation mode  $(V_{max}=I_{max}=1)$

With the conditions of (2.18) and (2.19), circuit parameters ( $C_p$ ,  $L_p$ ,  $R_L$ ) can be calculated for a given output power level [3]. The typical drain current and voltage waveforms shown in Fig. 2.9 (b) and Fig. 2.9 (d) exhibit no harmonic power dissipation, zero overlapping (time-domain) and 100% drain efficiency.

Table 2.2 summarizes the maximum output power and drain efficiency performance of various operation modes. It is clear that class E mode possesses the lowest the output power capability due to the highest voltage peak. Another drawback is that, as class E theory is constructed based on a switching device, normally the standalone class E amplifier is not suitable for handling signal with amplitude modulation.

## **2.4 Efficiency Enhancement Techniques**

As mentioned previously, the conventional PA can only provide peak efficiency at the highest output power level while transmitting signal generally possesses large peak-to-average ratio, which lead to poor overall efficiency. Therefore, various efficiency enhancement techniques have been introduced to efficiently amplify signal with amplitude modulation.

## 2.4.1 Doherty amplifier

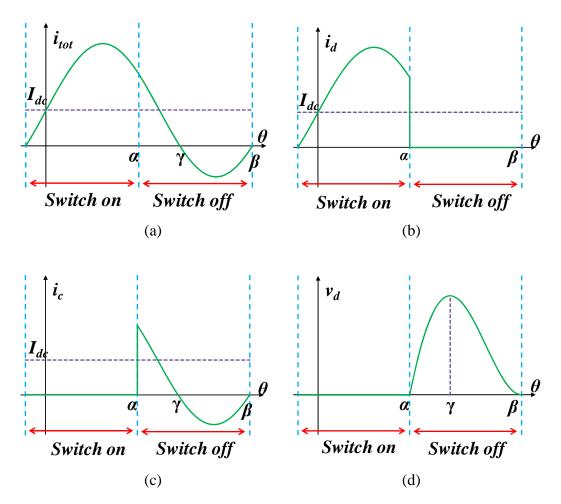

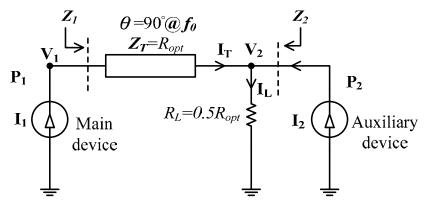

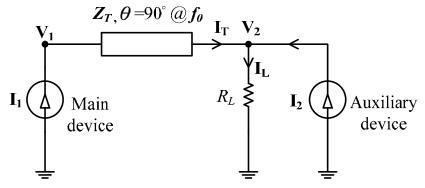

The popularity of Doherty Power Amplifier (DPA) mainly attributes to its ability of providing high efficiency in an extended power range with simply circuitry. As shown in Fig. 2.10, a total of four building blocks are involved: main device, auxiliary device, a quarter-wavelength Transmission Line (TL) and a resistive load  $R_L$ .

Fig. 2.10 Simplified diagram of the Doherty amplifier

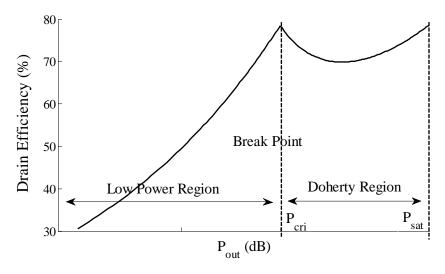

Fig. 2.11 Typical drain efficiency behavior of the Doherty amplifier

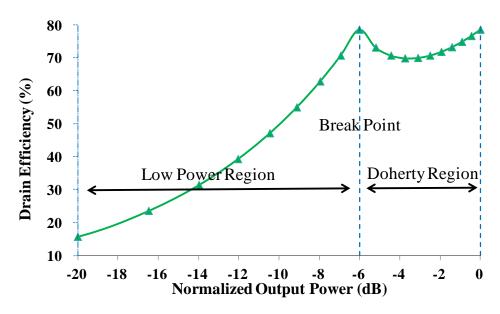

As depicted in Fig. 2.11, there are two operating regions for a typical Doherty amplification: the low power region and Doherty region. In the low power region, the auxiliary device is off, and the Doherty amplifier is acting as a conventional PA. As a result, the main device is loaded by a fixed impedance given by:

$$Z_{1cri} = \frac{Z_T^2}{R_L}$$

(2.20)

The break point denotes the transition of operation regions (turning-on of auxiliary device), and it is also the location of the first efficiency peak (the fundamental drain voltage  $V_1$  should reach its peak value  $V_{1sat}$ ).

Inside the Doherty region, with the injection current of the auxiliary device, the value of the drain load  $Z_I$  become dynamic and can be modulated to keep  $V_I$  staying at  $V_{Isat}$  even for the higher output power level (thus high efficiency is maintained inside Doherty region). The ABCD matrix of the combination of impedance inverter and the load  $R_L$  can be written as:

$$\begin{bmatrix} \mathbf{V}_1 \\ \mathbf{I}_1 \end{bmatrix} = \begin{bmatrix} jZ_T / R_L & jZ_T \\ j / Z_T & 0 \end{bmatrix} \begin{bmatrix} \mathbf{V}_2 \\ -\mathbf{I}_2 \end{bmatrix}$$

(2.21)

Thus we have:

$$\mathbf{V}_{1} = Z_{T} \left( \frac{Z_{T}}{R_{L}} \cdot \mathbf{I}_{1} - j \cdot \mathbf{I}_{2} \right)$$

(2.22)

$$\mathbf{V}_2 = -j \cdot \mathbf{I}_1 Z_T \tag{2.23}$$

To extract maximum power, it is obvious that  $I_2$  should be  $\pi/2$  behind  $I_1$  in phase. If  $\alpha_c$  and  $\alpha_v$  are the current ratio (= $I_{2sat}/I_{1sat}$ ) and voltage ratio (= $V_{2sat}/V_{1sat}$ ) at saturation respectively, the dynamic drain load  $Z_1$  can therefore be represented as:

$$Z_1 = Z_T \left(\frac{Z_T}{R_L} - \frac{I_2}{I_1}\right) = \frac{V_{1sat}}{I_1}$$

(2.24)

At saturation, the main device should be terminated by the optimum load  $R_{opt}$  (= $V_{1sat}/I_{1sat}$ ), and hence, we have:

$$Z_{1sat} = Z_T \left(\frac{Z_T}{R_L} - \alpha_C\right) = R_{opt}$$

(2.25)

$$\alpha_{V} = \frac{V_{2sat}}{V_{1sat}} = \frac{I_{1sat}Z_{T}}{V_{1sat}} = \frac{Z_{T}}{R_{opt}}$$

(2.26)

As the auxiliary current increases, the drain load is modulated from  $Z_{1cri}$  to  $Z_{1sat}$ , where  $\beta_d$  is the dynamic load span defined by:

$$\beta_d = \frac{Z_{1cri}}{Z_{1sat}} = \frac{Z_{1cri}}{R_{opt}}$$

(2.27)

From (2.25)-(2.27), the following formulas can thus be found:

$$\beta_d = 1 + \alpha_C \alpha_V \tag{2.28}$$

$$Z_T = \alpha_V R_{opt} \tag{2.29}$$

$$R_{L} = \frac{\alpha_{V}^{2}}{1 + \alpha_{C} \alpha_{V}} R_{opt}$$

(2.30)

Fig. 2.12 Parameter Profiles for Doherty operation: (a) Drain current; (b) Drain Voltage; (c) Drain load;

Subsequently, the output power level for the first and second efficiency peak can be expressed as follows:

$$P_{cri} = P_{1cri} = \frac{V_{1sat}^{2}}{2\beta_{d}R_{opt}}$$

(2.31)

$$P_{sat} = P_{1sat} + P_{2sat} = (1 + \alpha_c \alpha_V) \frac{V_{1sat}^2}{2R_{opt}}$$

(2.32)

The Output Back-Off (OBO), which is a measure of the high efficiency range, can be written as:

$$OBO = 10\log(\frac{P_{cri}}{P_{sat}}) = 10\log[\beta_d(1 + \alpha_c \alpha_V)] = 20\log(1 + \alpha_c \alpha_V)$$

(2.33)

In the symmetrical device scenario, both devices process the same saturation current and voltage:

$$\alpha_c = \alpha_v = 1 \tag{2.34}$$

From (2.28)-(2.30), the following relationship can be deduced ( $\beta_d = 2$ ):

$$Z_T = 2R_L = R_{opt} \tag{2.35}$$

The above is the classical configuration proposed by W. Doherty [4], with a theoretical high efficiency range of 6 dB. From (2.24), the required auxiliary current can be written as:

$$I_{2} = \begin{cases} 0 & I_{1} < 0.5I_{1sat} \\ 2I_{1} - I_{1sat} & I_{1} \ge 0.5I_{1sat} \end{cases}$$

(2.36)

The drain current, voltage and load profiles are depicted in Fig. 2.12. If both devices are biased in Class B, the ideal Doherty behavior will be created (Fig. 2.11).

In practice, the main device is often biased in class AB mode while the auxiliary device is biased in class C mode, with a slightly reduction of OBO (~5 dB). Moreover, it has been shown that the IMD components of class AB mode and class C mode amplifiers exhibit anti-phase relationship, and therefore, the linearity of Doherty amplifier is far better than expected due to IMD cancellation.

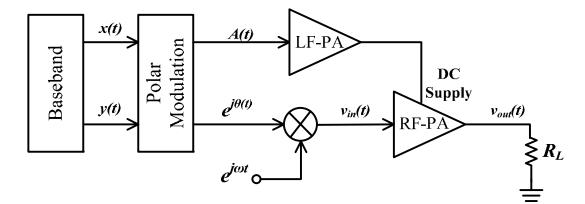

Fig. 2.13 The basic diagram of Envelope Elimination and Restoration (EER) technique

### 2.4.2 Envelope Elimination and Restoration Technique

Fig. 2.13 shows the basic diagram of Envelope Elimination and Restoration (EER) technique. The polar modulation system separates the baseband signal into the amplitude modulation and phase modulation signal components:

$$A(t) = \sqrt{x(t)^{2} + y(t)^{2}}$$

(2.37)

$$\theta(t) = \arctan[\frac{y(t)}{x(t)}]$$

(2.38)

The envelope variation is eliminated in the RF path, and the input signal of the RF PA exhibits constant envelope with only phase modulation. Because of this,

switching mode PA, like Class E amplifier can be adopted with theoretically 100% drain efficiency [5]. On the other hand, the output signal of Class E PA is proportional to the drain supply, and therefore, the envelope signal A(t), after amplified by a low frequency PA, can be applied as the DC supply of the nonlinear RF PA to restore the original waveform:

$$v_{in}(t) = \cos[\omega t + \theta(t)]$$

(2.39)

$$v_{out}(t) = GA(t)v_{in}(t) = GA(t)\cos[\omega t + \theta(t)]$$

(2.40)

Clearly, for the baseband part, the polar modulation system can be easily realized by modern DSP technology. For the RF part, the adoption of nonlinear PA (Class E) is a more efficient solution than linear amplification (Class AB). The single PA design approach takes the advantages of ease of matching and wider bandwidth, in compared with the Doherty amplifier. However, the amplification of the envelope signal (low frequency path) is normally not as efficient as the RF part, which seriously pulls down the overall efficiency. Moreover, the phase relationship between input and output of the RF PA behaves nonlinear when the dc supply is varied, thus extra linearization is required which further complicates the whole design.

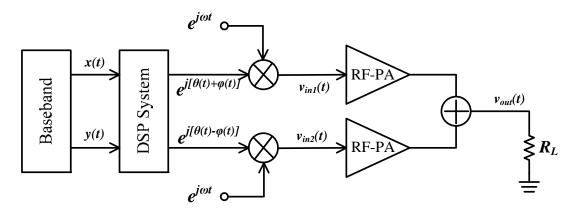

Fig. 2.14 The basic diagram of the conventional outphasing technique

## 2.4.3 Outphasing Technique

Similar to EER technique, the outphasing technique also adopts constant envelope signal and nonlinear amplifiers. Fig. 2.14 shows the basic diagram of the conventional outphasing technique. The baseband signal is given by:

$$g(t) = x(t) + j \cdot y(t) = A(t) \cdot e^{j\theta(t)}$$

(2.42)

where A(t) is the normalized amplitude and  $\theta(t)$  is the phase component. A DSP system is used to generate two phase modulated signals (constant envelope):

$$\cos[\varphi(t)] = A(t) \tag{2.43}$$

If nonlinear PA (with gain of G) is adopted, the amplitude information can be restored at the output:

$$v_{in1}(t) = \cos[\omega t + \theta(t) + \varphi(t)]$$

(2.44)

$$v_{in2}(t) = \cos[\omega t + \theta(t) - \varphi(t)]$$

(2.45)

$$v_{out}(t) = G[v_{in1}(t) + v_{in2}(t)] = 2G\cos[\omega t + \theta(t)]\cos[\varphi(t)] = 2GA(t)\cos[\omega t + \theta(t)]$$

(2.46)

Obviously, the adoption of nonlinear PA helps to reduce heat dissipation, but it is

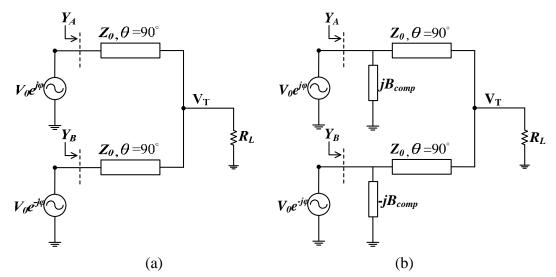

Fig. 2.15 Chireix Outphasing Amplifier: (a) Without compensation for the complex load; (b) With compensation for the complex load.

worth to note that the dc power consumption remains constant regardless of the actual power level. Therefore, the drain efficiency decreases when output power is back off. For average efficiency enhancement, Chireix proposed the usage of a non-isolating combining circuitry [6], as illustrated in Fig. 2.15. Two phase-modulated voltage sources, representing the outputs of the nonlinear PAs, are connected to the combining load ( $R_L$ ) with quarter wavelength transformers. Like Doherty amplifier, the effective drain load of each device in Chireix amplifier is dynamically modulated by the other device. By circuit analysis, it can be shown that ( $\varphi$  is the outphasing angle):

$$P_{out} = \frac{2R_L}{Z_0^2} V_0^2 \cos^2(\varphi)$$

(2.47)

$$Y_{A} = \frac{R_{L}}{Z_{0}^{2}} 2\cos^{2}(\varphi) - j\frac{R_{L}}{Z_{0}^{2}}\sin(2\varphi)$$

(2.48)

$$Y_{B} = \frac{R_{L}}{Z_{0}^{2}} 2\cos^{2}(\varphi) + j \frac{R_{L}}{Z_{0}^{2}} \sin(2\varphi)$$

(2.49)

Fig. 2.16 Drain efficiency behaviors of the Chireix Outphasing Amplifier under various compensation angles.

Note that the drain loads are complex admittance with opposite susceptance, since the active device can only present peak efficiency when the load is purely resistive, and therefore, the compensation components (Fig. 2.15 (b)) are added to cancel the susceptance and improve the efficiency at a given outphasing angle. Referring to Fig. 2.15 (b), we have:

$$Y_{A} = \frac{R_{L}}{Z_{0}^{2}} 2\cos^{2}(\varphi) - j\frac{R_{L}}{Z_{0}^{2}}\sin(2\varphi) + jB_{comp}$$

(2.50)

$$Y_{B} = \frac{R_{L}}{Z_{0}^{2}} 2\cos^{2}(\varphi) + j \frac{R_{L}}{Z_{0}^{2}} \sin(2\varphi) - jB_{comp}$$

(2.51)

$$B_{comp} = \frac{R_L}{Z_0^2} \sin(2\varphi_C)$$

(2.52)

In which  $\varphi_c$  is the compensation angle generated by  $B_{comp}$ . Assume both devices are operating at saturation (Class B mode) [1], the theoretical drain efficiency behavior of the compensated Chireix out-phasing technique can be derived as:

$$\eta(\varphi,\varphi_{c}) = \frac{\frac{\pi}{4}}{\sqrt{1 + \frac{1}{4}(\frac{\sin(2\varphi_{c}) - \sin(2\varphi)}{\cos^{2}(\varphi)})^{2}}}$$

(2.53)

Fig. 2.16 shows the drain efficiency behavior of the Chireix Outphasing amplifier versus normalized output power (=20 log[cos  $\varphi$ ]) under various compensation angle  $\varphi_{\rm C}$ . In the idealized case, high efficiency can be maintained over 10 dB OBO range, two limitations exist in practical outphasing amplifier design [7]: Firstly, as the input power is modulated to be constant level, gain and PAE drops dramatically when output power reduces by outphasing; Secondly, it can be observed that the signal bandwidth becomes much larger (up to 12 times with outphasing angle=90°) when the baseband signal is converted to the outphasing signal. Therefore, the modulation bandwidth is strongly restricted, and the implementation of the outphasing technique become more complex and costly compared to other techniques.

## Reference

- [1] S. Cripps, *RF Power Amplifiers for Wireless Communications*. 2nd ed. Norwood, MA: Artech House, 2006.

- [2] F. H. Raab, "Class-F Power Amplifiers with Maximally Flat Waveforms", IEEE Trans. Microw. Theory Techn., vol. 45, no. 11, pp. 2007–2012, Nov. 1997.

- [3] Paolo Colantonio, Franco Giannini and Ernesto Limiti, *High Efficiency RF and Mircowave Solid State Power Amplifiers*. John Wiley & Sons, Ltd, 2009.

- [4] W. H. Doherty, "A new high efficiency power amplifier for modulated waves," Proc. IRE, vol. 24, no. 9, pp. 1163–1182, Sep. 1936.

- [5] P. Reynaert and M. Steyaert, *RF Power Amplifiers for Mobile Communications*, ser. Analog Circuits and Signal Processing. Amsterdam, The Netherlands: Springer, 2006.

- [6] H. Chireix, "High power outphasing modulation", Proc. IRE., vol. 23, no. 11, pp. 1370-1392, Nov. 1935.

- [7] J. H. Qureshi, M. J. Pelk, M. Marchetti, W. C. E. Neo, J. R. Gajadharsing, M. P. van der Heijden, and L. C. N. de Vreede, "A 90-W peak power GaN outphasing amplifier with optimum input signal conditioning," *IEEE Trans. Microw. Theory Techn.*, vol. 57, no. 8, pp. 1925–1935, Aug. 2009.

## **Chapter 3**

## Literature Review on Advanced Doherty Power Amplifier Design

In the past decades, the Doherty amplifier has drawn much research interest due to the ability of providing high efficiency in an extended power range with simple circuitry and mild linearity performance. In this chapter, recent works concerning the enhancement of high efficiency range and operating bandwidth of DPA are briefly reviewed.

Fig. 3.1 Simplified diagram of classical Doherty amplifier

# **3.1 Recent works on DPA design with extended high efficiency range**

It has been shown in chapter 2.4 that the classical DPA amplifier (Fig. 3.1) can offer 6dB high efficiency range of 6 dB only, which is considered to be insufficient as many modern communication standards are generating signals found with ever-increasing value of PAPR. According to (2.33), it is found that the high efficiency range is solo determined by the output power ratio ( $\alpha$ ) at saturation:

$$\alpha = \frac{P_{2sat}}{P_{1sat}} = \frac{V_{2sat}I_{2sat}}{V_{1sat}I_{1sat}} = \alpha_C \alpha_V$$

(3.1)

Subsequently, we have:

$$OBO = 20\log(1+\alpha) \tag{3.2}$$

Previous techniques on extending OBO range are mostly based on the enlargement of  $\alpha$ . A direct method is to use an auxiliary device with enlarged gate periphery, which is known as asymmetrical DPA [1]-[5]. Usually, the main and auxiliary devices employ the same semiconductor technology with equal drain bias. As a result, the auxiliary device (enlarged gate periphery) can deliver a higher level of auxiliary current and auxiliary power, which results in extended OBO.

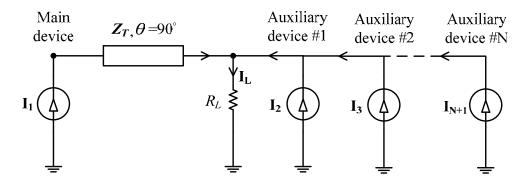

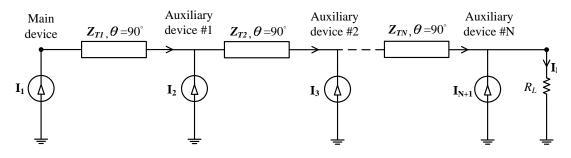

Fig. 3.2 Simplified diagram of multi-way Doherty amplifier

Alternatively, one can also use multiple auxiliary devices to increase the total amount of auxiliary current. Fig. 3.2 shows the diagram of the multi-way DPA [6], which turns on the auxiliary devices simultaneously and act equivalently to the asymmetrical DPA. Fig. 3.3 shows the drain efficiency behavior of asymmetrical DPA and multi-way DPA.

Fig. 3.3 Theoretical drain efficiency behavior of the asymetrical DPA and the multi-way DPA

Fig. 3.4 Simplified diagram of multi-stage Doherty amplifier

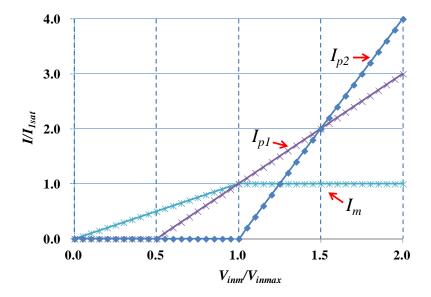

Another technique is the adoption of multi-stage DPA [7]-[8], as depicted in Fig. 3.4. In this configuration, the auxiliary devices turn on progressively to generate extra efficiency peaks. The drain efficiency behavior of a 3-stage DPA with gate periphery ratio of 1:3:4 is shown in Fig. 3.5. With the same total device periphery consumption, the average efficiency of the multi-stage DPA could outweigh the asymmetrical or multi-way DPA. However, the realization of such efficiency behavior imposes special requirement on current profiles. After reaching the second efficiency peak, the drain voltage of the auxiliary device #1 has to be kept constant for attaining maximum efficiency. Consequently, the main branch current  $I_m$  has to

Fig. 3.5 Theoretical drain efficiency behavior of the 3-stage DPA with gate periphery ratio of 1:3:4

Fig. 3.6 Current profiles of a 3-stage DPA with gate periphery ratio of 1:3:4

Fig. 3.7 Circuit diagram of the modified 3-stage Doherty amplifier

stay at a fixed level when  $V_{inm}/V_{inmax} > 1$  (Fig. 3.6). For linear input circuitry, such nonlinear behavior can only be produced by the overdriven of main device with the cost of generating large amount of distortion. To overcome this problem, a modified 3-stage DPA (Fig. 3.7) is presented in [9], which can generate three maximum efficiency peaks without saturated operation of main device. However, it still suffers from poor load modulation due to the low biases of the peaking PAs [10]. Therefore, gate bias adaptation is usually employed to achieve suitable load modulation for improved gain flatness and back-off efficiency.

# **3.2 Recent works on DPA design with extended operating bandwidth**

The increase of the number of frequency bands and signal bandwidth requires future transmitter to support wideband operation. In recent year, much effort has been devoted to design DPA with extended bandwidth.

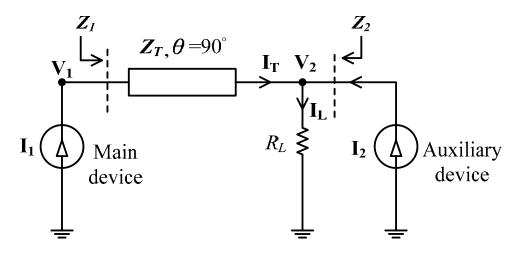

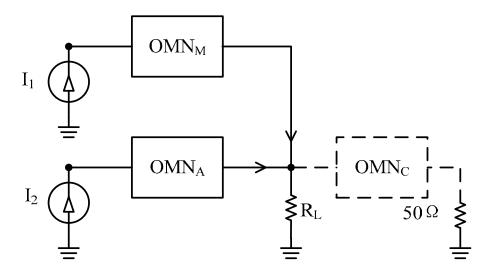

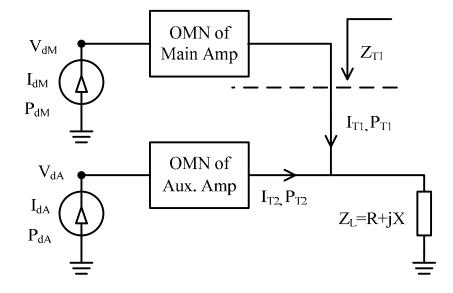

Fig. 3.8 Block diagram of DPA

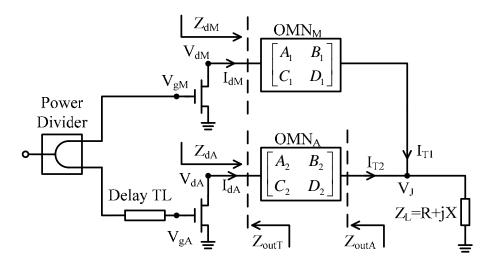

Fig. 3.8 shows the block diagram of broadband DPA. The Output Combining Matching Network (OMN<sub>C</sub>) is used to broadband transform 50ohm to the selected  $R_L$ . The Output Matching Network of Auxiliary amplifier (OMN<sub>A</sub>) is employed to compensate the device parasitic. The Output Matching Network of Main amplifier (OMN<sub>M</sub>) is made to operate as a broadband impedance inverter with  $\theta$ =90°@ $f_0$  [11]-[13]. The broadband networks can be synthesized with the classical filter theory [12] or Simplified Real Frequency Technique (SRFT) [13]. Based on this approach, DPAs with bandwidth up to 40% have been reported. However, serious degradation

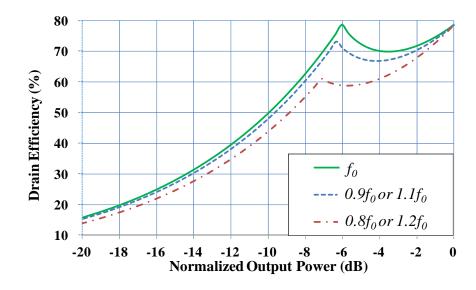

Fig. 3.9 Theoretical broadband drain efficiency behavior of DPA under classical configuration

on the efficiency (first peak) has been observed, which can be explained by the frequency variation of drain load (low power region):

$$Z_{1cri} = Z_T \frac{R_L + j \tan(\theta) Z_T}{Z_T + j \tan(\theta) R_L} = R_{opt} \frac{1 + j \cdot 2 \tan(\theta)}{2 + j \tan(\theta)}$$

(3.3)

As frequency is offset from the center value,  $Z_{Icri}$  would deviate from the optimum load  $(2R_{opt})$ , which leads to efficiency degradation (low power region). Based on the classical approach, we have:

$$Z_T = 2R_L = R_{opt} \tag{3.4}$$

$$I_{2} = \begin{cases} 0 & I_{1} < 0.5I_{1sat} \\ 2I_{1} - I_{1sat} & I_{1} \ge 0.5I_{1sat} \end{cases}$$

(3.5)

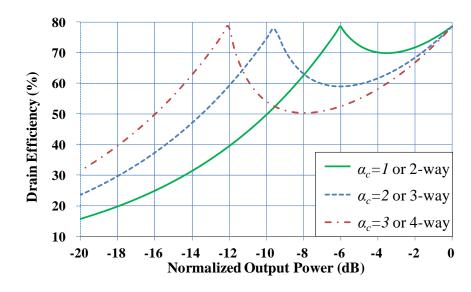

With the assumption of in-phase combining of  $I_T$  and  $I_2$  (Fig. 3.1), the theoretical broadband drain efficiency of classical configuration can be calculated (Fig. 3.9). It can be observed that, the efficiency curves deviates significantly from ideal case (solid line) when fractional bandwidth is extended beyond 20%.

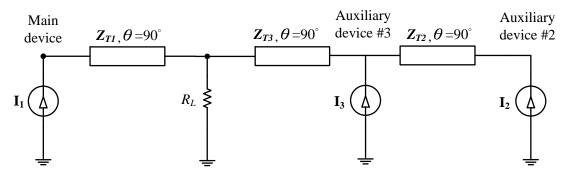

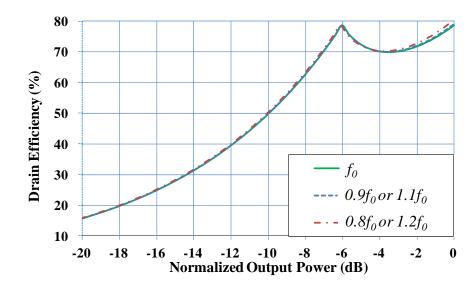

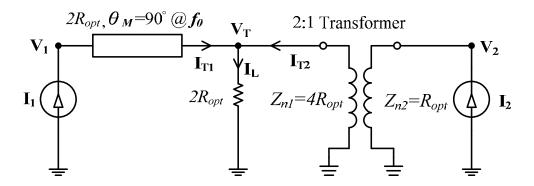

To overcome this problem, a modified configuration is introduced in [14]:

$$Z_T = R_L = 2R_{opt} \tag{3.6}$$

As a result, the drain load (main) is maintained at  $2R_{opt}$  (optimum load at 6dB back-off level) over an extended bandwidth (infinite in theory), and the efficiency peak of low power region can be maintained. Under such an arrangement, the current ratio and voltage ratio can be evaluated as:

$$\alpha_V = \frac{V_{2sat}}{V_{1sat}} = 2 \tag{3.7}$$

$$\alpha_{c} = \frac{I_{2sat}}{I_{1sat}} = 0.5 \tag{3.8}$$

In consequence, the resulted auxiliary current profile can be written as:

$$I_{2} = \begin{cases} 0 & I_{1} < 0.5I_{1sat} \\ I_{1} - I_{1sat}/2 & I_{1} \ge 0.5I_{1sat} \end{cases}$$

(3.9)

According to [14], it is further assumed that:

$$phase(I_2) = phase(I_1) - 90^{\circ}$$

(3.10)

Subsequently, from (3.9) and (3.10), the theoretical drain efficiency of the modified configuration can be calculated (Fig. 3.10), which shows substantial improvement in efficiency.

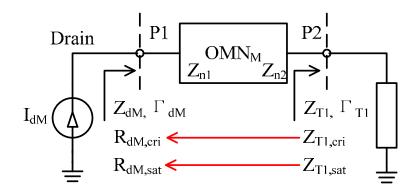

Furthermore, referring to Fig. 3.1, under the modified configuration, by the multiplication of ABCD matrices, the relationship between the terminal voltages and currents can be obtained as:

$$\begin{bmatrix} \mathbf{V}_{1} \\ \mathbf{I}_{1} \end{bmatrix} = \begin{bmatrix} e^{j\theta} & j2R_{opt}\sin\theta \\ e^{j\theta}/2R_{opt}&\cos\theta \end{bmatrix} \begin{bmatrix} \mathbf{V}_{2} \\ -\mathbf{I}_{2} \end{bmatrix}$$

(3.11)

$$\mathbf{V}_1 = 2R_{opt}(\mathbf{I}_1 + \mathbf{I}_2 e^{-j\theta}) \tag{3.12}$$

$$\mathbf{V}_2 = 2R_{opt}(\mathbf{I}_1 + \mathbf{I}_2 \cos\theta)e^{-j\theta}$$

(3.13)

Fig. 3.10 Theoretical broadband drain efficiency behavior of DPA under classical configuration

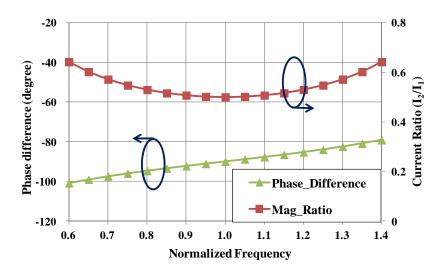

It is also found that, if wideband conditions of (3.9) and (3.10) are imposed, the magnitude of  $V_1$  and  $V_2$  can exceed the bias voltage as frequency offsets from the center, which limits the available bandwidth under Class B operation. Therefore, in [15] a frequency dependent current relationship is enforced:

$$\mathbf{I}_{2} = \mathbf{I}_{1} \cdot k(f, v_{in}) e^{j\theta_{d}(f, v_{in})}$$

(3.14)

The ratio k and phase difference  $\theta_d$  are function of both frequency and drive level. Clearly, at maximum output power level, the drain voltage  $V_{Isat}$  should be maintained at  $V_{dc}$  to generate the efficiency peak but without saturating the device:

$$\left|\mathbf{V}_{1sat}\right| = \left|2R_{opt}I_{1sat}(1+ke^{j(\theta_d-\theta)})\right| = V_{dc}$$

(3.15)

$$|\mathbf{V}_{2sat}| = |2R_{opt}I_{1sat}[1+k\cos(\theta)e^{j\theta_d}]| = 2V_{dc}$$

(3.16)

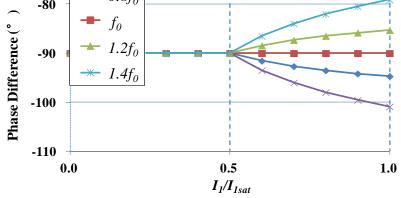

From (3.15) and (3.16), k and  $\theta_d$  can be solved (Fig. 3.11) for each  $\theta$  (= $f/f_0 \times 90^\circ$ ). With linear input-output assumption, the analysis can be further extended to the entire Doherty region. Fig. 3.12 shows the optimum value of k and  $\theta_d$  as a function of  $I_1$  (= $v_{in}$ ). Complex input circuitry involving digital control system has been used to

Fig. 3.11 Optimum saturation k and  $\theta_d$  versus operating frequency

(b)

Fig. 3.12 Optimum current profiles: (a) magnitude ratio k; (b) phase difference  $\theta_d$ .

produce the required current profiles, and demonstrated good Doherty performance over fractional bandwidth of 45%.

## References

- [1] J. Moon, J. Kim, J. Kim, I. Kim, and B.Kim, "Efficiency enhancement of Doherty amplifier through mitigation of the knee voltage effect," IEEE Trans. Microw. Theory Techn., vol. 59, no. 1, pp. 143–152, Jan. 2011.

- [2] J. Kim, J. Cha, I. Kim, and B. Kim, "Optimum operation of asymmetricalcells-based linear Doherty power amplifiers-uneven power drive and power matching," IEEE Trans. Microw. Theory Techn., vol. 53, no. 5, pp. 1802–1809, May 2005.

- [3] Y. Lee, M. Lee, and Y. Jeong, "Unequal-cells-based GaN HEMT Doherty amplifier with an extended efficiency range," IEEE Microw.Wireless Compon. Lett., vol. 18, no. 8, pp. 536–538, Aug. 2008.

- [4] K. Jangheon et al., "Power efficiency and linearity enhancement using optimized asymmetrical Doherty power amplifiers," IEEE Trans. Microw. Theory Techn., vol. 59, no. 2, pp. 425–434, Feb. 2011.

- [5] D. Y. Wu and S. Boumaiza, "A Mixed-technology asymetrically biased extended and reconfigurable Doherty amplifier with improved power utilization factor," IEEE Trans. Microw. Theory Techn., vol. 61, no. 5, pp. 1946–1956, May 2013.

- [6] M. Iwamoto, A. Williams, P. Chen, A. G. Metzger, L. E. Larson, and P. M. Asbeck, "An extended Doherty amplifier with high efficiency over a wide power range," IEEE Trans. Microw. Theory Techn., vol. 49, no. 12, pp. 2472–2479, Dec. 2001.

- [7] N. Srirattana, A. Raghavan, D. Heo, P. E. Allen, and J. Laskar, "Analysis and design of a high-efficiency multistage Doherty power amplifier for wireless communications," IEEE Trans. Microw. Theory Techn., vol. 53, no. 3, pp. 852–860, Mar. 2005.

- [8] W. C. E. Neo, J. Qureshi, M. J. Pelk, J. R. Gajadharsing, and L. C. N. de Vreede, "A mixed-signal approach towards linear and efficient N-way Doherty amplifiers," IEEE Trans. Microw. Theory Techn., vol. 55, no. 5, pp. 866–879, May 2007.

- [9] J. Gajadharsing, W. C. E. Neo, M. Pelk, L. C. N. de Vreede, and J. Zhao, "3-way Doherty amplifier with minimum output network", U.S. Patent 8 022 760, Sep. 2011.

- [10]I. Kim, J. Moon, S. Jee, and B. Kim, "Optimized design of a highly efficient three-stage Doherty PA using gate adaptation," IEEE Trans. Microw. Theory Techn., vol. 58, no. 10, pp. 2562–2574, Oct. 2010.

- [11]J. H. Qureshi, N. Li, W. C. E. Neo, F. Rijs, I. Blednov, and L. C. N. de Vreede, "A wideband 20 W LMOS Doherty power amplifier," in IEEE MTT-S Int. Microw. Symp. Dig., Anaheim, CA, May 2010, pp. 1504–1507.

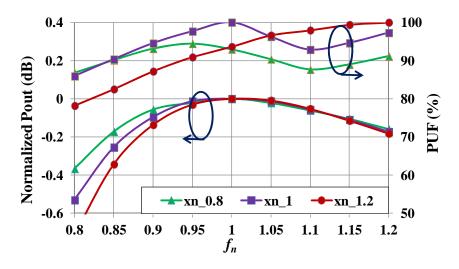

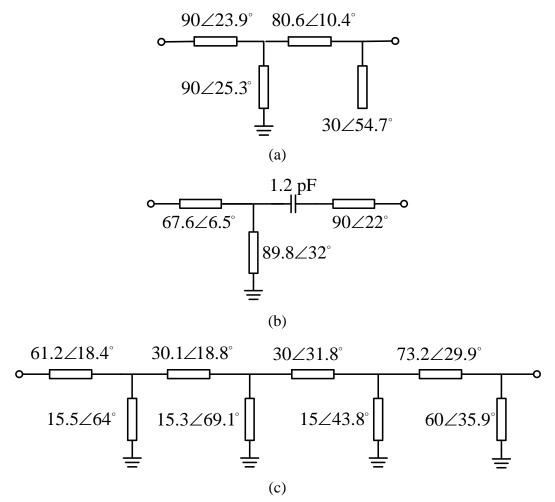

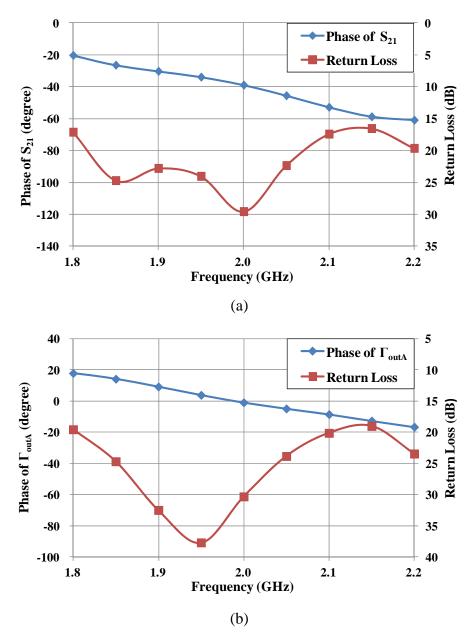

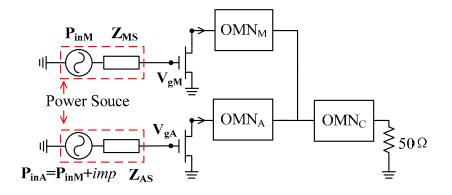

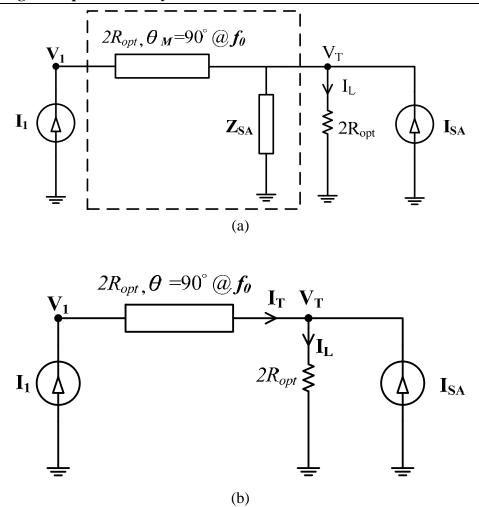

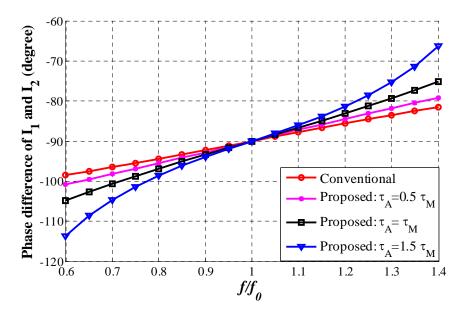

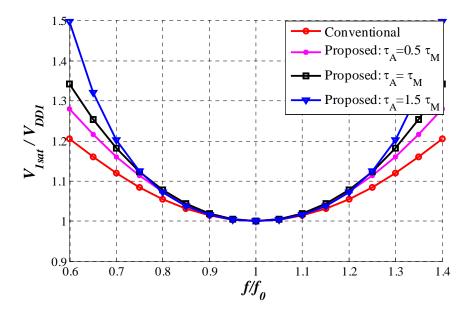

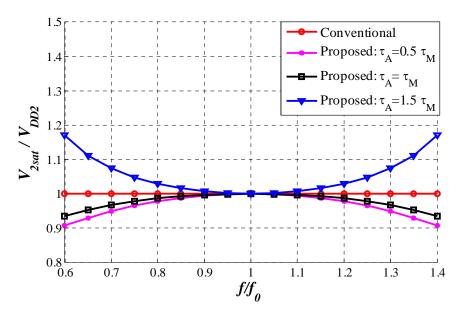

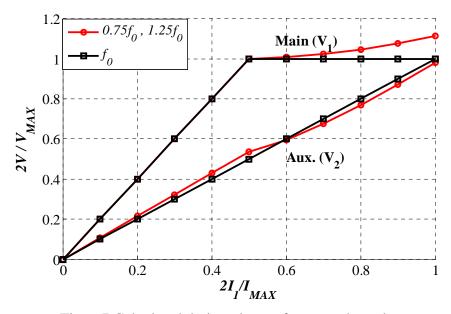

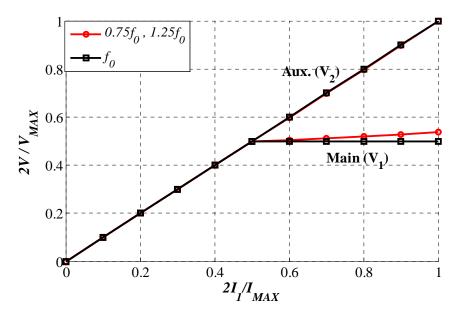

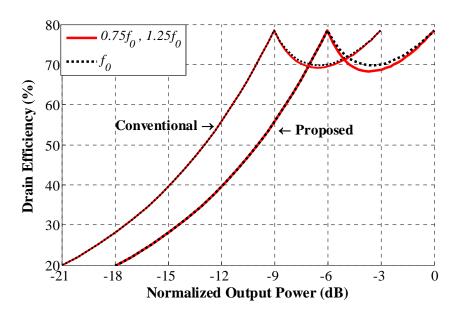

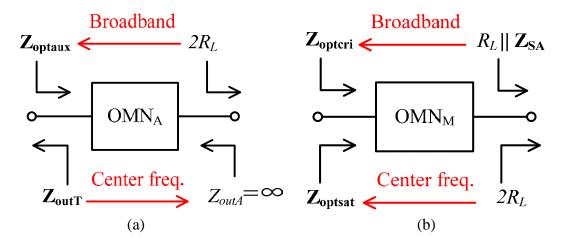

- [12]K. Bathich, A.Markos, and G. Boeck, "Frequency response analysis and bandwidth extension of the Doherty amplifier", IEEE Trans. Microw. Theory Tech., vol. 59, no. 4, pp. 934-944, Apr. 2011