# ACTA

# UNIVERSITATIS OULUENSIS

Jussi-Pekka Jansson

A STABILIZED MULTI-CHANNEL CMOS TIME-TO-DIGITAL CONVERTER BASED ON A LOW FREQUENCY REFERENCE

UNIVERSITY OF OULU GRADUATE SCHOOL; UNIVERSITY OF OULU, FACULTY OF TECHNOLOGY, DEPARTMENT OF ELECTRICAL ENGINEERING; INFOTECH OULU

#### ACTA UNIVERSITATIS OULUENSIS C Technica 430

#### **JUSSI-PEKKA JANSSON**

# A STABILIZED MULTI-CHANNEL CMOS TIME-TO-DIGITAL CONVERTER BASED ON A LOW FREQUENCY REFERENCE

Academic dissertation to be presented with the assent of the Doctoral Training Committee of Technology and Natural Sciences of the University of Oulu for public defence in OP-Pohjola-sali (Auditorium L6), Linnanmaa, on 9 November 2012, at 12 noon

UNIVERSITY OF OULU, OULU 2012

Copyright © 2012 Acta Univ. Oul. C 430, 2012

Supervised by Professor Juha Kostamovaara

Reviewed by Professor Olli Vainio Associate Professor Pietro Andreani

ISBN 978-951-42-9931-5 (Paperback) ISBN 978-951-42-9932-2 (PDF)

ISSN 0355-3213 (Printed) ISSN 1796-2226 (Online)

Cover Design Raimo Ahonen

JUVENES PRINT TAMPERE 2012

# Jansson, Jussi-Pekka, A stabilized multi-channel CMOS time-to-digital converter based on a low frequency reference.

University of Oulu Graduate School; University of Oulu, Faculty of Technology, Department of Electrical Engineering; Infotech Oulu, P.O. Box 4500, FI-90014 University of Oulu, Finland *Acta Univ. Oul. C 430, 2012*Oulu, Finland

#### Abstract

The aim of this work was to improve the performance and usability of a digital time-to-digital converter (TDC) in CMOS technology. The characteristics of the TDC were improved especially for the needs of pulsed laser time-of-flight (TOF) distance measurement, where picosecond-level precision with a long  $\mu$ s-level measurement range is needed in order to approach mm-level measurement accuracy. Stability in the face of process, voltage and temperature variations, multiple measurement channels, alternative measurement modes, a high integration level, standard interfaces and simple usage were the main features for development.

The measurement architecture is based on counter and timing signal interpolation on two levels. The counter counts the full reference clock cycles between the timing signals, while a new recycling delay line developed in this thesis interpolates within the reference clock cycle. This technique utilizes a short delay line several times per reference clock cycle, which minimizes the interpolation nonlinearity. The same structure also makes the use of a low, MHz-level reference frequency possible, and thus only a crystal is needed as an external oscillator component. The parallel load capacitor-scaled delay line structure acts as the second, sub-gate-delay interpolation level. The INL does not accumulate in elements connected in parallel, and the load capacitance differences enable high, ps-level resolution to be achieved.

Four TDC circuits in  $0.35 \, \mu m$  CMOS technology were designed and tested in the course of this work, of which the latest, a 7-channel TDC, is able to measure the time intervals between the start pulse and three separate stop pulses in one measurement and to resolve the pulse widths or rise times at the same time. In laser TOF distance measurement this functionality can be used when several echoes arrive at the receiver, and also to compensate for the detection threshold problem known as timing walk error. The TDC achieves 8.9 ps interpolation resolution within the cycle time of a 20 MHz reference clock using only 8 delay elements on the first interpolation level and 14 delay elements on the second. A measurement precision better than 9 ps was achieved without using result post-processing or look-up tables. This work shows that versatile, high performance TDCs can be created in standard CMOS technology.

Keywords: delay line interpolation, laser radar, reference recycling, time interval measurement, time-to-digital converter (TDC), walk-error compensation

#### Jansson, Jussi-Pekka, Stabiloitu, monikanavainen, matalataajuiseen referenssikelloon perustuva CMOS aika-digitaalimuunnin.

Oulun yliopiston tutkijakoulu; Oulun yliopisto, Teknillinen tiedekunta, Sähkötekniikan osasto; Infotech Oulu, PL 4500, 90014 Oulun yliopisto

Acta Univ. Oul. C 430, 2012

Oulu

#### Tiivistelmä

Väitöskirjatyön tavoitteena oli parantaa CMOS-aika-digitaalimuuntimien suorituskykyä ja käytettävyyttä. Muuntimen ominaisuuksia kehitettiin erityisesti laseretäisyysmittauksen tarpeita ajatellen, missä millimetritason mittaustarkkuus laajalla mittausaluella edellyttää aika-digitaalimuuntimelta pikosekuntitason tarkkuutta mikrosekuntien mittausalueella. Stabiilius prosessiparametri-, jännite- ja lämpötilavaihteluita vastaan, useat mittauskanavat, useat mittausmoodit, korkea integraatioaste, standardoidut liitäntäväylät ja helppo käytettävyys olivat erityisesti kehityksen kohteina.

Suunniteltu mittausarkkitehtuuri koostuu laskurista ja kaksitasoisesta ajoitussignaali-interpolaattorista. Laskuri laskee kokonaiset referenssikellojaksot ajoitussignaalien välillä ja työssä kehitetty referenssiä kierrättävä viivelinjarakenne rekistereineen interpoloi ajoitussignaalien paikat referenssikellojaksojen sisältä. Referenssinkierrätystekniikka hyödyntää lyhyttä viivelinjaa useampaan kertaan kellojakson aikana, mikä minimoi epälineaarisuuden interpoloinnissa. Sama rakenne mahdollistaa myös MHz-tason referenssitaajuuden, jolloin matalataajuista kidettä voidaan käyttää referenssilähteenä. Toinen interpolointitaso koostuu rinnakkaisista kapasitanssiskaalatuista viive-elementeistä, mitkä mahdollistavat alle porttiviiveen mittausresoluution. Rinnakkaisessa rakenteessa elementtien epälineaarisuudet eivät summaudu, mikä mahdollistaa pikosekuntitason mittaustarkkuuden.

Väitöskirjatyössä suunniteltiin ja toteutettiin neljä aikavälinmittauspiiriä käyttäen 0,35 µm CMOS-teknologiaa, joista viimeisin, 7-kanavainen muunnin kykenee mittaamaan aikavälin useampaan pulssiin yhdellä kertaa sekä voi selvittää samalla pulssien leveydet tai nousuajat. Laseretäisyysmittauksessa monikanavaisuutta voidaan käyttää kun useita kaikuja lähetetystä pulssista saapuu vastaanottimeen sekä kompensoimaan mittauksessa esiintyviä muita virhelähteitä. Käytettäessä 20 MHz:n kidettä referenssilähteenä muunnin saavuttaa alle 9 ps:n interpolointiresoluution ja tarkkuuden ilman epälineaarisuudenkorjaustaulukoita. Työ osoittaa, että edullisella CMOS-teknologialla voidaan toteuttaa monipuolinen ja erittäin suorituskykyinen aika-digitaalimuunnin.

Asiasanat: Aika-digitaalimuunnin, aikavälinmittaus, laseretäisyysmittaus, referenssinkierrätys, viivelinjainterpolointi

# **Acknowledgements**

This thesis is based on research work carried out at the Electronics Laboratory of the Department of Electrical Engineering and Infotech Oulu, University of Oulu, during the years 2004–2012.

First, I would like to thank my supervisor, Professor Juha Kostamovaara, for his excellent guidance, support and patience during these years. His tireless sharing of knowledge and experience has been exceptional. I would like to thank Dr. Antti Mäntyniemi for introduction and guidance into the world of digital time interval measurement. I would also like to thank all my co-workers for the helpful and pleasant working environment.

I wish to thank Professor Olli Vainio and Associate Professor Pietro Andreani for reviewing my thesis, and Mr. Malcolm Hicks for revising the English of the manuscript and most of the publications.

This research was supported financially by Infotech Oulu Graduate School, Finnish Funding Agency for Technology and Innovation (TEKES) and Academy of Finland. Financial support has also been received from the following foundations: Tekniikan Edistämissäätiö (TES), Tauno Tönningin Säätiö, Nokia Oyj:n Säätiö, Seppo Säynäjäkankaan Tiedesäätiö, Kaute-Säätiö, Walter Ahlströmin Säätiö, Elektroniikkainsinöörien Seura (EIS), Ulla Tuomisen Säätiö and Riitta ja Jorma J. Takasen Säätiö. All of these partners and foundations are gratefully acknowledged.

I would like to thank my parents Mikael and Vieno, my brothers with their families and my friends for patience and support during these years. Finally, I would like to express my gratitude to my lovely wife Miia and children Iida and Daniel. You are the most important in my life.

# List of terms, symbols and abbreviations

The terms describing the performance of the measurement equipment are defined according to the IEEE Standard Dictionary of Electrical and Electronics Terms (IEEE 1996):

Accuracy is the degree of correctness with which a measured value agrees with the true value

*Differential nonlinearity* is the difference between a specified code bin width and the average code bin width

*Integral nonlinearity* is the maximum nonlinearity (deviation) over the specified operating range of a system

*Jitter* refers to the short-term deviations of the significant instants of a signal from their ideal positions in time

*Precision* is the quality of coherence or repeatability of measurement data, customarily expressed in terms of the standard deviation of the extended set of measurement results from a well-defined (adequately specified) measurement process in a state of statistical control

Random error has unknown magnitudes and direction and varies with each measurement

Resolution is the least value of the measured quantity that can be distinguished

Systematic error remains constant in magnitude and direction throughout the calibration process

ADAS advanced driver assistance systems

ADC analogue-to-digital converter

ALU arithmetic logic unit

AWG arbitrary waveform generator

BiCMOS bipolar-CMOS, a semiconductor technology containing both bipolar

and CMOS transistors

BIST built-in self-test

CLK clock

CMOS complementary MOS, a semiconductor technology containing both

NMOS and PMOS transistors

CP charge pump

CSN chip select negative

CTR counter

DAC digital-to-analogue converter

DLL delay-locked loop

DNL differential nonlinearity

EN enable

FPGA field-programmable gate array

GaAs gallium arsenide

IC integrated circuit

IEEE Institute of Electrical and Electronics Engineers

INL integral nonlinearity

INT1 first interpolation level result INT2 second interpolation level result

LSB least significant bit LUT look-up table

MDLL multiplying delay-locked loop

MISO master in, slave out MOSI master out, slave in

NRE nonrecurring engineering

PD phase detector

PET positron emission tomography PVT process, voltage, temperature QFN quad flat no-leads package

REFCLK reference clock rms root mean square

SPI serial peripheral interface SYNC synchronization block TAC time-to-amplitude converter

TCXO temperature compensated crystal oscillator

TDC time-to-digital converter

TEKES Finnish Funding Agency for Technology and Innovation

TOF time-of-flight

XTAL crystal

c velocity of light

C capacitance

I current

M recycling factor Q<sub>e</sub> quantization error

10

RΦn register value of time sample n

ST<sub>int</sub> result of start interpolator

SP<sub>int</sub> result of stop interpolator

T actual input time

$T_{INT}$  interpolation time interval  $T_m$  measurement result of TDC

T<sub>SPn</sub> time interval between start and stop pulse n

$\begin{array}{ll} T_w & \text{pulse width} \\ T_r & \text{rise time} \end{array}$

V<sub>ctrl</sub> control voltage

σ standard deviation

σ<sub>clk</sub> rms jitter of reference clock

σ<sub>inl</sub> standard deviation of integral nonlinearity

$\sigma_{start}$  rms jitter of start signal  $\sigma_{stop}$  rms jitter of stop signal  $\sigma_{tdc}$  rms TDC internal jitter  $\sigma_{q}$  rms quantization error

$\sigma_{rms}$  rms standard deviation of the single-shot precision of a TDC

μ average value

resolution of the first interpolation level resolution of the second interpolation level

τclk period of the internal clock

τe delay element basic delay

τint interpolation resolution

τref period of the reference clock

τ<sub>tot</sub> delay element total propagation delay

Φn interpolation time sample n

# List of original publications

- I Jansson J-P, Mäntyniemi A & Kostamovaara J (2005) A Delay Line Based CMOS Time Digitizer IC with 13 ps Single-shot Precision. Proceedings of IEEE International Symposium on Circuits and Systems (ISCAS'2005). Kobe, Japan, 23–26 May 2005, 5: 4269–4272.

- II Jansson J-P, M\u00e4ntyniemi A & Kostamovaara J (2006) A CMOS Time-to-Digital Converter with better than 10 ps Single-Shot Precision. IEEE Journal of Solid-State Circuits, 41(6): 1286–1296.

- III Jansson J-P, M\u00e4ntyniemi A & Kostamovaara J (2009) Synchronization in a Multi-level CMOS Time-to-Digital Converter. IEEE Transactions on Circuits and Systems I: Regular Papers. 56(8): 1622–1634.

- IV Jansson J-P, M\u00e4ntyniemi A & Kostamovaara J (2009) Multiplying Delay Locked Loop (MDLL) in Time-to-Digital Conversion. Proceedings of International Instrumentation and Measurement Technology Conference (I2MTC'2009). Singapore, 5–7 May 2009: 1226–1231.

- V Jansson J-P, Koskinen V, Mäntyniemi A & Kostamovaara J (2012) A Multichannel High-Precision CMOS Time-to-Digital Converter for Laser-Scanner-Based Perception Systems. IEEE Transactions on Instrumentation and Measurement. 61(9): 2581–2590.

The author wrote the above papers and was responsible for the practical work lying behind them. The work was supervised by Prof. Juha Kostamovaara, whose ideas, comments and hints helped in the completion of the whole work.

# **Contents**

| A  | bstra  | ct                                                            |    |

|----|--------|---------------------------------------------------------------|----|

| Ti | iviste | elmä                                                          |    |

| A  | cknov  | wledgements                                                   | 7  |

| Li | st of  | terms, symbols and abbreviations                              | 9  |

| Li | st of  | original publications                                         | 13 |

| C  | onten  | its                                                           | 15 |

| 1  | Intr   | oduction                                                      | 17 |

|    | 1.1    | Background                                                    | 17 |

|    | 1.2    | Contributions and structure of the thesis                     | 19 |

| 2  | Tim    | e interval measurement uncertainty                            | 23 |

|    | 2.1    | Quantization error                                            | 24 |

|    | 2.2    | Nonlinearity                                                  | 25 |

|    | 2.3    | Stability                                                     | 26 |

|    | 2.4    | Jitter sources.                                               | 27 |

| 3  |        | e-to-digital conversion methods                               | 29 |

|    | 3.1    | The counter method                                            | 31 |

|    |        | Time-to-amplitude converter (TAC)                             |    |

|    | 3.3    | Delay line-based measurement methods                          | 33 |

|    |        | 3.3.1 Delay line with successive elements                     |    |

|    |        | 3.3.2 The Vernier-based measurement method                    | 36 |

|    |        | 3.3.3 Pulse-shrinking delay line                              | 37 |

|    | 3.4    | Technological issues.                                         | 38 |

|    | 3.5    | Conclusions                                                   | 39 |

| 4  | Ove    | rview of the original publications                            | 41 |

|    | 4.1    | Paper I (2005), A Delay Line Based CMOS Time Digitizer IC     |    |

|    |        | with 13 ps Single-shot Precision                              | 41 |

|    | 4.2    | Paper II (2006), A CMOS Time-to-Digital Converter with better |    |

|    |        | than 10 ps Single-Shot Precision.                             | 41 |

|    | 4.3    | Paper III (2009), Synchronization in a Multi-level CMOS Time- |    |

|    |        | to-Digital Converter                                          | 42 |

|    | 4.4    | Paper IV (2009), Multiplying Delay Locked Loop (MDLL) in      |    |

|    |        | Time-to-Digital Conversion                                    | 43 |

|    | 4.5    | Paper V (2012), A Multi-Channel High Precision CMOS Time-     |    |

|    |        | to-Digital Converter for Laser Scanner-Based Perception       |    |

|    |        | Systems                                                       | 43 |

| 5  | Stru                     | icture                                               | s for a high performance time-to-digital converter    | 45 |  |  |

|----|--------------------------|------------------------------------------------------|-------------------------------------------------------|----|--|--|

|    | 5.1                      | 5.1 Two-level (coarse-fine) measurement architecture |                                                       |    |  |  |

|    | 5.2 Coarse interpolation |                                                      |                                                       | 46 |  |  |

|    |                          | 5.2.1                                                | Basic successive delay line structure                 | 46 |  |  |

|    |                          | 5.2.2                                                | Reference recycling delay line                        | 48 |  |  |

|    | 5.3                      | Fine i                                               | nterpolation                                          | 50 |  |  |

|    |                          | 5.3.1                                                | Load capacitor-scaled delay lines                     | 50 |  |  |

|    |                          | 5.3.2                                                | Stabilization of load capacitor-scaled delay elements | 53 |  |  |

|    | 5.4                      | Synch                                                | nronization structures                                | 53 |  |  |

|    |                          | 5.4.1                                                | Counter synchronization                               | 55 |  |  |

|    |                          | 5.4.2                                                | Synchronization of the second interpolation level     | 57 |  |  |

| 6  | A m                      | ulti-cl                                              | nannel TDC for TOF distance measurements              | 61 |  |  |

|    | 6.1                      | TDC                                                  | requirements in laser TOF distance measurement        | 61 |  |  |

|    | 6.2 Operation            |                                                      |                                                       | 63 |  |  |

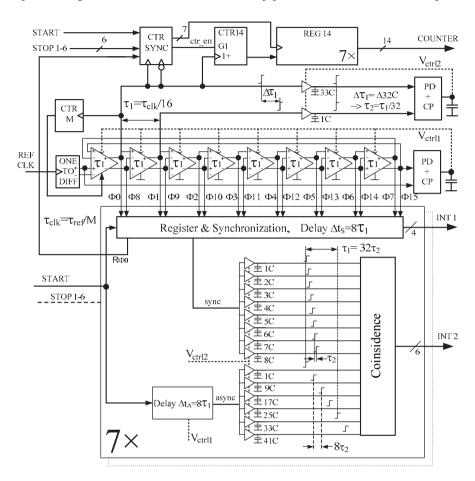

|    | 6.3                      | 3.3 Architecture                                     |                                                       |    |  |  |

|    | 6.4                      | 4 Measurement core                                   |                                                       |    |  |  |

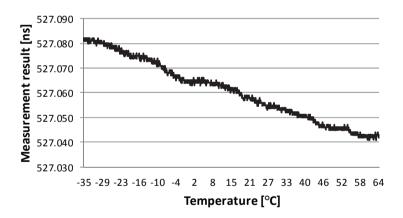

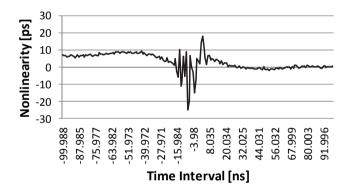

|    | 6.5                      | 5 Measurement results                                |                                                       |    |  |  |

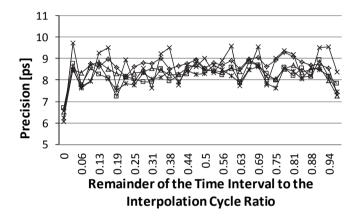

|    |                          | 6.5.1                                                | Interpolation nonlinearity                            | 68 |  |  |

|    |                          | 6.5.2                                                | Temperature drift                                     | 70 |  |  |

|    |                          |                                                      | Measurement linearity                                 |    |  |  |

|    |                          | 6.5.4                                                | Precision                                             | 71 |  |  |

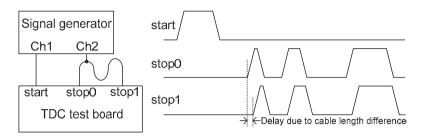

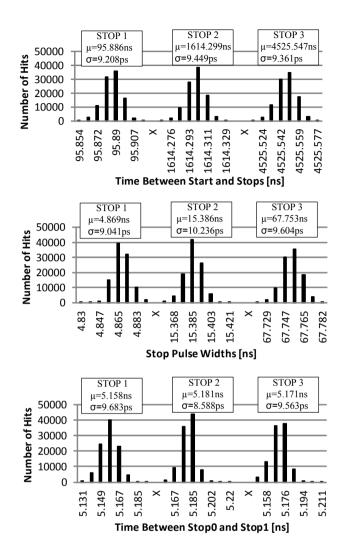

|    |                          | 6.5.5                                                | Multi-channel measurement                             | 72 |  |  |

| 7  | Disc                     | cussior                                              | 1                                                     | 77 |  |  |

|    | 7.1                      | Comp                                                 | parison with other TDCs                               | 79 |  |  |

| 8  | Sun                      | ummary                                               |                                                       |    |  |  |

| Re | fere                     | nces                                                 |                                                       | 87 |  |  |

| Or | igin                     | al pub                                               | olications                                            | 93 |  |  |

### 1 Introduction

#### 1.1 Background

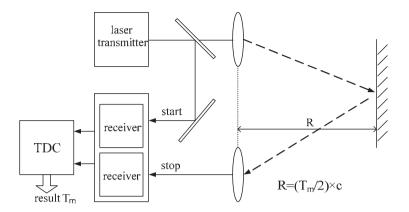

A time-to-digital converter (TDC) measures the time interval between two or more timing signals and presents the result in a digital form. The main inputs, the electrical timing signals, define the beginning and end of the measurement and are thus often called the start and stop signals, respectively. The measurement result, a digital word, is the main output of the TDC.

High resolution time-to-digital conversion is used in many applications. Measurement devices such as oscilloscopes and logic analysers commonly utilize TDCs (Park & Park 1999), and experiments in high energy physics, such as those concerned with particle lifetimes, flight times and identification, are largely based on high precision time interval measurements (Porat 1973, Myllylä 1976, Brockhaus & Glasmachers 1992). The TDC is a basic block in laser time-of-flight (TOF) rangefinders (Goldstein & Dalrymble 1967, Kostamovaara 1986, Määttä 1995) and can be used to characterize the timing and performance parameters of high speed circuits, i.e. jitter, skew, clock-to-output, setup times, hold times, ageing and clock control (Wilstrup 1998, Rivoir 2006, Abas et al. 2007, Chen et al. 2011, Bowman et al. 2011). TDCs are used in telecommunications for clock recovery (Park & Kim 1999), phase and frequency demodulation (Chu 1988, Rahkonen & Kostamovaara 1994) and all-digital frequency synthesis (Staszewski et al. 2006, Tonietto et al. 2006), for example. Medical imaging techniques such as time-of-flight positron emission tomography (TOF-PET) also make use of TDCs (Moses 2003, Conti et al. 2005). Analogue-to-digital conversion (ADC) can be performed over the time domain with analogue-to-time and time-to-digital converters (Huang & Sechen 2009, Daniels et al. 2010, Townsend et al. 2010). Other new applications to have emerged recently are single photon counting (Niclass et al. 2008) and fluorescence measurements (Schwartz et al. 2008).

Interest in TDCs is increasing, for a number of reasons. Picosecond-level measurement performance with standard, cheap technologies has made new applications possible and profitable. New small line width circuit technologies with a low operating voltage weaken the characteristics of traditional analogue signal processing but improve the performance of the signal processing in the time domain. The analogue circuit blocks used in frequency synthesis, for example, can in many cases be replaced with digital blocks including a TDC.

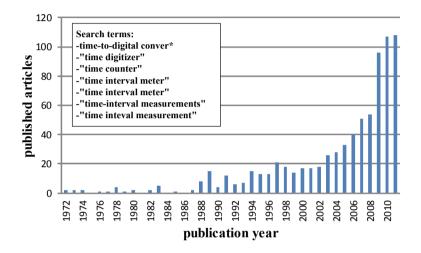

The numbers of TDC-related articles contained in the IEEE (Institute of Electrical and Electronics Engineers) *Xplore* digital library in given years are shown in Fig. 1, the identification criterion being the occurrence of one of the search terms listed in the insert in either the title, abstract or index. It should be mentioned in this connection that one of the articles included in this thesis (Paper II) is the second most referenced TDC architecture publication of all time, having a total of 67 citations in the IEEE library and totally 111 citations according to the Google Scholar (August 2012).

Fig. 1. TDC-related articles in the IEEE Xplore digital library.

Electronic time interval measurement has been studied at the Electronics Laboratory of the University of Oulu since the late 1970s. Many measurement architectures have been developed and a large number of master's, licentiate's and doctoral theses have been published concerning time interval digitization. Nuclear science and laser distance measurement have been the main applications for the TDCs designed in the laboratory (Myllylä 1976, Kostamovaara 1986, Rahkonen 1993, Määttä 1995, Räisänen-Ruotsalainen 1998, Mäntyniemi 2004, Nissinen 2011).

The aim of this work is to continue the laboratory's TDC development work by improving the performance of time-to-digital conversion. Measurement precision is perhaps the main performance parameter, but calibration-free operation, operation with several timing signals, suitability for serial production, user-friendliness, versatility, integration of auxiliary functions, size and power consumption have also been taken into account in this work.

#### 1.2 Contributions and structure of the thesis

The first mission in this work was to reach a better than 10 ps time interval measurement precision within a long measurement range. The goal was achieved with a TDC that included a counter and a two-level interpolation architecture in 0.35  $\mu m$  CMOS technology. The counter is responsible for the measurement range, the first interpolation level creates even-sized time samples with a new developed delay line structure which makes low integral nonlinearity (INL) possible, and the second interpolation level continues the interpolation with a parallel load capacitor scaled delay line structure which is able to create linear time samples with better than 10 ps resolution.

The second contribution is the proposal for a means of utilizing a low-frequency reference source. TDCs usually require higher reference frequencies, from several tens of MHz up to the GHz level. With a high reference frequency the interpolation region becomes smaller, in which case linear high resolution interpolation is easier and the TDC can be small in size. The power consumption of a high frequency oscillator can be high, however, and its costs can be much greater than those of the actual TDC. It is shown here that the reference frequency does not need to be high in order to achieve high precision and stable operation in varying environmental circumstances. The reference recycling technique developed here employs a short delay line several times per reference clock cycle and the resulting TDCs are able to use reference sources of only few megahertz. Finally, the oscillator was also integrated into the circuit, so that only a crystal is needed as an external component, which further reduces the costs and size of the device.

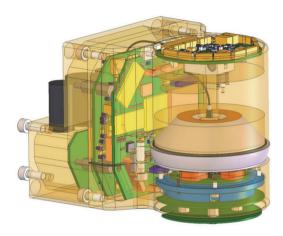

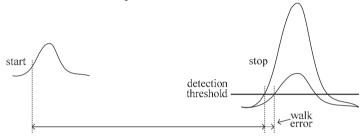

The third contribution is the designing of a TDC especially for the needs of pulsed laser TOF radar, within the Minifaros Project, part of the 7<sup>th</sup> Framework Programme funded by the European Commission (www.minifaros.eu), The aim of this project was to develop a low cost, lightweight and miniature laser scanner sensor (prototype shown in Fig. 2) for vehicular environmental perception (Fürstenberg & Ahlers 2011). The resulting TDC circuit, presented in detail in Chapter VI, measures the time interval between transmitted and received laser pulses, and uses this information to determine the distance from the target. The application demands several parallel measurement channels in order to locate a

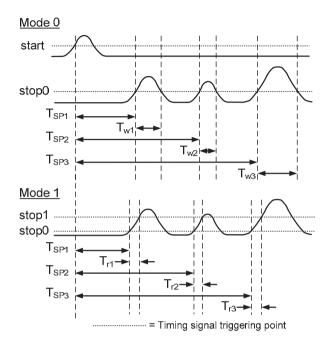

number of adjacent echo-pulses, and also for walk-error compensation, as will be explained later. The 7-channel TDC designed here can provide the time intervals between the start and three successive stop pulses and the widths or rise times of the stop pulses. There are also several new structures that improve the usability of the circuit. The circuit can be tested at the wafer level without precise external time delays by means of a built-in self-test (BIST), a serial peripheral interface (SPI) provides a standard data link for the user, and the final measurement results are calculated within the TDC, which reduces the data flow out of the circuit and minimizes external data processing. The TDC is also able to handle situations in which the stop signals arrive before the start.

Fig. 2. The prototype laser scanner produced in the Minifaros Project.

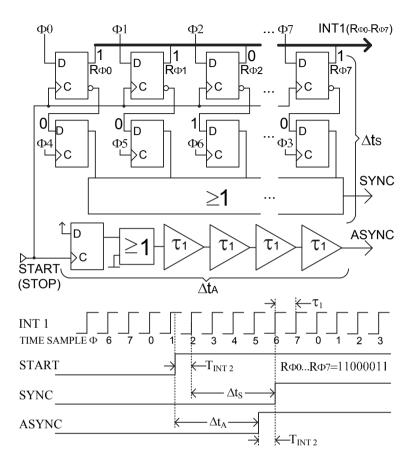

The fourth mission was to improve synchronization in the two-level interpolation architecture. As explained in Chapter V, the two-level interpolation architecture requires synchronization delays between the operations of the different resolution interpolators in order to render the results received from the levels compatible, and this delay needs to be compensated for in the asynchronous timing signal path. Non-ideal silicon wafers and circuit fabrication, however, will create mismatched propagation delays even in identical structures. Mismatch in the synchronization delays will shift the interpolation signals out of the interpolation region, creating error in the measurements. The delay offset can be cancelled out with external delay adjusting structures, which need to be calibrated externally for each circuit. The solution proposed here is a widening of the region covered by the second interpolation level. With only a few extra delay elements and registers

the second interpolation level can have an offset in its interpolation signals which does not detract from the performance of the device.

The thesis is composed of a summary part comprising 8 chapters and a publication part consisting of a total of 5 internationally peer-reviewed original publications. The summary part is organized as follows. Chapter 2 goes through the general TDC-related terms and factors affecting the measurement performance, Chapter 3 presents the most common time interval digitization methods and structures introduced in the literature, and Chapter 4 gives a short review of the original publications included in the thesis. Chapter 5 presents the structures developed during this work in order to make high-performance measurement possible, Chapter 6 presents the architecture and measurement results of the multi-channel TDC developed here especially for the needs of laser TOF distance measurement, including all the ideas and structures developed for it, Chapter 7 discusses and compares different TDC realizations, and finally Chapter 8 summarizes the findings of the thesis.

# 2 Time interval measurement uncertainty

The result (output) of an *ideal* time-to-digital converter should be exactly correct with any input time interval. The number of bits in the measurement result will be enormous due to the infinite resolution and unlimited maximum measurement time interval. External variables such as temperature changes, supply voltage variation and noise should have no influence on the result. *Real* time interval measurement devices have always weaknesses which introduce error into the measurement result and detract from measurement performance. This chapter presents the main terms which are used when describing TDCs and are needed in order to understand why the measured result is always an approximation of the true value.

Resolution and the equivalent term LSB (least significant bit) are used to describe the smallest time interval that the TDC can fractionate. The result given by the TDC (as a digital word) must be multiplied by the LSB value in order to reconstitute the measured time interval  $T_{\rm m}$ .

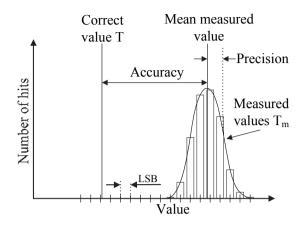

When the same time interval T is measured many times with a real TDC, several adjacent results usually turn up, as in Fig. 3, for example. The measured values  $T_m$  tend to vary around the mean value with a certain statistical variation that can be described with the standard deviation value  $\sigma$ , usually called the precision of the measurement. The precision usually depends on the time interval to be measured, and the maximum and root-mean-square (rms) values of the precision within a certain measurement range should be indicated when describing a TDC. Precision is very good performance parameter when comparing TDCs, because it includes the effects of all the *random* error sources. It should already be noted at this point that a small measurement LSB (high resolution) does not automatically mean good measurement precision.

The deviation of the mean measured value from the correct value can be called the averaged accuracy, or simply the accuracy, as in Fig. 3. Accuracy error results from *systematic* error sources, which can create a constant offset, or linearity error in the resulting measurement, which can fluctuate with the time interval. This constant offset can be easily subtracted from the result, because it is always the same, but a varying linearity error can be removed from the result only by means of look-up tables (LUT). The sources of error responsible for measurement uncertainty are presented in the following sections.

Fig. 3. Measurement uncertainty.

#### 2.1 Quantization error

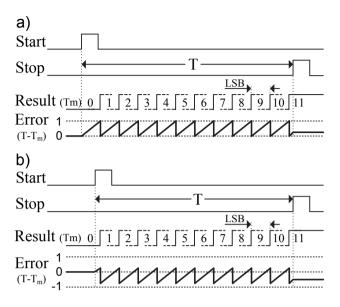

As in all analogue-to-digital converters (ADC), quantization error is a result of finite measurement resolution. The manner in which quantization creates measurement error and the variation in the amount of this error with the time interval are shown in Fig. 4. The asynchronous timing signal (start or stop) can arrive in any moment within the LSB, which causes the quantization error,  $Q_e$ , to be in the region  $(0 \le Q_e < 1) \times LSB$  with an rms error value of  $\sigma_q = LSB/\sqrt{12}$ . In TDCs based on a single conversion, Fig. 4 a), this is the final effect of the quantization noise. The start signal, for example, can propagate in a delay line and the stop signal will record the state of the delay line (Staszewski *et al.* 2006, Henzler *et al.* 2008, Lee *et al.* 2008). Fig. 4 b) shows the quantization error in a situation where both the timing signals, start and stop, are asynchronous with respect to the resolution of the measurement. The error region will now be  $(-1 < Q_e < 1) \times LSB$  with a rms value of  $\sigma_q = LSB/\sqrt{6}$  (Hewlett Packard).

Fig. 4. Quantization error with a) one, b) two asynchronous timing signal(s).

#### 2.2 Nonlinearity

Linearity error describes the deviation of the output value (measurement result) from the input value (time interval). In a linear device the output changes in direct proportion to the input value, yielding a straight line as the output-versus-input graph.

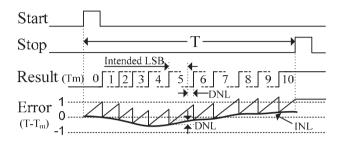

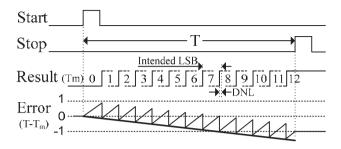

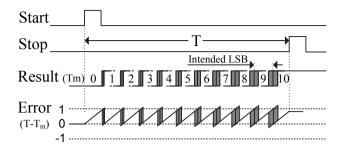

Measurement nonlinearity results from mismatch in the measurement resolution. A nonlinear current or capacitor in analogue measurement structures, nonhomogeneity in silicon process parameters and processed layout and systematic noise sources, for example, can create static differences with respect to the measurement LSBs, which interfere with the smooth growth of the measurement result with the time interval. The manner in which variation in the resolution of the measurement creates nonlinearity error is illustrated in Fig. 5. The differential nonlinearity (DNL) is the deviation of a single quantization step from the ideal value of 1 LSB. The LSBs and the errors within them are usually interconnected and interdependent, which means that the nonlinearity accumulates as the time interval becomes longer. The accumulated linearity error is called the integral nonlinearity (INL). The maximum INL defines the maximum

measurement error due to nonlinearity. As presented later on, the standard deviation of the INL,  $\sigma_{inl}$ , can be used to describe the effect of INL on the rms precision.

Fig. 5. Differential and integral nonlinearity.

#### 2.3 Stability

The stability of a measuring instrument describes how its metrological properties vary with changes in the environment and with time. Instability in TDC measurement results can occur due to changes in temperature, operating voltages and/or reference clock frequency, for example. An example of measurement error occurring when environmental changes lead to a change in measurement resolution is shown in Fig. 6. The measurement error usually increases smoothly with the time interval, and nonstability is often described as gain error.

A TDC needs a stabilization system in order to find out and adjust to the LSB in different circumstances. The measurement resolution has to be known in order that the measured digital output word should correlate with the true time interval. Usually an external reference clock, e.g. a temperature-compensated crystal oscillator (TCXO), is used for stabilization, i.e. to minimize the effects of PVT (process, voltage, temperature) variations. The propagation delay of adjustable delay elements can be locked to a reference clock cycle time (Rahkonen & Kostamovaara 1993), or else the prevailing resolution can be assessed by processing the result using a period estimation technique (Staszewski *et. al* 2006) or a separate calibration cycle (Nissinen *et al.* 2003).

Fig. 6. Stability error.

#### 2.4 Jitter sources

Random jitter sources worsen the statistical variation in the measurements obtained (precision). Noise in the supply and bias voltages and thermal noise in the TDC measurement structure create random time error in the signals participating in the measurement. Jitter can also accumulate in the time samples during measurement, as shown in Fig. 7. The rms effect of this inherent jitter on measurement precision can be denoted with  $\sigma_{tdc}$ .

The main input signals entering the TDC, the reference clock and the start and stop signals also contain jitter. The rms jitter from the reference clock,  $\sigma_{clk}$ , can be estimated from its phase noise spectrum (Hajimiri & Lee 1999). At short measurement time intervals the effect of clock jitter is low, usually below 1 ps with good oscillators, but at longer time intervals (>1 ms) the reference clock jitter starts to affect the measurement precision dramatically (Keränen *et al.* 2011). Jitter in the start and stop timing signals ( $\sigma_{start}$  and  $\sigma_{stop}$ ) is not actually a characteristic of the TDC, but is present in the precision value when the same time interval is measured many times over.

Fig. 7. Accumulating jitter in measurement time samples.

# 3 Time-to-digital conversion methods

Many time interval measurement methods and variations within them have been presented in the literature, and they can also be categorized in various ways. Analogue measurement methods make use of charges, currents and voltage differences, while digital methods are based on fast, discrete state changes. The design platform/technology can be FPGA, CMOS or BiCMOS, or else the TDC can be constructed from discrete components. Some TDCs use just a counter to digitize the interval between the timing signals (start and stop), which easily provides long measurement range. Some TDCs use only a single high resolution conversion structure, which allows high precision but lacks the necessary dynamic measurement range. The third solution is to use both of the above, a combination of a counter and high resolution timing signal interpolators, which is also known as the Nutt method (Nutt 1968).

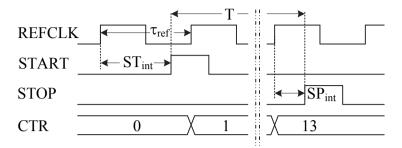

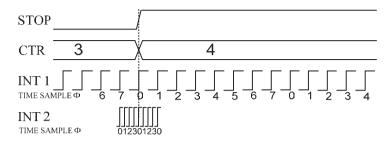

In the Nutt method, as presented in Fig. 8, a counter, CTR, counts the reference clock edges between the timing signals and is responsible for the measurement range. Counting is enabled by the start signal and disabled by the stop signal. Usually two interpolators, one for each timing signal, locate the timing signals within the reference clock cycle time  $\tau_{ref}$  with much higher resolution  $\tau_{int}$ . The interpolators indicate the time delay of the timing signals relative to the reference clock edges, so that their maximum measurement range is  $\tau_{ref}$ . The actual reference edge used for the interpolation depends on the architecture and can also be the next edge after the timing signal. An estimate,  $T_m$ , of the real time interval T consists of the counter result CTR and the digitized interpolation results of the start and stop signals,  $ST_{int}$  and  $SP_{int}$  respectively:

$$T_m = CTR \times \tau_{ref} + (SP_{int} - ST_{int}) \times \tau_{int}. \tag{1}$$

Fig. 8. Timing diagram of the Nutt method.

The Nutt method is usually used in time digitizers because it entails several benefits. The binary counting method of the counter provides an effective way of measuring long time intervals, and the measurement range can be extended simply by adding more bits to the counter. The measurement precision of a Nutt-based TDC worsens at time intervals longer than the reference clock cycle time, but only due to the reference source jitter, which can be very small. The measurement range of the interpolator (high resolution measurement unit) is only the reference clock cycle time, and it needs to be linear only in that region.

The Nutt-based TDCs are linear by nature. When the same time interval is measured many times and the timing signals are asynchronous with respect to the reference clock, these signals will also hit upon different locations within the reference clock period. The effects of static error sources, quantization error and measurement nonlinearity differ in every measurement and average out in the result if the same time interval is measured many times. In other words, the nature of the quantization and nonlinearity error sources changes from that of an accuracy problem to that of a precision problem. Only the static offset in the result persists when averaging, and that can easily be subtracted from the result.

In a Nutt-based measurement architecture the rms precision of the TDC,  $\sigma_{rms}$ , is a compound of the error sources presented in Chapter 2: the rms quantization error  $\sigma_q$ , the standard deviations of the integral nonlinearities in the start and stop interpolation channels,  $\sigma_{inl-st}$  and  $\sigma_{inl-sp}$  respectively, the rms value of the random inherent TDC jitter,  $\sigma_{tdc}$ , the rms reference clock jitter,  $\sigma_{clk}$ , and the rms jitter in the input timing signals,  $\sigma_{start}$  and  $\sigma_{stop}$ . When the error sources are not correlated their effects can be summed:

$$\sigma_{rms} = \sqrt{\sigma_a^2 + \sigma_{inl-st}^2 + \sigma_{inl-sp}^2 + \sigma_{tdc}^2 + \sigma_{clk}^2 + \sigma_{start}^2 + \sigma_{stop}^2}.$$

(3)

When using averaging, the number of measurements needed per time interval depends on the desired precision, the improvement in precision being inversely proportional to the square root of the number of averaged results. The precision without averaging may be 10 ps, for example, but it can be reduced to 0.1 ps by measuring the same time interval 10 000 times.

Several measurement blocks, a counter and two interpolators are needed in the Nutt method, unless the same interpolator can measure both of the timing signals. The measurement architecture, which includes several measurement levels, such as the counter and an interpolator, always needs a synchronization structure as well in order to achieve the correct overall result. The synchronization issue will be discussed in Chapter 5.

This chapter presents the mainstream time digitizing architectures. These can be used as stand-alone converters which directly digitize the time interval between the start and stop signals, but more often the high resolution structures (other than in the counter method) are used as interpolators in the Nutt method, and then they actually measure the interval between the timing signal (start or stop) and the reference signal, as presented in Fig 8. The referenced TDC related to the measurement method is marked with (N) if the Nutt method is used. Precision-based comparisons between architectures would be convenient and highly meaningful, but often this parameter is not reported at all in the literature. The performance and characteristics of the TDCs implemented here are discussed in Chapter 7.

#### 3.1 The counter method

The easiest way to measure time digitally is probably to use a reference clock of known frequency and a counter. The counter result states how many reference clock periods fit within the measurement time interval when the counting is enabled between the start and stop signals. The counter method provides a large linear dynamic range and good stability (Porat 1973), the structure of a counterbased TDC is straightforward and the measurement range can be extended easily by adding a few logic gates and registers.

The measurement resolution in the counter method depends on the counter frequency. One nanosecond resolution has been achieved with a 0.5 µm CMOS operating at a frequency of 1 GHz (Veneziano 1998), and 417 ps resolution with a 2.4 GHz reference clock in GaAs technology (Gao & Partridge 1991). The power consumption of a pure counter method is high because the capacitive loads in the

counter are driven with a high frequency. Averaging can also be used to improve the precision.

#### 3.2 Time-to-amplitude converter (TAC)

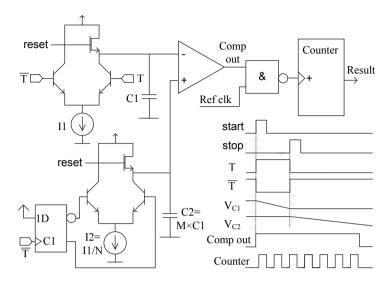

A time-to-amplitude converter (TAC) converts the measurement time interval first to a corresponding analogue voltage, which can then be digitized with an analogue-to-digital converter (ADC) (Henebry & Rasiel 1966, Porat 1973) or time stretching method (Nutt 1968). The analogue voltage can be created by (dis)charging a capacitor (C1 in Fig. 9) during the time interval with a constant current (I1 in Fig. 9). In the time stretching method, as presented in Fig. 9, the analogue voltage is discharged with a much smaller current (I2) after the stop signal and the stretched time interval is measured by enabling a counter during this time.

A 0.8 μm BiCMOS dual-slope time stretching converter (N) interpolates the cycle time of a 100 MHz reference clock with 32 ps resolution and better than 30 ps precision (Räisänen-Ruotsalainen *et al.* 2000). A resolution of 1 ps with a 100 MHz clock and 1 ms measurement range was obtained using a two-stage stretching method (Kalisz *et al.* 1987) with discrete components and a microprocessor (N), but the jitter level was about 5 ps and the linearity error 10 ps, so that the benefit gained from the high resolution was only minor. A pulse stretching-based 0.35 μm CMOS TAC (N) was shown to measure time intervals of up to 250 ns with 50 ps resolution (Chen *et al.* 2006) using a 80 MHz reference clock, while an integrated 1.2 μm CMOS TAC-ADC combination achieved a resolution of 107 ps within a measurement range of 8–24 ns (Gerds *et al.* 1994). A TAC-ADC combination constructed with discrete components and FPGA (N) was even able to achieve 0.1 ps resolution and 1.8 ps precision with a 200 MHz reference clock and had a wide, programmable measurement range (Keränen *et al.* 2011).

Digital measurement methods are usually preferred because analogue converters are more sensitive to the ambient temperature, are more susceptible to external disturbances, consume more power and are more difficult to realize in modern technologies. The time stretching method has also a long conversion time. The primary reason why analogue converters are still considered, however, lies in their superb resolution capability.

Fig. 9. An analogue dual-slope time stretching-based time-to-digital converter.

#### 3.3 Delay line-based measurement methods

The basic construction block in a digital time digitizer is usually called a delay element. It is a digital gate in which the propagation delay is controlled or measurable. Delay elements can be connected in several ways to form delay lines for time digitizing (Rahkonen & Kostamovaara 1993).

#### 3.3.1 Delay line with successive elements

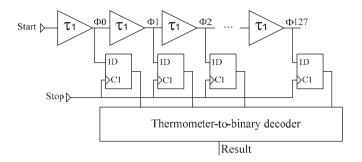

The simplest delay line consists of identical delay elements, e.g. buffer-type gates, placed one after another, as presented in Fig. 10. The signal which propagates through the delay line generates time samples for the delay element outputs with an even time delay. The start signal can propagate in the delay line and the stop signal can register the state of the delay line, which reveals how many element delays there were between the timing signals. In timing signal interpolation the reference signal usually propagates in the delay line and both timing signals (start and stop) record the state of the delay line.

Fig. 10. A delay line with successive elements.

The measurement resolution with successive elements depends mainly on the circuit technology and the structure of the delay elements. The buffer delay is about 250 ps in 0.35  $\mu$ m CMOS technology and around 40 ps in 90 nm CMOS. The propagation delay increases if the element contains functions such as delay adjustability, for example, to stabilize the delay at different temperatures. Then about 500 ps resolution can be achieved in 1.2  $\mu$ m CMOS over a wide temperature range (Rahkonen & Kostamovaara 1993). When the delay elements in a 0.8  $\mu$ m BiCMOS technology were connected to form a ring oscillator 125 ps resolution was obtained with a 500 MHz reference clock (N) (Herve & Torki 2002).

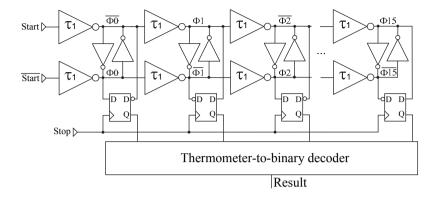

Since an inverter is the simplest logic component, the best resolution can probably be achieved when inverter-type elements are used. One disadvantage is that the delay line forms successive rising and falling edges, which makes the resolution inconstant, in addition to which the delay difference fluctuates with temperature. The problem can be solved by using a differential delay line in which two parallel inverters form rising and falling edges at every step and only the rising edges are used for time sample generation, for example. This structure has been used in the present work and also in other high resolution TDCs (Staszewski *et al.* 2006, Henzler *et al.* 2008). The cross-coupled inverters between the differential outputs in Fig. 11 maintain the opposite polarity of the signals in long delay chains. A differential inverter-based delay line in 90 nm CMOS technology creates time samples with ~20 ps resolution and can cover a 640 ps measurement range (Staszewski *et al.* 2006).

Fig. 11. Differential successive delay line.

Several methods have been presented for improving the LSB below the unit delay of a delay element. An on-chip RC delay line creates 4 time samples from the timing signal as well and records the state of the delay line, allowing 24.5 ps resolution and 22.4 ps precision to be achieved in 0.25 µm CMOS with a 320 MHz reference clock (N) (Mota *et al.* 2000). Resistors were used in the delay line, as shown in Fig. 12, to divide the differential inverter-based delay so that 4.7 ps resolution and 3.3 ps precision could be achieved in 90 nm CMOS when measuring over a 600 ps range (Henzler *et al.* 2008). The measurement method with successive elements is used as the first level in multi-level measurement structures in many TDCs, and was also used for this purpose here.

Fig. 12. A successive delay line with resistors.

Measurement with a successive delay line can be fast (flash-type), because the result is ready as soon as the measurement signals have arrived and the raw measurement data in the thermometer code are decoded to binary format. The size

of the digitizer increases with the measurement range and resolution, however, and a delay element and register are needed for every time sample. For example, if a high performance technology with 10 ps resolution were to interpolate the 10 ns period of a 100 MHz reference clock, 1000 delay elements and registering flip-flops would be needed. Another problem arises from the nonlinearity in the delay line. The delay mismatch of individual elements accumulates as the elements are placed one after another. Thus the measurement error can be large, especially in long delay lines (Toifl *et al.* 1999).

#### 3.3.2 The Vernier-based measurement method

The Vernier time measuring technique (Baron 1957) utilizes two delay generators having a small time difference, which corresponds to the resolution (LSB). At first the Vernier principle was realized with two startable oscillators having a slightly different oscillation frequency, the slower-frequency oscillator being enabled by the start signal and the faster one by the stop signal. The time samples of the faster oscillator caught those of the slower one up in every oscillation period. Measurement was complete when the oscillators produced time samples at the same time and the number of oscillations up to this point revealed the measurement time interval. A resolution of 1 ps with a 1  $\mu$ s range was achieved with an integrated bipolar gate array and two external oscillators with a clock rate of up to 700 MHz (Otsuji 1993).

In integrated circuits the Vernier principle is usually realized as presented in Fig. 13, with two separate delay lines having slightly different delays (Hoppe 1982). When the start signal propagates in the slower delay line and the stop signal in the faster delay line, the stop signal catches up with the start signal after a certain number of propagation steps. The number of propagated delay elements before the coincidence is multiplied by the delay difference between the elements (resolution) to obtain the measurement time interval. A Vernier TDC with delay lines in 0.7 µm CMOS can reach a resolution of 30 ps and a precision of 20 ps over a dynamic range of less than 4 ns (Dudek *et al.* 2000), while an integrated Vernier-based TDC in 0.35 µm CMOS with a counter and two ring oscillators (N) having a slightly different oscillation frequency has 37.5 ps resolution and 39 ps precision within an input range of over 50 ns with a 55 MHz reference clock (Chen *et al.* 2007). A Vernier-based interpolation architecture made with FPGA (N) was shown to measure a long 45 s range with 100 ps resolution using a 100

MHz reference clock (N). The TDC concerned achieved 70 ps precision using INL look-up tables (Szplet *et al.* 2000).

Fig. 13. A converter based on the Vernier principle.

In the Vernier method the faster time sample generator catches up with the slower one with a certain resolution at every propagation step, which can lead to a long conversion time. The amount of jitter increases in such delay lines, especially in long conversions, which detracts from the measurement precision. The nonlinearity in delay line-based Vernier TDCs can also be large because it now accumulates in two separate delay lines. Without these factors, the measurement resolution and precision could be very good.

#### 3.3.3 Pulse-shrinking delay line

The measurement time interval can be converted to a pulse of a width equal to the time interval. The pulse width can then be measured with a pulse-shrinking delay line (Rahkonen & Kostamovaara 1990). The delay elements in the pulse-shrinking delay line, two inverters in Fig. 14, shorten the pulse by an amount which corresponds to the LSB. After a certain number of delay elements the pulse vanishes totally, and this number reveals the pulse width. 50 ps resolution was obtained with 0.8 µm CMOS within a range of 100 ns (Karadamoglou *et al.* 2004).

Fig. 14. A TDC based on pulse shrinking in a delay line.

Another similar approach, the cyclic pulse-shrinking technique, uses a single shrinking element in the delay line and circulates the pulse in this delay line until it vanishes (Chen *et al.* 1997). A counter counts the rounds of circulation and indicates the result. Only one element is responsible for the shrinking, which improves the nonlinearity. A dynamic range of 18 ns was measured with 20 ps resolution and 76 ps precision (Tisa *et al.* 2003).

Size, nonlinearity and accumulating jitter are the biggest problems affecting pulse-shrinking delay lines. Their nonlinearity and size can be improved by adopting the cyclic version, although this multiplies the measurement time and the effect of jitter at the same time.

#### 3.4 Technological issues

Size, power consumption, production volume and unit price are the main parameters affecting the selection of a suitable technology. Discrete components offer a good platform for high resolution analogue-based TDCs in low volume production, especially because modern integrated circuit technologies concentrate on digital performance, but the other parameters mentioned above do not fit in well with discrete component implementation. FPGAs offer fast implementation and reconfiguration, but their measurement performance and unit price are usually no more than moderate with high production volumes. ASIC implementation is good where size, power consumption and high production

volumes are concerned. All the supporting blocks can be integrated into the same circuit and the measurement performance also approaches that of realizations designed with discrete components. Analogue signal processing, amplification, current sources etc. can be implemented quite easily in BiCMOS technology, whereas CMOS technology is the natural choice with pure digital TDCs.

Technology scaling in integrated circuits affects their delay generation. When the delay of a buffer in  $0.35~\mu m$  CMOS technology is about 250~ps, a similar gate in 65~nm CMOS technology, according to the simulations, requires a time of only about 30~ps. When the technology is scaled down, high resolution TDCs are possible with simpler measurement structures and circuit size and power consumption are also reduced.

Not all the negative factors are scaled down with the technology, however. The influence of process variations becomes more clearly visible as the transistors shrink in size, which increases the percentage variation in transistor characteristics. Where the maximum DNL of a differential inverter-type delay element in 0.35 µm CMOS (Paper III) was 15 ps (5% of the propagation delay), the maximum DNL in a similar delay element in 90 nm technology was 12 ps (60% of the propagation delay) (Staszewski *et al.* 2006). If the cycle time of a 100 MHz reference clock (10 ns) is interpolated with a successive delay line, 500 delay elements with a 20 ps propagation delay are needed in a highly developed technology, for example. The INL in this long delay line is higher than in a shorter delay line with longer delays but a smaller relative delay mismatch. The improvement in precision achieved with smaller quantization noise, as in (3), is thus at least partly cancelled out due to the higher nonlinearity.

Noise in the supply and control voltages is also proportionally larger when the operating voltage decreases, which creates more jitter in the delay elements. Although the circuit size becomes smaller with scaled technology, the price of the circuit can be higher, especially in low volume production, due to the higher NRE (non-recurring engineering) costs.

#### 3.5 Conclusions

Most of the TDCs published in the literature are based on the structures presented in this chapter. Several variations on these have been presented, but the original characteristics of the techniques usually remain. The goal is always the same, to obtain an accurate estimate of the measurement time interval with high resolution, low nonlinearity and low jitter. The measurement performance should also remain

within the overall measurement range. The Nutt method relaxes the accuracy requirements within the region of the reference clock cycle time, and for this reason it has been preferred for the present work.

Discrete component realization of the time-to-analogue converter together with an ADC can achieve very high resolution and precision, but interest in this alternative is usually limited by the large size, power consumption and costs. Integration of the analogue parts into a single chip is more or less possible with BiCMOS technologies, but it is difficult to achieve stable operation and low power consumption in combination with high measurement performance. Use was made of standard CMOS technologies and digital measurement architectures in the present work because they offer lot of possibilities at moderate cost, especially when the most modern technologies are avoided.

Delay elements can be combined in several ways for time digitization. Placing the elements one after another causes accumulation of the delay errors of the individual elements and the INL begins to detract from the measurement performance. The resolution is also low, especially in former integrated technologies, but it can be improved by using two parallel delay lines with different delays, as in the Vernier principle. Again long delay lines are needed and the measurement time increases, which begins to increase the jitter as well. The INL can be limited by using the same delay elements several times in cyclic measurement structures, but a feedback logic is usually needed for this, which increases the measurement time and jitter levels further. The measurement or conversion time is also important, because it is this that defines the measurement rate of the TDC.

Previous studies and structures were consulted for guidance on the design of the time interval measurement architecture for the present work, and it is evident that an accurate, high precision TDC can be created by combining the basic structures presented here. The successive delay line is a simple method for covering the measurement region, but long chains must be avoided because of the INL. Cyclic structures help with the INL but cannot be used excessively due to the increase in jitter. A delay difference in parallel delay elements, as in the Vernier principle, provides an effective method for attaining high resolution. Other desired features in a TDC may be a high measurement rate, calibration-free operation, no need for post-processing of the results, full system integration in a small-sized circuit, standard, cheap technology, low power consumption and flexibility of the timing signals and measurement intervals. These characteristics formed a basis for the TDC development work carried out here.

## 4 Overview of the original publications

The five original publications included in this thesis describe the developmental work carried out with respect to time-to-digital converters. Four TDC circuits were designed, and the papers present the structure, operation, measurement results and the elements behind their performance. This chapter presents an overview and the main messages of all five publications.

# 4.1 Paper I (2005), A Delay Line Based CMOS Time Digitizer IC with 13 ps Single-shot Precision

Paper I, originally presented at the IEEE International Symposium on Circuits and Systems in Kobe, Japan, in 2005, describes the first TDC circuit designed for this work. Like all the others, it was realized with 0.35 µm CMOS technology, which was quite modern at that time. The Nutt-based measurement core was composed of a counter and stabilized two-level interpolators. Many structures were adopted from previous high precision TDCs designed in the same laboratory, especially those of Mäntyniemi et al. (2002). A successive delay line was used for the first level of interpolation within the cycle time of a 145 MHz reference clock. A differential inverter-based delay line structure was presented, which improved the resolution and nonlinearity as compared with a one-sided realization. The second interpolation level was composed of parallel load capacitor scaled delay elements and provided an LSB width of 13.5 ps. The rms precision was 12.4 ps and the maximum measurement range up to 226 µs. The measurement precision was the best published up to that time, and the architecture seemed promising for further development. The main weaknesses were the dependence on a high reference clock frequency and the external calibration, which had to be performed for each circuit separately.

# 4.2 Paper II (2006), A CMOS Time-to-Digital Converter with better than 10 ps Single-Shot Precision

Paper II, published in the IEEE Journal of Solid-State Circuits, presents the second TDC circuit. The paper goes through the factors affecting measurement precision in Nutt-based converters and presents a new delay line structure for timing signal interpolation. The reference recycling method reduces the number

of delay elements in the successive delay line, which improves the INL. The reference frequency can also be a fraction of the internal delay line frequency.

The TDC measures time intervals up to 204  $\mu s$  with 12.2 ps resolution. The frequency of the reference source can be chosen freely and a 5 MHz signal generator was used in the measurements. The interpolation factor,  $\tau_{ref}/LSB$ , was hence 16384 and was achieved using only 20 effective delay elements. The TDC achieved 13.0 ps rms precision alone and 8.1 ps with an INL look-up table (INL-LUT). External calibration was still needed for every circuit in order to compensate for the synchronization delay mismatches. This publication is still the second most cited TDC article of all time in the IEEE *Xplore* digital library.

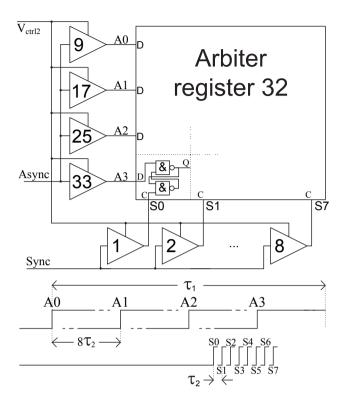

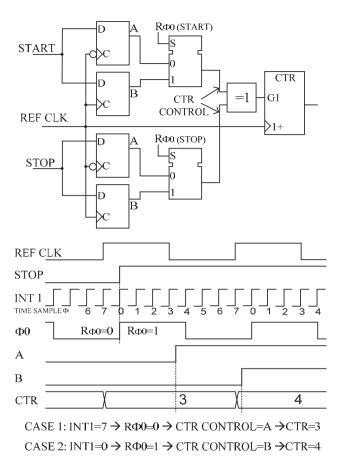

## 4.3 Paper III (2009), Synchronization in a Multi-level CMOS Time-to-Digital Converter

Paper III, published in IEEE Transactions on Circuits and Systems I: Regular Papers, presents the third TDC circuit to be designed in the present connection. It is primarily concerned with synchronization problems and the structures required in converters based on multiple measurement blocks. The results obtained at the counter and interpolation levels can be inconsistent, if the operations of these levels are not reliably synchronized. The paper presents a technique for avoiding the synchronization delay mismatch problem. The measurement range at the second interpolation level can be widened in both directions over the effective range, which secures the operation of the second interpolation level in the case of a mismatch.

The TDC contained only 6 differential delay elements at the first interpolation level. The measurement resolution was 9.6 ps and the maximum measurement range 1 ms. The rms precision of the TDC was 10.6 ps, but a precision of 6.0 ps was achieved when the static interpolation nonlinearity was removed with an INL-LUT. A 6 MHz reference source was used in the measurements. The performance in terms of precision was again the best among the known long-range digital TDCs. The main needs for further development concerned usability. The programming and result readout were nonstandard and difficult to use.

# 4.4 Paper IV (2009), Multiplying Delay Locked Loop (MDLL) in Time-to-Digital Conversion

Paper IV was published in the proceedings of the International Instrumentation and Measurement Technology Conference, Singapore, 2009. It deals with the reference recycling technique, its properties and capabilities as a single interpolation level in modern technologies. The reference recycling delay line, or synonymously, the multiplying delay locked loop (MDLL), can form a compact, efficient time digitizer unit as a stand-alone component with the counter in a small line width technology where the propagation delay of the delay element (LSB) can be few tens of picoseconds. The size of the device can be small and nonlinearity good, because the delay line is short and the counter is responsible for the long range. Jitter and area calculations were performed for the MDLL. The measurement results were based on the TDC presented in Paper III.

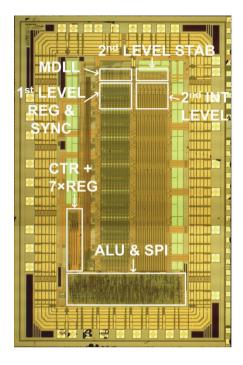

## 4.5 Paper V (2012), A Multi-Channel High Precision CMOS Time-to-Digital Converter for Laser Scanner-Based Perception Systems

Paper V was published in IEEE Transactions on Instrumentation and Measurement. It presents a TDC that was especially suited for the needs of laser time-of-flight (TOF) distance measurement. The characteristics, architecture and measurement results of this latest circuit are also presented in Chapter 6.

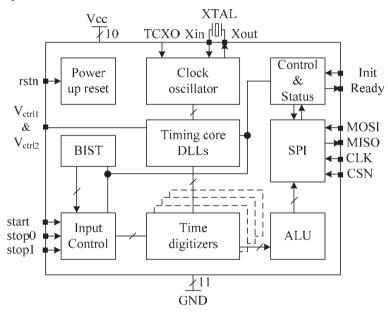

The TDC has 7 measurement channels, so that it can detect the start and 6 successive stop signals in one measurement. Several new structures and functions were integrated into the circuit, which improve its usability, reduce the number of external components and are needed for serial production. The internal oscillator makes possible to use a crystal as a reference. The programming and data readout interface is a standard serial peripheral interface (SPI), and the integrated arithmetic logic unit (ALU) calculates the results inside the TDC. A build-in self-test (BIST) can be used for circuit testing at the wafer level. The TDC can also handle situations in which stops arrive before the start, which creates negative measurement results.

The TDC measures time intervals up to  $\pm 74~\mu s$  with 8.9 ps resolution. The rms precision was 8.6 ps without an INL-LUT and 8.0 ps with an INL-LUT. The measurements were carried out using a 20 MHz reference clock.

# 5 Structures for a high performance time-todigital converter

This chapter goes through the principles and structures developed and improved during the work on this thesis in order to make high performance time-to-digital conversion possible. The whole TDC was constructed from the parts presented in Chapter 6.

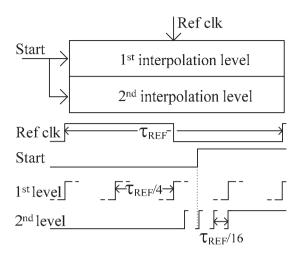

#### 5.1 Two-level (coarse-fine) measurement architecture

Recent high precision TDCs have usually used a two-level architecture to digitize the interval between the timing signals (Huang *et al.* 2007, Lee & Abidi 2008) or between the timing and reference signals in the Nutt method (Mäntyniemi *et al.* 1997, Chen *et al.* 2007, Mäntyniemi *et al.* 2009, Papers I–V). The two-level measurement principle adopted in the interpolation is presented in Fig. 15. The first interpolation level, also known as the coarse interpolator, locates the timing signal within the reference clock cycle with moderate resolution. This interpolation is often based on a successive delay line in which the resolution is determined by the propagation delay of a digital gate. The second interpolation level, also known as the fine interpolator, locates the timing signal within the result of the first level, i.e. with higher resolution. In other words, sub-gate delay measurement techniques are employed to perform another measurement within the resolution of the first level, which also represents the dynamic range of the second measurement level.

The two-level architecture entails several benefits as far as high resolution measurement is concerned. The number of delay elements and registers is reduced, because the second, high resolution measurement is performed only within a small range, as in Fig. 15. A 100 ns reference clock cycle, for example, can be interpolated with 10 ps resolution by means of 10000 delay elements and registers on one interpolation level, but the same task requires only 100 delay elements and registers for both the coarse and fine interpolations in a two-level setup. The fact that less delay elements participate in the measurement also means that the INL and power consumption can be lower.

Fig. 15. Interpolation on two levels. Revised from [II] © 2006 IEEE.

#### 5.2 Coarse interpolation

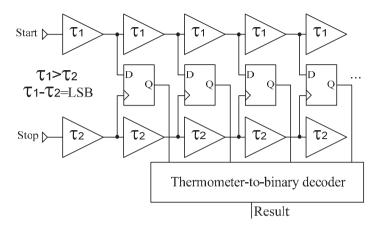

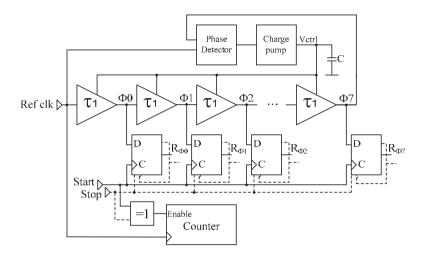

#### 5.2.1 Basic successive delay line structure

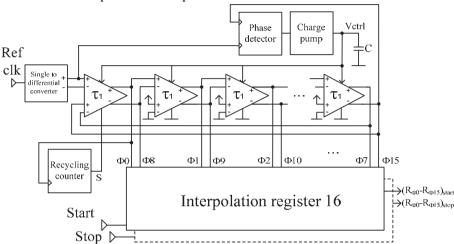

The coarse interpolation in the circuits designed here is based on continuous and uniform reference signal propagation in a delay element chain. The external reference signal creates time samples with an even time delay,  $\tau_1$  in Fig. 16, in a delay line with identical cascaded delay elements. The timing signals, start and stop, define the prevailing time sample, and the register outputs,  $R_{\Phi 0} - R_{\Phi 7}$  in Fig. 16, reveal the coarse location of the timing signal within the reference clock cycle. The counter is connected to count the reference clock edges occurring between the timing signals.

Stabilization in the face of process, voltage and temperature (PVT) variations is handled with a delay locked loop (DLL) structure, also shown in Fig. 16. The beginning and end of the delay line are connected to a phase detector, which controls a charge pump that adjusts the delay control voltage  $V_{\text{ctrl}}$  in the delay line. The control voltage is adjusted until the phase detector receives both signals, the signal which has gone through the delay line and the new reference edge, at the same time, which means that the delay corresponds to the reference clock

cycle time  $\tau_{ref.}$  The DLL stabilizes the delay in the delay line automatically and continuously when the reference signal is propagated in the delay line.

Fig. 16. Basic DLL-stabilized delay line interpolation structure with counter. Revised from [II] © 2006 IEEE.

The delay line structure presented in Fig. 16 has certain drawbacks which had to be considered here. The interpolation signals  $\Phi 0...\Phi 7$  have to be identical, e.g. rising edges, so that the time samples will be uniform in every situation. If both rising and falling edges were used, the interpolation LSBs would vary in length with PVT changes. The delay elements in the present structure have to be of the buffer type rather than the inverter type, which would increase the delay in the delay elements and detract from the achievable resolution and precision.

Another drawback is that the total delay in the delay line has to cover the reference clock cycle time. This forces us to use a high frequency reference source and long delay lines, especially as the delay in modern delay element technologies is short. A high frequency external oscillator nevertheless increases the cost and power consumption of the TDC. Operation with a low cost, low frequency external crystal would be the most desirable case.

The third issue is that the length of the delay line, i.e. the number of delay elements in it, affects the linearity of the interpolation time samples (Toifl *et al.* 1999). The DLL stabilization structure matches the beginning and end of the delay line, but time samples taken between these points are not controlled (Paper II). Delay variation (DNL) between the elements accumulates to yield INL, as

discussed earlier, and this time error in the interpolation time samples is also transferred to the measurement result and detracts from the precision. The delay in the delay line should be reduced, but this would further increase the reference clock frequency.

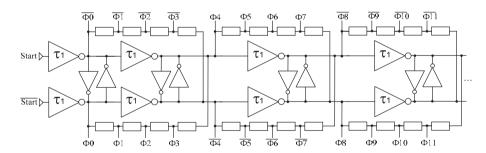

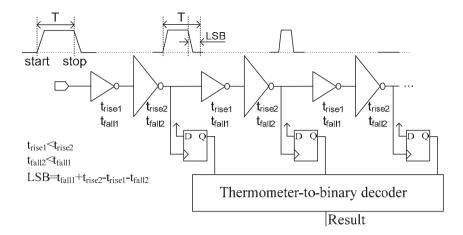

#### 5.2.2 Reference recycling delay line

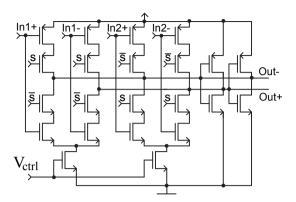

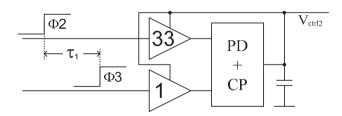

To relieve the problems presented above, a new delay line structure for timing signal interpolation was designed here (Paper II). This structure is based on a multiplying delay-locked loop (MDLL), which was originally designed to prevent excessive jitter accumulation in frequency synthesis (Waizman 1994). The idea is to recycle the reference signal several times in the delay line before the next jitter-free reference edge is passed to that delay line. A suitable MDLL delay line structure for timing signal interpolation is shown in Fig. 17. The delay elements, as in the transistor-level diagram in Fig. 18, are differential delay-adjustable multiplexers with two input channels. The two input channels are needed only in the first element, but all the elements are identical in order to maintain even-sized time samples. Note that the end of the delay line in Fig. 17 is cross-coupled back to the second channel of the first element. This is necessary in order to achieve pulse propagation.

The delay line operates as follows. The external reference signal rising edge is first converted to a differential and then passed to the delay line. After this the input channel of the first element is changed and the reference begins to circulate in the closed loop. After a certain number of rounds (counted by the recycling counter) the first element lets the next jitter-free reference edge enter the loop. A phase detector and charge pump control the delay so that the delay in the recycled delay line becomes equal to the reference clock cycle time.

When the reference signal is recycled in the coarse interpolator the delay line can be short, which reduces the size of the device and improves the INL. The inverting differential delay element structure, presented in Paper I, makes its propagation delay smaller than that of a buffer-type delay element, which improves the interpolation resolution. As in Fig. 11, opposite signal phases are cross-coupled with inverters, which improves the DNL and the effect of jitter compared with a one-sided element. The propagation delay in an element depends on both the rising and the falling edge, which balance each other out in the case of an extra load or supply noise in the other line, for example.

The reference recycling in a closed loop increases the inherent delay line jitter if the reference frequency is reduced, because the thermal noise and the noise in the supply and bias voltages have more time to create random error in the interpolation time samples. The effects of quantization noise and INL in the delay line nevertheless still dominated in terms of the precision of the designed circuits when a 10 MHz crystal was used as the reference source. Thus the recycling delay line structure also makes use of as low frequency a reference as possible, which will reduce power consumption.

Fig. 17. A reference recycling delay line for timing signal interpolation. Revised from [II] © 2006 IEEE.

Fig. 18. A differential delay-adjustable delay element with two input channels. Revised from [I]  $\odot$  2005 IEEE.

#### 5.3 Fine interpolation

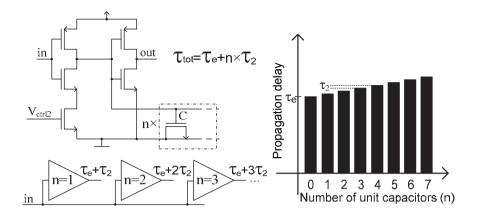

### 5.3.1 Load capacitor-scaled delay lines

The second interpolation level in the TDCs designed here was based on load capacitor scaling in delay elements connected in parallel (Mäntyniemi *et al.* 1997). The propagation delay of a buffer-type delay element, as presented in Fig. 19, can be increased by adding extra capacitance inside the element. When a rising edge propagates through the element the extra charge needs to be discharged, which creates an additional delay. Changes in the propagation delay resulting from the placement of different numbers of unit capacitors of the same size within the elements are shown in Fig. 19. The total propagation delay  $\tau_{tot}$  consists of basic delay  $\tau_{e}$  in a delay element and the delay from a single unit capacitor  $\tau_{2}$  multiplied by the number of unit loads n.

Fig. 19. A load capacitor-scaled delay element. Revised from [I] © 2005 IEEE.