### University of Patras

COMPUTER ENGINEERING AND INFORMATICS DEPARTMENT

MASTER PROGRAM: HARDWARE AND SOFTWARE OF INTEGRATED SYSTEMS

#### MASTER THESIS

## Energy Efficient Instruction Decoding in Application-Specific Instruction-Set Processors

### Christos I. Kargas

Supervisor Professor: Constantinos Goutis Thesis Committee: Constantinos Goutis

> Dimitrios Nikolos Georgios Theodoridis

Patras, 2012

### ΠΑΝΕΠΙΣΤΗΜΙΟ ΠΑΤΡΩΝ

#### ΤΜΗΜΑ ΜΗΧΑΝΙΚΩΝ Η/Υ ΚΑΙ ΠΛΗΡΟΦΟΡΙΚΗΣ

Προγραμμα Μεταπτυχίακων Σπουδών Ολοκληρώμενα Συστήματα Υλίκου και Λογισμικού

### ΜΕΤΑΠΤΥΧΙΑΚΗ ΔΙΠΛΩΜΑΤΙΚΗ ΕΡΓΑΣΙΑ

## Αποκωδικοποίηση Εντολών για Χαμηλή Κατανάλωση Ενέργειας σε Επεξεργαστές Συνόλου Εντολών Ειδικού Σκοπού

### Χρήστος Ι. Κάργας

Επιβ βέπων Καθηγητής: Κωνσταντίνος Γκουτης Τριμεβής Επιτροπή: Κωνσταντίνος Γκουτης

> Δημήτριος Νικολος Γεώργιος Θεοδωριδής

Πάτρα, 2012

## Energy Efficient Instruction Decoding in Application-Specific Instruction-Set Processors

### **Christos Kargas**

**Master Thesis**

Computer Engineering and Informatics Department University of Patras, Greece

and

IMEC / Holst Centre Eindhoven, The Netherlands

Patras, November 2012

### **Acknowledgements**

The hereby presented master thesis, entitled "Energy Efficient Instruction Decoding in Application-Specific Instruction-Set Processors", is a description of the research during the Master Thesis and its results, for the Master of Science program "Hardware and Software of Integrated Systems" of the Department of Computer Engineering and Informatics belonging to the Faculty of Engineering of the University of Patras. The study was conducted in cooperation with IMEC/Holst Centre in Eindhoven, The Netherlands.

The assignment and supervision of the present study was conducted by professor Dr. Constantinos Goutis of the Department of Electrical and Computer Engineering of the University of Patras, whom I'd like to thank warmly for his scientific guidance and moral support as well as giving me the great opportunity to perform my thesis abroad.

I would also like to thank deeply principal researcher Jos Huisken for accepting me in IMEC/Holst Centre and his invaluable guidance and counseling during this thesis. Our endless talks on many matters both theoretical and technical have enriched my knowledge, have served me well during my thesis and are sure to be of much value to me later on.

I would also like to express my sincere gratitude to professor Francky Catthoor of IMEC-Leuven for selecting me among the candidates, for the valuable advice and motivation he provided and his inspiring influence. Additionally, senior researcher Jos Hulzink of IMEC/Holst Centre for his assistance in technical matters, sharing his technical knowledge on the development framework used for this thesis and for his accurate and timely suggestions that helped me overcome many major problems in my thesis.

Special thanks to IMEC/Holst Centre for equipment supply and the facilities they provided and Target Compilers for allowing the use of the tools and the feedback on several matters.

I would like to thank senior researcher Mario Konijnenburg of IMEC/Holst Centre for his assistance in several occasions, PhD candidate António Artés Garcia for willfully sharing his knowledge, his technical assistance and always keeping the spirits high along with PhD candidate Bo Liu in the office we shared, Georgios Selimis and Ioannis Giannis for their advice and helping me adapt to

the Netherlands and of course all the people in the ULP-DSP group of IMEC/Holst Centre who are always willing to help and for the friendly environment. Finally, Stefania Dakourou for allowing me to use some of her work for comparisons.

Closing, I would like to thank professor Dr. Dimitrios Nikolos of the Department of Computer Engineering and Informatics of the University of Patras and assistant proffessor Dr. George Theodoridis of the Department of Computer and Electrical Engineering of the University of Patras who along with the supervisor Dr. Constantinos Goutis, make up the committeee of my master thesis.

Christos I. Kargas

Patras, November 2012

## Ευχαριστίες

Η παρούσα διπλωματική εργασία, με θέμα "Αποκωδικοποίηση εντολών για χαμηλή κατανάλωση ενέργειας σε Επεξεργαστές Συνόλου Εντολών Ειδικού Σκοπού (ASIPs) ", είναι μία περιγραφή της έρευνας κατά τη διάρκεια της μεταπτυχιακής διπλωματικής εργασίας και των αποτελεσμάτων της, για το Μεταπτυχιακό Πρόγραμμα Σπουδών Όλοκληρωμένα Συστήματα Υλικού και Λογισμικού' του Τμήματος Μηχανικών Η/Υ και Πληροφορικής της Πολυτεχνικής Σχολής του Πανεπιστημίου Πατρών. Η μελέτη διενεργήθηκε σε συνεργασία με το ερευνητικό κέντρο IMEC/Holst Centre με βάση το Αϊντχόφεν της Ολλανδίας.

Η ανάθεση και η επίβλεψη της παρούσας εργασίας έγινε από τον καθηγητή κ. Κωνσταντίνο Γκούτη, του τμήματος Ηλεκτρολόγων Μηχανικών και Τεχνολογίας Υπολογιστών του Πανεπιστημίου Πατρών, τον οποίο και θα ήθελα να ευχαριστήσω θερμά για την επιστημονική του καθοδήγηση και την στήριξη, καθώς και για την ευκαιρία που μου έδωσε να πραγματοποιήσω την εργασία μου στο εξωτερικό.

Θα ήθελα επίσης θα ευχαριστήσω εκ βαθέων τον επικεφαλή ερευνητή Jos Huiken που με δέχτηκε στο IMEC/Holst Centre καθώς και για την πολύτιμη καθοδήγηση και τις συμβουλές κατά τη διάρκεια της εργασίας. Οι ατελείωτες συζητήσεις μας σε διάφορα θέματα, τόσο θεωρητικά όσο και πρακτικά εμπλούτισαν τις γνώσεις μου, με βοήθησαν πολύ κατά τη διάρκεια της εργασίας και είναι σίγουρο ότι θα μου είναι ακόμα πιο χρήσιμες στο μέλλον.

Θα ήθελα ακόμη να ευχαριστήσω τον καθηγητή Francky Catthoor του IMEC-Leuven που με επέλεξε ανάμεσα στους υποψήφιους, για τις πολύτιμες συμβουλές και την ενθάρρυνση που μου παρείχε καθώς και την έμπνευση που μου ενέπνευσε. Επίσης τον έμπειρο ερευνητή Jos Hulzink του IMEC/Holst Centre για τη συνδρομή του σε τεχνικά θέματα, για τις τεχνικές γνώσεις που μου μετέδωσε στην αναπτυξιακή πλατφόρμα που χρειάστηκε σε αυτή την εργασία καθώς και για τις εύστοχες και έγκαιρες συστάσεις του που με βοήθησαν να ξεπεράσω πολλά μεγάλα εμπόδια στην εργασία μου.

Ένα μεγάλο ευχαριστώ στο ερευνητικό κέντρο IMEC/Holst Centre για τον εξοπλισμό και τις εγκαταστάσεις που μου παρείχε και στην εταιρία Target Compilers που μου επέτρεψε να χρησιμοποιήσω την αναπτυξιακή πλατφόρμα της και για την απάντηση που μου έδωσαν σε διάφορα θέματα όταν επικοινώνησα μαζί τους.

Θα ήθελα ακόμη να ευχαριστήσω τον έμπειρο ερευνητή Mario Konijnenburg του

IMEC/Holst Centre για την βοήθεια του σε διάφορες περιπτώσεις, τον υποψήφιο διδάκτορα Antonio Artes Garcia για την προθυμία του στο να μοιραστεί τις γνώσεις του ή να βοηθήσει σε τεχνικά θέματα μαζί με τον υποψήφιο διδάκτορα Βο Liu στο γραφείο το οποίο μοιραζόμασταν, τον Γεώργιο Σελίμη και τον Ιωάννη Γιάννη για τις συμβουλές τους, τη στήριξη και την βοήθεια που μου προσέφεραν στην προσαρμογή στην Ολλανδία και φυσικά όλους στην ομάδα ULP-DSP του IMEC/Holst Centre για τη προθυμία να βοηθήσουν και για το φιλικό περιβάλλον. Τέλος την Στεφανία Δακουρού, που μου επέτρεψε να χρησιμοποιήσω ένα τμήμα της εργασίας της για διάφορες συγκρίσεις.

Κλείνοντας, θα ήθελα να ευχαριστήσω τον καθηγητή κ. Δημήτριο Νικολό του τμήματος Μηχανικών Η/Υ και Πληροφορικής του Πανεπιστημίου Πατρών και τον καθηγητή κ. Γεώργιο Θεοδωρίδη του τμήματος Ηλεκτρολόγων Μηχανικών και Τεχνολογίας Υπολογιστών του Πανεπιστημίου Πατρών που μαζί με τον επιβλέπων καθηγητή κ. Κωνσταντίνο Γκούτη αποτελούν την εξεταστική επιτροπή της μεταπτυχιακής διπλωματικής εργασίας μου.

Χρήστος Ι. Κάργας

Πάτρα, Νοέμβριος 2012

### **Abstract**

With commercial processor design tools, a designer can quickly design a Cprogrammable ASIP for a specific application domain. There are several such ASIPs available for both wireless (UWB baseband processing), encryption, and biomedical processing (particularly for ECG beat detection). In traditional CPUs and DSPs the impact of the instruction-set definition and the complexity of the instruction decoder can be substantial, especially in terms of power consumption. Fully orthogonal VLIW processors, do not incur the cost of an instruction decoder that severely. Instead the instruction word becomes very large, thereby shifting the (power-)cost to the program memory or instruction cache. For the purposes of this thesis a SIMD processor is developed and is compared to a soft-SIMD to observe its area, performance and energy efficiency for a bioimaging benchmark and how the processor description in the ASIP language nML, defines the generated HDL. This SIMD processor is turned into orthogonal and using iterative experiments it is investigated, what is the impact on power while manipulating the instruction-set architecture in combination with the program memory size. It is also investigated how instruction-set re-configuration can be exploited to improve power efficiency. Using this investigation guidelines for low-power ASIP design can be produced.

## Εκτεταμένη Περίληψη

Με τη σύγχρονη τεχνολογία σχεδιασμού επεξεργαστών, ο σχεδιαστής μπορεί με ευκολία να σχεδιάσει ένα προγραμματιζόμενο Επεξεργαστή Συνόλου Εντολών Ειδικού Σκοπού (ASIP - Application-Specific Instruction-set Processor) για ένα συγκεκριμένο εύρος εφαρμογών. Υπάρχουν διάφοροι τέτοιοι επεξεργαστές διαθέσιμοι για ασύρματες εφαρμογές, κρυπτογράφηση και βιοϊατρικές εφαρμογές (π.χ. στον αλγόριθμο εντοπισμού χτύπου ηλεκτροκαρδιογραφήματος). Στους παραδοσιακούς επεξεργαστές και επεξεργαστές σήματος (DSP - Digital Signal Processor) ο ορισμός του συνόλου εντολών και η πολυπλοκότητα έχουν μεγάλη επίδραση, ειδικά στην κατανάλωση ισχύος. Μία πιθανή λύση σε αυτό το πρόβλημα είναι οι ορθογώνιοι επεξεργαστές μεγάλου μεγέθους λέξης εντολής (VLIW - Very Large Instruction Word).

Με τον όρο ορθογώνιο επεξεργαστή, ορίζεται ένας επεξεργαστής οριζόντιου σύνολου εντολών, άρα ένας επεξεργαστής στον οποίο μπορεί να υπάρξει κάθε διαθέσιμος συνδυασμός μεταξύ των διαθέσιμων εντολών και των μεθόδων διευθυνσιοδότησης για πρόσβαση στη μνήμη και το αρχείο καταχωρητών. Οι ορθογώνιοι επεξεργαστές δεν επιβαρύνουν τόσο τον αποκωδικοποιητή εντολών. Αντί αυτού το μέγεθος της λέξης της εντολής γίνεται πολύ μεγάλο, και έτσι μετατίθεται το ενεργειακό κόστος στην μνήμη εντολών προγράμματος (program memory )ή την κρυφή μνήμη εντολών προγράμματος (instruction cache).

Για τους σκοπούς αυτής της διπλωματικής εργασίας, αναπτύχθηκε ένας επεξεργαστής SIMD, ο οποίος συγκρίνεται με έναν soft-SIMD για να μελετηθούν η απαιτούμενη περιοχή στο ενσωματωμένο, επιδόσεις και κατανάλωση ενέργειας για μία βιοϊατρική εφαρμογή, καθώς και το πως η περιγραφή ενός επεξεργαστή στη γλώσσα περιγραφής επεξεργαστών ASIP nML ορίζει την παραγούμενη γλώσσα περιγραφής υλικού (HDL - Hardware Description Language). Ο επεξεργαστής αυτός μετατρέπεται σε ορθογώνιο, και με τη χρήση επαναληπτικών πειραμάτων μελετάται η επίδραση στην κατανάλωση ενέργειας κατά τη διάρκεια αλλαγών στην αρχιτεκτονική του συνόλου εντολών και του μεγέθους της μνήμης εντολών προγράμματος. Ακόμη μελετάται πως μπορεί να εκμεταλλευτεί ο σχεδιαστής την αναδιάρθρωση του συνόλου εντολών για να βελτιώσει την κατανάλωση ενέργειας (εικόνα 1).

Οι επεξεργαστές ASIP είναι πολύ διαδεδομένοι τελευταία γιατί μπορούν και συνδυάζουν επιδόσεις, χαμηλή κατανάλωση ενέργειας και κυρίως ευελιξία. Με αυτούς μπορούμε πιο εύκολα να βρούμε τη χρυσή τομή ανάμεσα στα διάφορα

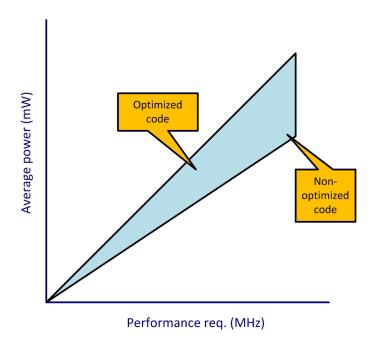

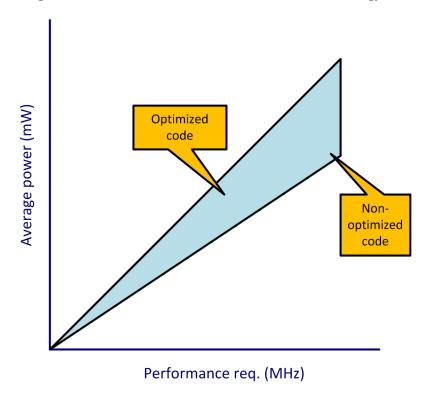

**Εικόνα 1:** Μέση κατανάλωση ισχύος και συχνότητα λειτουργίας επεξεργαστών ανάλογα με το επίπεδο βελτιστοποίησης του κώδικα σε εμπορικούς επεξεργαστές ASIP

χαρακτηριστικά του επεξεργαστή που θέλουμε, με αποτέλεσμα έναν επεξεργαστή αρκετά ισχυρό και ενεργειακά αποδοτικό για το εύρος εφαρμογών που θέλουμε. Δεν πρέπει να ξεχνάμε ότι στη σύγχρονη αγορά ενσωματωμένων συστημάτων, η κατανάλωση ενέργειας είναι ένα από τα μεγαλύτερα προβλήματα. Ωστόσο, καθώς η τεχνολογία προχωράει με αλματώδεις ρυθμούς, μερικές από τις λύσεις που έχουν δώσει οι σχεδιαστές σε διάφορα προβλήματα που αντιμετώπιζαν στο παρελθόν μελετούνται ξανά, με σκοπό να βρεθεί μία πιο αποτελεσματική λύση.

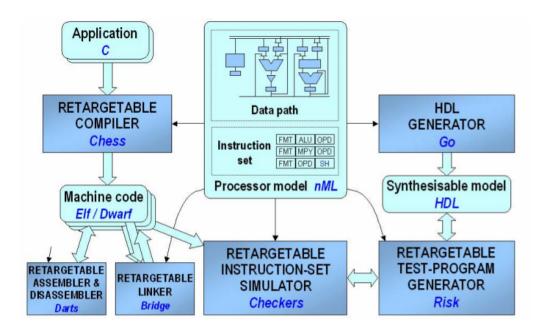

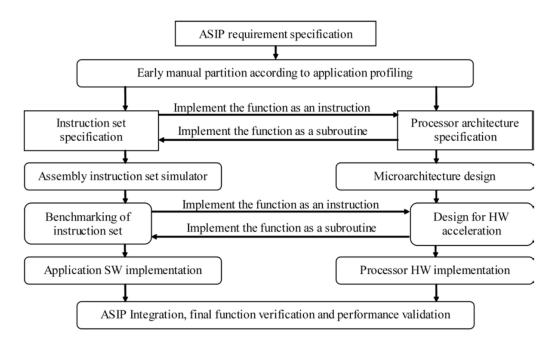

Για την ανάπτυξη τους, οι επεξεργαστές ASIP χρησιμοποιούν ένα ειδικό περιβάλλον ανάπτυξης με εξελιγμένα εργαλεία ανάπτυξης (εικόνα 2), με τα οποία η ανάπτυξη ενός επεξεργαστή ASIP μπορεί να γίνει σε πολύ λιγότερο χρόνου από όσο χρειάζεται ένας κανονικός επεξεργαστής. Προσφέρουν μία πλήρη σουίτα για το σχεδιασμό του επεξεργαστή από το σχεδιασμό της αρχιτεκτονικής του επεξεργαστή, τον ορισμό του συνόλου εντολών και των λειτουργιών μέχρι την προσομοίωση εφαρμογών και την παραγωγή γλώσσας περιγραφής υλικού. Οι διαθέσιμες δυνατότητες προσομοίωσης μπορούν να συνδυαστούν με τις δυνατότητες αναγνώρισης χαρακτηριστικών (profiling)για να ερευνηθούν διαφορετικές υλοποιήσεις και μέσω επαναληπτικών αλλαγών στον αρχικό κώδικα να βρεθεί η ιδανική υλοποίηση για ένα συγκεκριμένο εύρος εφαρμογών.

Πολλές φορές η κατανάλωση ισχύος και η κατανάλωση ενέργειας συγχέονται και θεωρείται ότι είναι το ίδιο. Αυτό είναι λάθος. Η χαμηλή κατανάλωση ισχύος δεν μας εξασφαλίζει και χαμηλή κατανάλωση ενέργειας. Στα σύγχρονα ενσωματωμένα συστήματα, η ενέργεια είναι ο καθοριστικός παράγοντας που πολλές φορές καθορίζει την επιτυχία ενός επεξεργαστή. Η χαμηλή κατανάλωση ισχύος και η υψηλές

**Εικόνα 2:** Επισκόπηση των εργαλείων ανάπτυξης επεξεργαστών ASIP της Target που χρησιμοποιήθηκαν για αυτή την εργασία

επιδόσεις από μόνες τους δεν είναι αρκετές, καθώς αυτά τα δύο πολλές φορές έρχονται σε αντίθεση. Ένας επεξεργαστής που σχεδιάζεται για χαμηλή κατανάλωση συχνά δεν έχει καλές επιδόσεις ή αναγκάζεται να λειτουργεί σε χαμηλή συχνότητα, με αποτέλεσμα να χρειάζεται περισσότερη ενέργεια για να ολοκληρωθεί μία εργασία. Άρα, ένας σχεδιαστής επεξεργαστών πρέπει να κάνει ένα συμβιβασμό και να κρατήσει μία ισορροπία ανάμεσα στην ισχύ και την επίδοση, ανάλογα με την εφαρμογή για την οποία προορίζεται. Ευτυχώς, στους επεξεργαστές ASIP, είναι εύκολο και γρήγορο να γίνουν αλλαγές που αλλάζουν αυτές τις ισορροπίες.

Υπάρχουν διάφορες τεχνικές για να μειωθεί η κατανάλωση ισχύος, και οι οποίες μπορούν να εφαρμοστούν σε διαφορετικά επίπεδα της σχεδίασης (επίπεδο μεταγλωττιστή, αρχιτεκτονικής ή κυκλωμάτων), όπως δυναμική κλιμάκωση τάσης DVS - Dynamic Voltage Scaling, clock gating, ή κωδικοποίηση δεδομένων. Κάθε μία από αυτές έχει τα δικά τις πλεονεκτήματα και είναι στη διάθεση του σχεδιαστή να επιλέξει ποια αυτές να χρησιμοποιήσει.

Συνήθως θεωρείται δεδομένο ότι όσο πιο μικρή η μνήμη που χρησιμοποιεί ένας επεξεργαστής, τόσο καλύτερα. Αλλά αυτό που παραβλέπεται είναι η επιβάρυνση που έχει η χρήση της μικρής μνήμης στα υπόλοιπα μέρη του σχεδίου. Για ακριβώς αυτό το λόγο, διερευνάται σε αυτή την εργασία το κατά πόσο μία μεγαλύτερου μήκους λέξη εντολής μπορεί να αποδώσει καλύτερα για το σύνολο του συστήματος, παρά το επιπλέον κόστος στη μνήμη, καθώς αυτή θα επέτρεπε στον σχεδιαστή να χρησιμοποιήσει τα επιπλέον διαθέσιμα ψηφία της λέξης εντολής για να προσαρμόσει το σύνολο εντολών ακριβώς στην εφαρμογή για την οποία προορίζεται ο επεξεργαστής και κατόπιν να επανακωδικοποιηθεί με πιο αποτελεσματικό τρόπο.

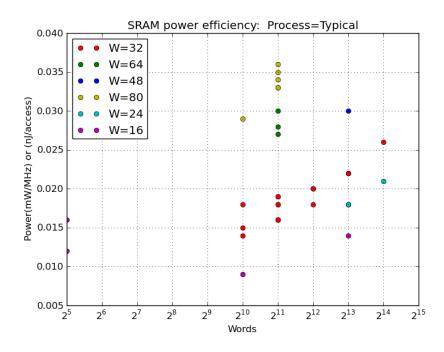

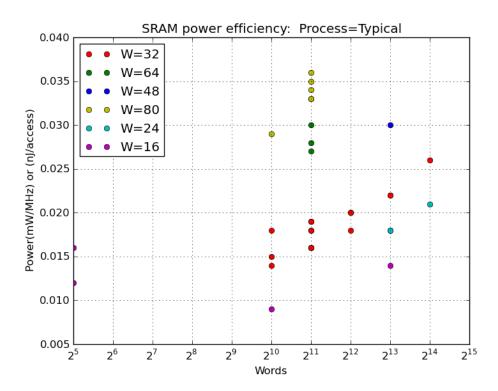

Μελέτες σε διάφορες σύγχρονες εμπορικές SRAM μνήμες δείχνουν ότι παρότι οι μεγαλύτεροι πίνακες μνημών (που αποτελούνται από άλλους μικρότερους υποπίνακες) τείνουν να προσφέρουν περισσότερο αποθηκευτικό χώρο για την περιοχή που διεκδικούν στο ολοκληρωμένο, η κατανάλωση ισχύος (αναφορικά με την συχνότητα λειτουργίας) τείνει να αυξάνεται με ταχύτερους ρυθμούς όσο το μέγεθος της λέξης αποθήκευσης ή ο συνολικός χώρος αποθήκευσης αυξάνεται (εικόνα 3). Αυτό συνεπάγεται ότι ενώ οι μικρότερες μνήμες είναι καλύτερες σε κατανάλωση ισχύος, οι μεγαλύτερες μνήμες μπορούν να προσφέρουν πολύ περισσότερο αποθηκευτικό χώρο για αναλογικά λιγότερη απαιτούμενο χώρο στο ολοκληρωμένο, το οποίο με τη σειρά του έχει άμεση επίδραση στην κατανάλωση ενέργειας. Η καλύτερη λύση είναι μία ενδιάμεση τιμή μεγέθους λέξης και μεγέθους μνήμης που εγγυάται υπεραρκετό αποθηκευτικό χώρο (ειδικά για τη μνήμη των εντολών εκτέλεσης) με αναλογικά μικρότερο ενεργειακό κόστος.

**Εικόνα 3:** Μέση κατανάλωση ενέργειας με διαφορετικό μέγεθος λέξης και μνήμης για εμπορικές SRAM

Η αρχιτεκτονική του συνόλου εντολών είναι ένα από τα κυριότερα και πιο καθοριστικά χαρακτηριστικά ενός επεξεργαστή. Αυτό ισχύει και για τους επεξεργαστές ASIP, όπου τα εργαλεία λογισμικού του παράλληλου σχεδιασμού υλικού και λογισμικού (hardware/software co-design) πρέπει να προσαρμοστούν σε αυτό το σύνολο εντολών και να το υποστηρίξουν.

Μία από τις πιο σημαντικές αρχιτεκτονικές επεξεργαστών είναι οι αρχιτεκτονικές SIMD (Single Instruction Multiple Data). Αυτές επιτρέπουν την καλύτερη αξιοποίηση παράλληλων εντολών εκτέλεσης (instruction-level parallelism). Υπάρχουν διάφορες προσεγγίσεις για την υλοποίηση μίας τέτοιας αρχιτεκτονικής,

με κυριότερες την υλοποίηση της σε υλικό (hardware SIMD) ή λογισμικό (software SIMD). Η αρχιτεκτονική hard-SIMD στηρίζεται σε πολλαπλές μονάδες εκτέλεσης στο υλικό ενώ η soft-SIMD μεταφέρει αυτήν την πολυπλοκότητα στον μεταγλωττιστή του κώδικα εκτέλεσης και τον αποκωδικοποιητή του συνόλου εντολών.

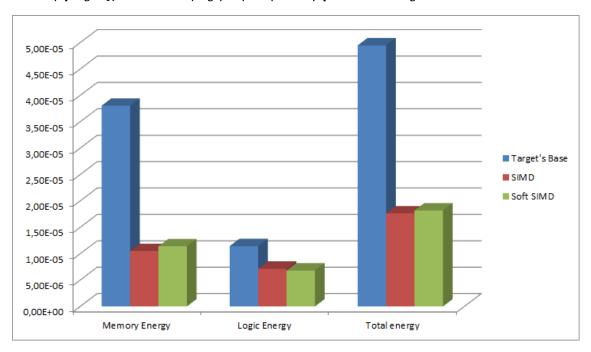

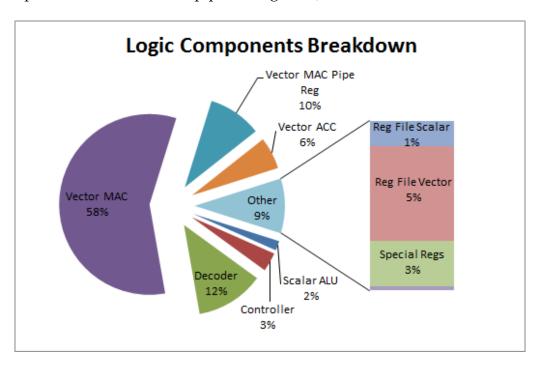

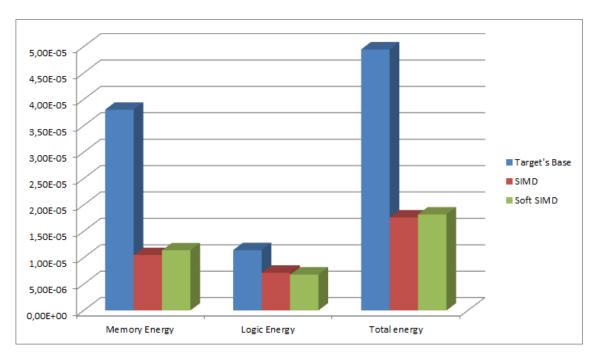

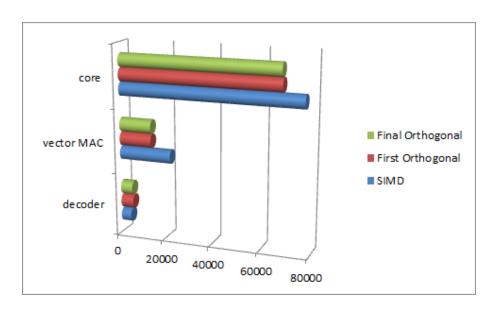

Κατά τη διάρκεια αυτής της διπλωματικής αναπτύχθηκε ένας επεξεργαστής ASIP με αρχιτεκτονική hard-SIMD ο οποίος και συγκρίθηκε με έναν απλό επεξεργαστή και έναν soft-SIMD με σκοπό να διερευνηθούν οι επιδόσεις σε ενέργεια και απαιτούμενο χώρο σε ολοκληρωμένο. Σαν εφαρμογή ελέγχου της επίδοσης χρησιμοποιείται μία βιοϊατρική εφαρμογή βασισμένη σε ένα Γκαουσιανό φίλτρο. Τα αποτελέσματα δείχνουν ότι και οι δύο υλοποιήσεις επεξεργαστών SIMD έχουν σαφώς καλύτερες επιδόσεις από τον απλό επεξεργαστή (εικόνα 4). Εφόσον μπορούν να εκτελέσουν την εφαρμογή πιο γρήγορα με μικρότερο αναλογία κατανάλωσης ισχύος και συχνότητας λειτουργίας, έχουν και σαφώς μικρότερο ενεργειακό κόστος.

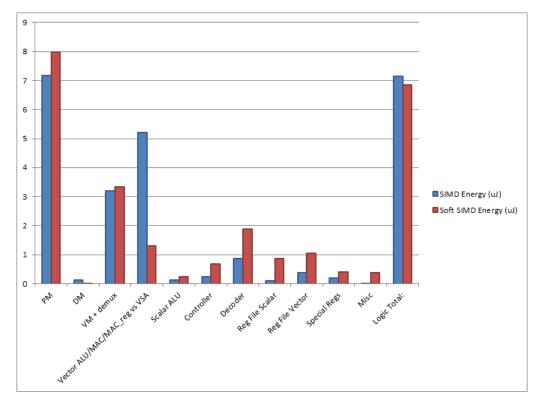

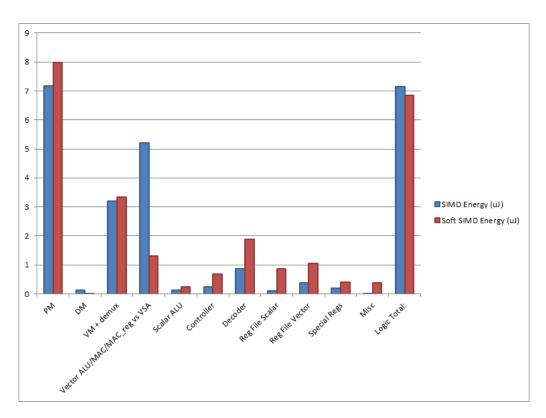

**Εικόνα 4** Συγκρίσεις για τις καταναλώσεις ενέργειας για τις μνήμες, τα μέρη λογικής και συνολικά για τις τρεις διαφορετικές αρχιτεκτονικές

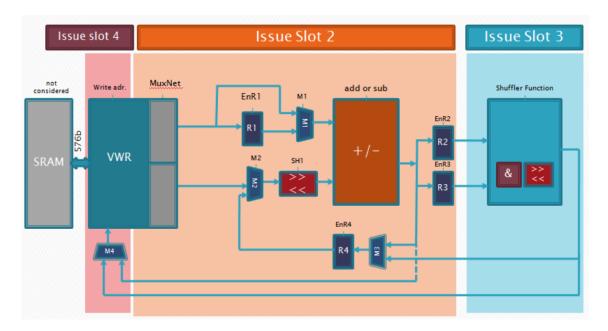

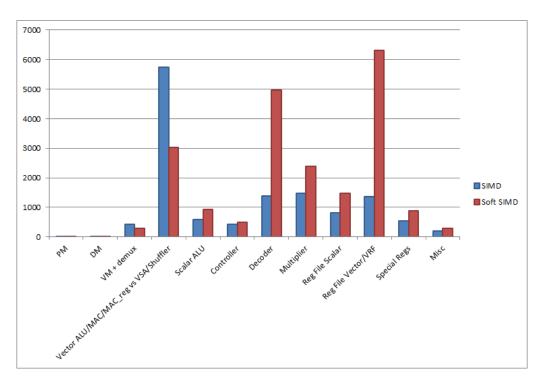

Η σύγκριση μεταξύ των δύο υλοποιήσεων hard-SIMD και soft-SIMD είναι κάπως δύσκολη, καθώς διαφέρουν σε πολλά σημεία, αλλά επικεντρώνεται στην κατανάλωση ενέργειας γιατί αυτό είναι το σημείο που μας ενδιαφέρει περισσότερο. Η αρχιτεκτονική hard-SIMD απαιτεί λίγο μικρότερο ποσό ενέργειας για την βιοϊατρική εφαρμογή, με μικρότερη περιοχή απαιτούμενων κελιών στο ολοκληρωμένο. Υλοποιεί στο υλικό της τέσσερις πολλαπλασιαστές των 16 ψηφίων για τον υπολογισμό των λειτουργιών που χρειάζεται η μονάδα MAC (Multiply-Accumulate), οι οποίοι είναι πολύ απαιτητικοί τόσο σε χώρο στο ολοκληρωμένο όσο και σε ισχύ. Παρόλα αυτά έχει ένα συνολικά σχετικά απλό σχεδιασμό. Η αρχιτεκτονική soft-SIMD έχει αρκετές πολύπλοκες βελτιστοποιήσεις με κυριότερες ένα εξελιγμένο αρχείο

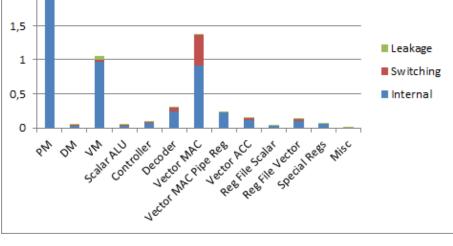

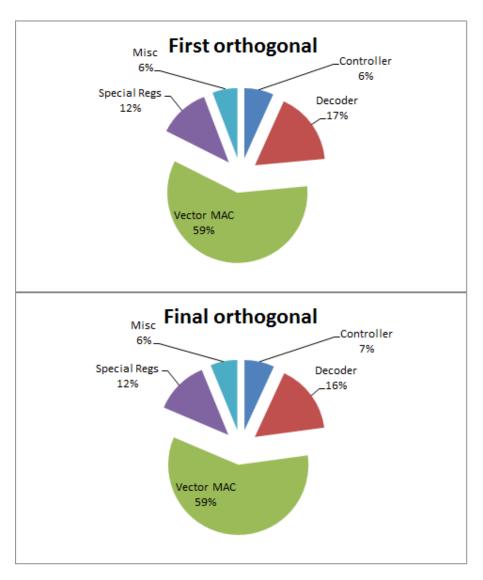

καταχωρητών για αποθήκευση διανυσματικών δεδομένων (Vector Vegister File), μία μονάδα επεξεργασίας διανυσματικών δεδομένων μέσω επαναληπτικών ολισθήσεων και προσθέσεων (vector shift-add unit) που υποκαθιστά τους πολλαπλασιαστές ΜΑΟ και λέξη εντολής μήκους 80 ψηφίων που μπορεί να προσαρμοστεί σε διαφορετικά μεγέθη υπολέξεων. Μελετώντας τα αποτελέσματα μετρήσεων ενέργειας για τα διάφορα μέρη της κάθε αρχιτεκτονικής (εικόνα 5), είναι εμφανές ότι η πολυπλοκότητα που επιβάλλουν οι προσθήκες της αρχιτεκτονικής soft-SIMD στα υπόλοιπα μέρη του επεξεργαστή και κυρίως στον αποκωδικοποιητή εντολών (ο οποίος πρέπει να αποκωδικοποιήσει μία πολύ μεγάλη λέξη εντολής των 80 ψηφίων) τα επιβαρύνει πάρα πολύ με αποτέλεσμα να αυξάνεται δραματικά η απαίτηση σε χώρο και κατανάλωση ισχύος. Από αυτά συμπεραίνουμε ότι καθαρά από την οπτική πλευρά της κατανάλωσης ενέργειας, η αρχιτεκτονική hard-SIMD με τον πιο απλό και ξεκάθαρο σχεδιασμό της που εξυπηρετεί στην γρήγορη ανάπτυξη και αποσφαλμάτωση του επεξεργαστή και παρέχει πολύτιμο χώρο για βελτιώσεις στην σχεδίαση και κυρίως κωδικοποίηση του συνόλου εντολών μέσω πειραματικών βελτιστοποιήσεων, κάτι που αξιοποιεί πλήρως τις δυνατότητες των εργαλείων ανάπτυξης επεξεργαστών ASIP.

**Εικόνα 5:** Συγκρίσεις κατανάλωσης ενέργειας μεταξύ των διαφορετικών τμημάτων των αρχιτεκτονικών hard-SIMD και soft-SIMD

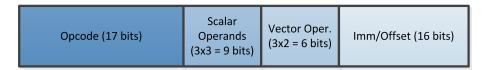

Η αρχιτεκτονική hard-SIMD κατόπιν μετατράπηκε σε αρχιτεκτονική με ορθογώνιο σύνολο εντολών, και το μήκος της λέξης εντολής από 16 ψηφία έγινε 48. Η αρχική ιδέα ήταν να γίνει η αρχιτεκτονική του συνόλου εντολών όσο γίνεται

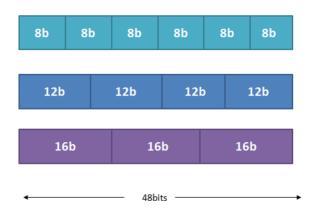

μεγαλύτερη και πλήρως ορθογώνια, δίνοντας έτσι τη δυνατότητα πλήρους ελέγχου στα παραγόμενα σήματα αλλά αυτό δεν κατέστη δυνατόν λόγω τον περιορισμένων δυνατοτήτων των τρεχόντων εκδόσεων των εργαλείων ανάπτυξης. Η νέα λέξη εντολών μήκους 48 ψηφίων (εικόνα 6) περιέχει 17 ψηφία για την επιλογή της εντολής και των παραμέτρων λειτουργίας της (opcode), 3\*3=9 ψηφία για τους τρεις απλούς τελεστές, 3\*2=6 ψηφία για τους διανυσματικούς τελεστές και 16 ψηφία για άμεση εισαγωγή τιμών(offset).

Η ορθογώνια αρχιτεκτονική συνόλου εντολών μήκους 48 ψηφίων

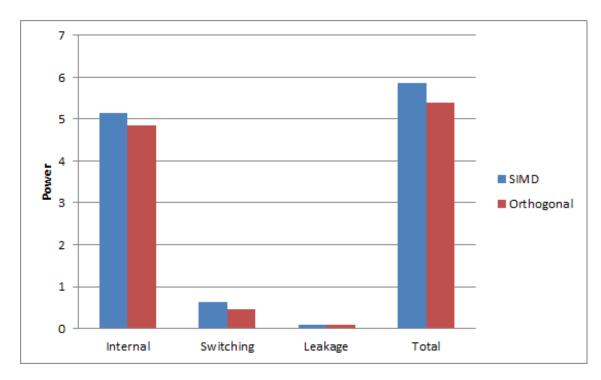

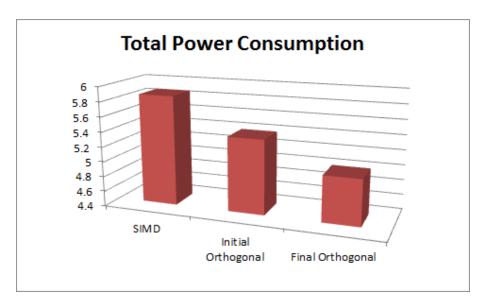

Η νέα ορθογώνια αρχιτεκτονική, παρά το τέσσερις φορές μεγαλύτερο μήκος λέξης εντολής και άρα και μέγεθος μνήμης εντολών προγράμματος είναι 10% πιο αποδοτικό ενεργειακά σε σχέση με την προηγούμενη αρχιτεκτονική (soft-SIMD), καθώς μειώνεται κατά πολύ η κατανάλωση ενέργειας του αποκωδικοποιητή εντολών, της μονάδας MAC και των άλλων τμημάτων.

Διεξήχθησαν διάφοροι πειραματισμοί για το πως θα μπορούσε να μειωθεί η πολυπλοκότητα του αποκωδικοποιητή μέσω της κωδικοποίησης του συνόλου εντολών. Αυτό πετυχαίνεται με τη χρήση των αρκετών ψηφίων στο μήκους 17 ψηφίων opcode που δεν χρησιμοποιούνται, με σκοπό να βελτιωθεί η γραμματική nML που περιγράφει το σύνολο εντολών και μέσω αυτής ο παραγόμενος κώδικας περιγραφής υλικού και να γίνει πειραματισμός με διαφορετικές μεθόδους κωδικοποίησης Τα εργαλεία ανάπτυξης ASIP παρέχουν επιλογές και μήκη λέξης εντολής. για παρακολούθηση της εκτέλεσης ενός προγράμματος και εξαγωγή στατιστικών στοιχείων, κυρίως για τα ποσοστά εκτέλεσης της κάθε εντολής. Αυτά τα στοιχεία, σε συνδυασμό με τη δυνατότητα γρήγορης παραγωγής νέου κώδικα περιγραφής υλικού που δίνουν τα εργαλεία ανάπτυξης ASIP, επιτρέπουν την εξερεύνηση διαφορετικών επιλογών χωρικής ή χρονικής τοπικότητας και των επιπτώσεων τους στην αρχιτεκτονική και την κατανάλωση ενέργειας που αυτή απαιτεί. Το μόνο πρόβλημα είναι ότι χρειάζεται ένας αυτοματοποιημένος τρόπος για να μπορεί γρήγορα μία νέα περιγραφή nML να περάσει από τα διάφορα στάδια μεταγλωττίσεων, προσομοιώσεων και επαληθεύσεων μέχρι την παραγωγή κώδικα περιγραφής υλικούς και καθώς την σύνθεση του με στοιχεία βιβλιοθηκών ολοκληρωμένων κυκλωμάτων και την εξαγωγή στοιχείων για την κατανάλωση ενέργειας και την μετατροπή αυτών σε φιλική και ευανάγνωστη για τον χρήστη μορφή. Αυτό λύνεται με τη χρήση διαφόρων σεναρίων εκτέλεσης (scripts) ή προγραμμάτων από διάφορες γλώσσες προγραμματισμού.

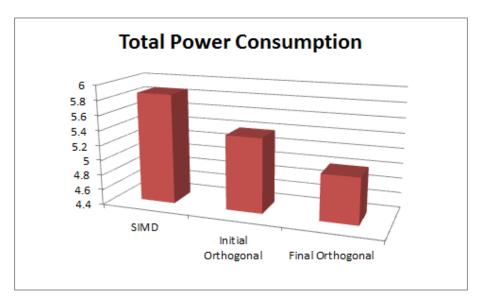

Η τελική υλοποίηση σαν αποτέλεσμα των προαναφερθέντων μεθόδων, διατηρεί τον βασικό περιορισμό ότι δεν πρέπει να γίνουν αλλαγές στην βασική λειτουργικότητα και το πλήθος των εντολών, γιατί παρόλο που αυτό θα έδινε πολλές παραπάνω δυνατότητες, ανοίγει τον 'ασκό του Αιόλου' για την πολυπλοκότητα

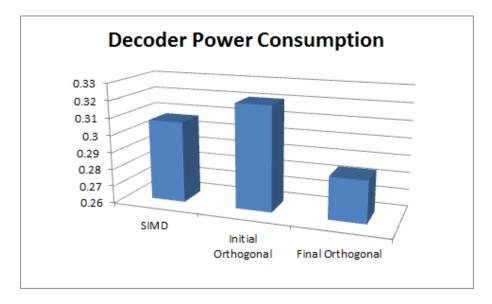

της αρχιτεκτονικής και των πειραματισμών. Μέσω της χρήσης διαφορετικής κωδικοποίησης για τις εντολές που ανήκουν σε βρόγχους επαναλήψεων που εκτελούνται πάνω από το 95% στο σύνολο των εντολών, και των βελτιστοποιήσεων της κωδικοποίησης τους τόσο συνολικά όσο και μεταξύ τους, προκύπτει ότι υπάρχει τεράστια μείωση στην δραστηριότητα αλλαγής ψηφίων (toggling activity) του αποκωδικοποιητή εντολών των μνημών, τα οποία με τη σειρά τους βελτιώνουν την συνολική κατανάλωση ενέργειας κατά 8% σε σύγκριση με την αρχική ορθογώνια αρχιτεκτονική και 15% σε σύγκριση με την αρχιτεκτονική SIMD (εικόνα 7).

**Εικόνα 7:** Συνολική κατανάλωση ενέργειας την αρχιτεκτονική SIMD, την αρχική και την βελτιστοποιημένη αρχιτεκτονική ορθογώνιου συνόλου εντολών

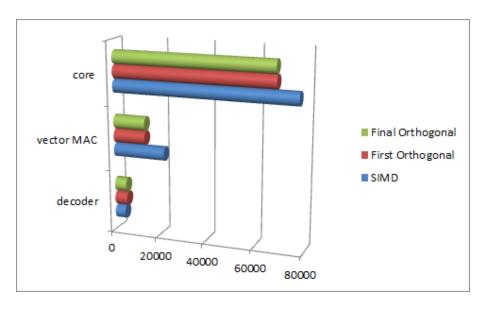

Είναι προφανές ότι η κωδικοποίηση του συνόλου εντολών και του μήκους λέξης εντολής αποτελεί ένα σημαντικό παράγοντα στην ενέργεια και τις επιδόσεις ενός επεξεργαστή. Με την χρήση των εργαλείων σχεδίασης ASIP και των δυνατοτήτων γρήγορου επανασχεδιαμού που μας παρέχουν μπορούμε να προσαρμόσουμε το σύνολο εντολών στην εφαρμογή για την οποία προορίζεται, με αποτέλεσμα να μειώνεται δραστικά η κατανάλωση ενέργειας χωρίς απώλεια στις επιδόσεις. Το μήκος της λέξης εντολών ορίζει τη σχέση μεταξύ της πολυπλοκότητας των μνημών και της συνολικής αρχιτεκτονικής (μέσω του αποκωδικοποιητή εντολών) (εικόνα 8). Μία μικρότερου μήκους λέξη εντολής χρειάζεται μικρότερη μνήμη και μεταφέρει την πολυπλοκότητα στον αποκωδικοποιητή εντολών, ενώ μία μεγαλύτερη λέξη εντολής προϋποθέτει έναν απλούστερο αποκωδικοποιητή αλλά μεγάλες μνήμες. Όμως, μερικές φορές και ανάλογα το πεδίο εφαρμογών η μείωση της δραστηριότητας toggling των εντολών είναι πιο σημαντική από από το μήκος τους.

Συνδυάζοντας τα δεδομένα από τους πειραματισμούς στις διαφορετικές αρχιτεκτονικές ASIP με τα δεδομένα από τις μετρήσεις στις μνήμες, προκύπτει το συμπέρασμα ότι καθώς η ενέργεια είναι καθοριστικός παράγοντας στη σχεδίαση, ένας επεξεργαστής και κυρίως ένας επεξεργαστής ASIP μπορεί να ωφεληθεί πάρα

**Εικόνα 8:** Απαιτούμενος χώρος σε ολοκληρωμένο (σε χώρο κελιών) για την αρχιτεκτονική SIMD και τις δύο αρχιτεκτονικές με ορθογώνιο σύνολο εντολών

πολύ από ένα μεγαλύτερο σε μήκος λέξης και όχι υπερβολικά συμπιεσμένο σύνολο εντολών, το οποίο μπορεί να μειώσει την συνολική πολυπλοκότητα σε όλη τα επιμέρους τμήματα της αρχιτεκτονικής, άρα και την απαιτούμενη ενέργεια χώρο σε ολοκληρωμένο, και παρέχει τη δυνατότητα βελτιστοποιήσεων για συγκεκριμένες εφαρμογές χωρίς να επιβαρύνει πολύ τις μνήμες. Πάραυτα, η αύξηση του μήκους της λέξης εντολών πρέπει να γίνει ελεγχόμενα λόγω της εκθετικά αυξανόμενης κατανάλωσης ισχύος πάνω από το μήκος λέξης 64 ψηφίων. Είναι στην ευχέρεια του σχεδιαστή να επιλέξει το κατάλληλο μέγεθος λέξης εντολής για την κάθε περίπτωση.

## **Contents**

| Ac | kno   | wledgements                                                         | iii |

|----|-------|---------------------------------------------------------------------|-----|

| Ει | ιχαρι | ιστίες                                                              | V   |

| Al | stra  | ct                                                                  | vii |

| Eı | κτετο | ιμένη Περίληψη                                                      | ix  |

| 1  | Intr  | roduction                                                           | 1   |

|    | 1.1   | Motivation                                                          | 1   |

|    |       | 1.1.1 Embedded systems                                              | 1   |

|    |       | 1.1.2 Processor design and instruction set architecture             | 4   |

|    |       | 1.1.3 Application specific instruction-set processors               | 7   |

|    | 1.2   | Objectives                                                          | 10  |

|    | 1.3   | Thesis Outline                                                      | 11  |

| 2  | Bac   | kground and Related Work                                            | 13  |

|    | 2.1   | Ultra-low power processor design                                    | 13  |

|    |       | 2.1.1 Power dissipation                                             | 14  |

|    |       | 2.1.2 Energy or power focus                                         | 14  |

|    |       | 2.1.3 Low energy metrics                                            | 15  |

|    |       | 2.1.4 The deep sub-micron era                                       | 16  |

|    |       | 2.1.5 Performance to power consumption ratio in different processor |     |

|    |       | types                                                               | 16  |

|    | 2.2   | Memory efficiency                                                   | 18  |

|    |       | 2.2.1 SRAM                                                          | 18  |

|    |       | 2.2.2 Memory power efficiency                                       | 18  |

|    |       | 2.2.3 Memory addressing modes                                       | 20  |

|   |     | 2.2.4 Loopbuffers                                                         | 21       |

|---|-----|---------------------------------------------------------------------------|----------|

|   | 2.3 | Techniques for energy-efficient processors                                | 21       |

|   |     | 2.3.1 Low-power techniques in circuit design                              | 22       |

|   |     | 2.3.2 Low-power techniques in architecture level                          | 25       |

|   | 2.4 | Code compression and encoding $\ldots \ldots \ldots \ldots \ldots \ldots$ | 29       |

|   | 2.5 | Architecture Description Languages                                        | 34       |

|   | 2.6 | Design methodologies for ASIP                                             | 34       |

|   |     | 2.6.1 Target IP Designer                                                  | 36       |

|   |     | 2.6.2 Tensilica's Xtensa                                                  | 36       |

|   |     | 2.6.3 LISA and Synopsys Processor Designer                                | 36       |

|   | 2.7 | ASIP Case studies                                                         | 37       |

| 3 | Dev | elopment Framework                                                        | 41       |

| • |     | nML Grammar                                                               |          |

|   | 0.1 | 3.1.1 nML Structural Skeleton                                             |          |

|   |     | 3.1.2 nML Rule Definition                                                 |          |

|   |     | 3.1.3 Primitives definition and generation language                       |          |

|   | 3.2 | Target tool flow                                                          |          |

|   |     | 3.2.1 Chess                                                               |          |

|   |     | 3.2.2 Checkers                                                            |          |

|   |     | 3.2.3 Go                                                                  | 44       |

|   |     | 3.2.4 Risk                                                                | 45       |

|   | 3.3 | Instuction set encoding                                                   | 45       |

| _ | _   |                                                                           |          |

| 4 |     | elopment of a SIMD ASIP                                                   | 47       |

|   |     | Hardware SIMD and Software SIMD                                           | 47       |

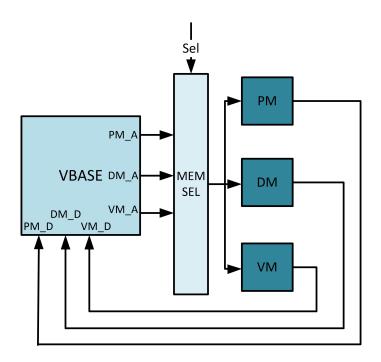

|   |     | Basic features of the VBase processor                                     | 49       |

|   |     | Additions and modifications                                               | 49       |

|   |     | Gauss loop filtering                                                      | 50       |

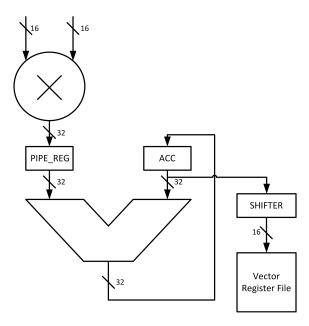

|   | 4.5 | Multiply-accumulate unit                                                  | 51       |

|   |     | 4.5.1 Shifter and overflow prevention                                     | 52       |

|   |     | 4.5.2 Wrapper and Testbench                                               | 53       |

|   | 4.0 | 4.5.3 Additional instructions added                                       | 53<br>54 |

|   | 4.6 | Comparison of the hard-SIMD with a soft-SIMD implementations              | 54       |

|   |     | 4.6.1 The Soft-SIMD implementation                                        | 54       |

|   |      | 4.6.2 Comparison and results                                                       | 56 |

|---|------|------------------------------------------------------------------------------------|----|

| 5 | Mod  | lifying the Instruction Set for Energy-Efficiency                                  | 63 |

|   | 5.1  | Analysing the generated control signals for full orthogonality $\ \ \ldots \ \ \ $ | 63 |

|   | 5.2  | Creating a wider instruction                                                       | 65 |

|   |      | 5.2.1 Power Results                                                                | 66 |

|   |      | 5.2.2 Area Results                                                                 | 66 |

|   | 5.3  | Optimizing the encoding of the instruction set                                     | 67 |

|   |      | 5.3.1 Reducing decoder complexity                                                  | 67 |

|   |      | 5.3.2 Exploiting methods for energy efficient architectural design with ASIP tools | 70 |

|   | 5.4  | Final implementation                                                               |    |

|   |      | 5.4.1 Final results                                                                | 72 |

|   |      | 5.4.2 Conclusions                                                                  | 74 |

| 6 | Con  | clusions                                                                           | 77 |

|   | 6.1  | The quest for the golden ratio                                                     | 77 |

|   | 6.2  | Memory efficiency                                                                  | 78 |

|   | 6.3  | ASIP instruction-set architecture                                                  | 78 |

|   |      | 6.3.1 Hard-SIMD and Soft-SIMD                                                      | 79 |

|   |      | 6.3.2 Orthogonality and optimal word size                                          | 79 |

|   | 6.4  | Future work                                                                        | 81 |

|   | Bibl | liography                                                                          | 82 |

# **List of Figures**

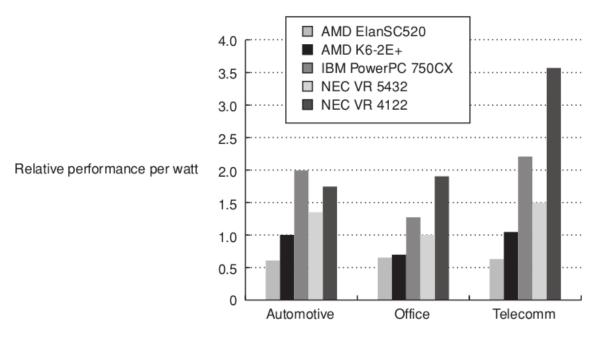

| 1.1  | Relative performance per watt for five embedded processors [Henn06].                                                                                                                              | 3  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

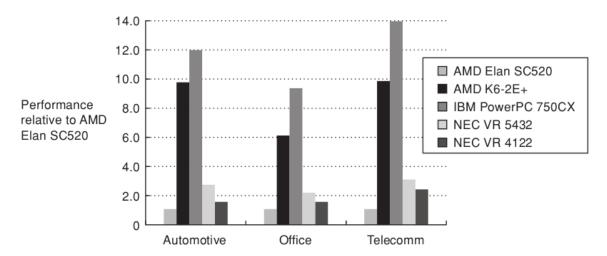

| 1.2  | Raw performance for five embedded processors, The performance is presented as relative to that of the AMD ElanSC520 [Henn06]                                                                      | 4  |

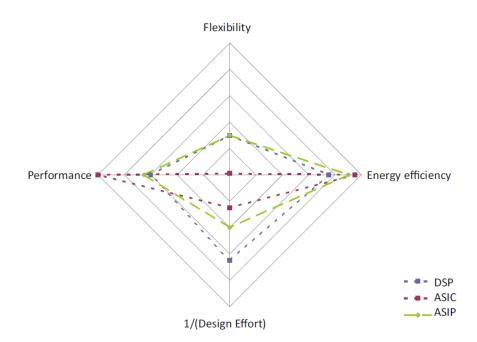

| 1.3  | Different design styles target different design metrics [Catth10]                                                                                                                                 | 7  |

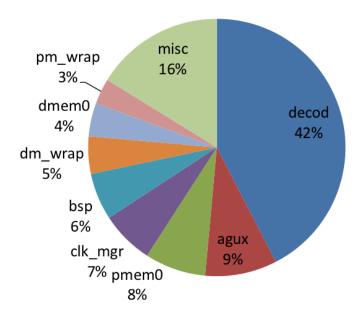

| 1.4  | Power consumption for different components of CoolBio executing ECG v1.0 code $\dots \dots \dots$ | 8  |

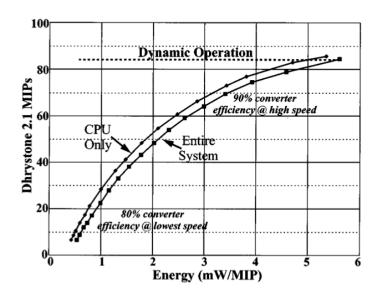

| 1.5  | Average power and performance depending on the level of code optimization for a commercial ASIP                                                                                                   | 9  |

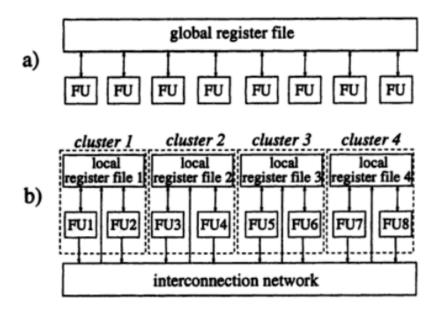

| 1.6  | VLIW data paths: a) orthogonal b) clustered [Leup00]                                                                                                                                              | 10 |

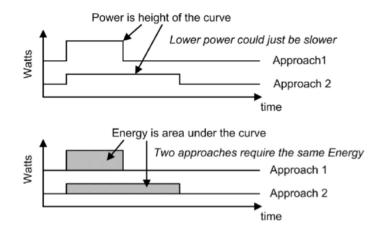

| 2.1  | Power versus energy [Keat07]                                                                                                                                                                      | 15 |

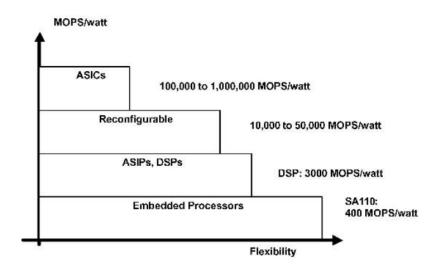

| 2.2  | MOPS/watt versus flexibility [Piguet06]                                                                                                                                                           | 17 |

| 2.3  | A typical SRAM cell composed of 6 transistors (6T)[Westell]                                                                                                                                       | 18 |

| 2.4  | SRAM area needed for different block sizes[Katev11]                                                                                                                                               | 19 |

| 2.5  | SRAM Power consumption for different block sizes[Katev11]                                                                                                                                         | 20 |

| 2.6  | Power consumption for different word and block sizes in commercial SRAM memories                                                                                                                  | 21 |

| 2.7  | Measured throughput versus energy consumption [Burd00]                                                                                                                                            | 23 |

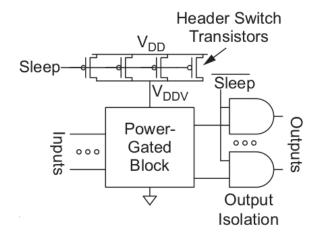

| 2.8  | Power gating [Westell]                                                                                                                                                                            | 24 |

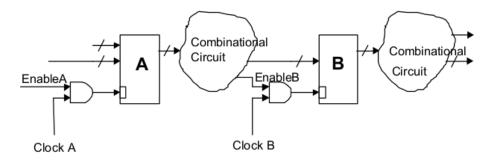

| 2.9  | Latch-based clock gating [Piguet06]                                                                                                                                                               | 26 |

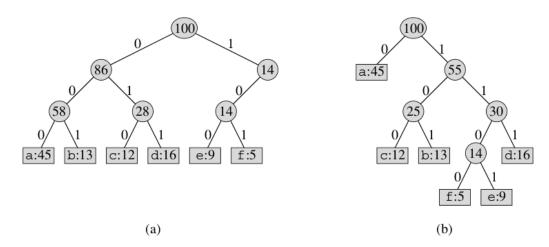

| 2.10 | OTrees showing the initial data and the results of a simple Huffman coding. [CormeO1]                                                                                                             | 31 |

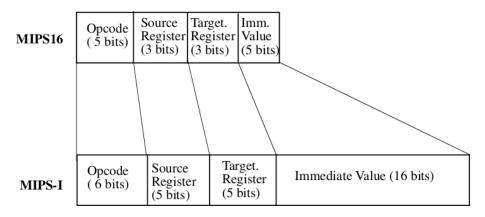

| 2.11 | Mapping of MIPS16 compressed instructions [Kiss97]                                                                                                                                                | 33 |

| 2.12 | ASIP hardware/software co-design flow [Liu08]                                                                                                                                                     | 35 |

| 2.13 | 3Different design styles target different design metrics [Morg07]                                                                                                                                 | 37 |

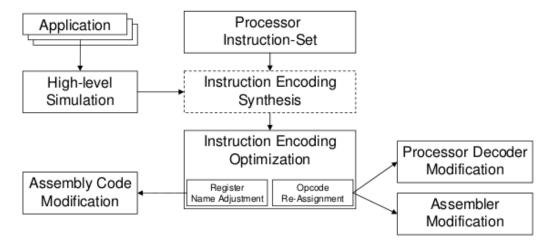

| 2.14 | Overall encoding synthesis flow [Zhang08]                                                                                                                                                         | 38 |

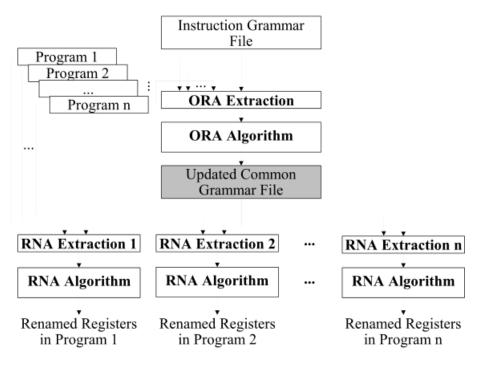

| 2.15 | Multiple assembly programs optimization flow [Zhang08]                                                                                                                                            | 40 |

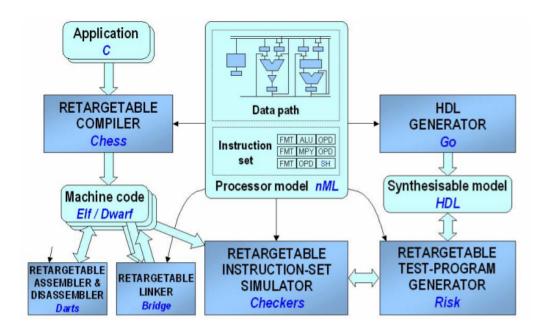

| 3.1  | Outline of Target's Chess/Checkers tool suite flow                                                                  | 42 |

|------|---------------------------------------------------------------------------------------------------------------------|----|

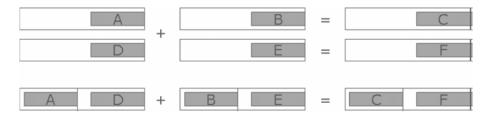

| 4.1  | SIMD data packing                                                                                                   | 48 |

| 4.2  | Application of Gauss filter through a coefficient square matrix [Psy10]                                             | 50 |

| 4.3  | The basic MAC unit introduced                                                                                       | 51 |

| 4.4  | The wrapper outline                                                                                                 | 53 |

| 4.5  | Soft-SIMD sub-words [Dak11]                                                                                         | 55 |

| 4.6  | Soft-SIMD processor architecture [Dak11]                                                                            | 56 |

| 4.7  | $Hard\mbox{-SIMD power consumption percentage in login components}  .  .$                                           | 57 |

| 4.8  | Hard-SIMD power type per component                                                                                  | 58 |

| 4.9  | Target's Base, Hard-SIMD and Soft-SIMD memory, logic and total energy consumption comparisons                       | 60 |

| 4.10 | Hard-SIMD and Soft-SIMD area comparison per component                                                               | 61 |

| 4.11 | Hard-SIMD and Soft-SIMD energy comparison per component                                                             | 62 |

| 5.1  | A very wide instruction word divided in different parts, each one containing the control bits for a functional unit | 64 |

| 5.2  | The 48-bit orthogonal instruction set                                                                               | 66 |

| 5.3  | Comparison of the average power consumption in uW of the original SIMD (blue) and the orthogonal version (red)      | 67 |

| 5.4  | Decoder component power consumption of the SIMD, first and final orthogonal implementations                         | 72 |

| 5.5  | Total power consumption of the SIMD, first and final orthogonal implementations                                     | 73 |

| 5.6  | Power consumption for every component in the two orthogonal implementations                                         | 75 |

| 5.7  | Cell area required for the SIMD and the two orthogonal                                                              | 76 |

## **List of Tables**

| 2.1 | Power reduction techniques [Piguet06]                            | 22 |

|-----|------------------------------------------------------------------|----|

| 4.1 | Target's Base cycle count, area, power and energy needed for the |    |

|     | same filter application                                          | 59 |

## Chapter 1

### Introduction

#### 1.1 Motivation

Embedded systems have developed a lot the last decade, with a main research focus on improving performance and cost and secondary on improving power, flexibility or reliability. However, the same principles do not apply on the market anymore. Nowadays, one of the features that has come to pose a big problem is that of power and energy consumption. By rapidly increasing the performance, we have increased the energy consumption of the system at an even greater rate. Application Specific Instruction-set Processors were developed and introduced to SoC design for their unique feature to combine performance, flexibility and power efficiency. There has been a lot of work in the field of performance, but in the field of power there is still a lot of space for improvement.

The motivational framework for this study is summarized in the following sections, including an introduction to embedded systems, processors and especially ASIPs that provides the reader with essential information for the next chapters

#### 1.1.1 Embedded systems

Embedded computer systems are computers inside devices designed to perform certain functions and are one of the most rapidly growing part of the computer industry. These devices are everyday machines excluding laptops, desktops or servers (which are by comparison general purpose) and they range from mobile phones, hand-held digital devices or video consoles to cars and washing machines. Their purpose is to perform a specific task as efficiently as possible (perceived by the common user as "fast" or "responsive") while providing a certain autonomy on battery or generally low power consumption. They are usually programmed to perform just a handful of functions or programmable but within small limits. The

parts of the code that are used most often are heavily optimized. More complicated systems come with firmware which can be updated for bug corrections or added functionality. That is how they manage to uphold time-to-market deadlines and reduce the cost.

Compared to desktops, embedded systems differ in a lot of ways. They have a much broader range of technical characteristics since each one is developed for a precise function, from low-end and cheap 8-bit or 16-bit embedded microprocessors to way high-end, efficient and expensive embedded microprocessors that provide greater functionality and maximum performance. Also, unlike desktops, each embedded system is developed with predefined criteria, usually in performance, area, responsiveness, or energy consumption, with more narrow limits.

Embedded systems are also used for *real-time systems* where they are programmed to meet specific real-time constraints, meaning that the time from certain events until the proper response of the system cannot exceed a set time limit. Those real-time systems can be either soft or hard. In hard real-time systems (e.g. in planes), failing to keep up to the deadline results in a complete system failure, so the design and standards of those systems are far more strict, or soft real-time systems where a few failures are tolerated but they reduce the quality of service.

Typically, the purpose of an embedded system is to process information in the form of signals, so one of the most common embedded systems are digital signal processors (DSPs). The term "signal" does not necessarily denote a telecommunication transmission, but it could also be a video, an image, a sound or any form of data. DSPs are specialized processors optimized for for digital signal processing algorithms. These algorithms are from many domains, from transforms (e.g. Discrete Cosine Transform, Fast Fourier Transform), timedomain filtering (e.g. finite impulse response or infinite impulse response filters) or convolution to error correction. But in all those the core unit is common: the multiply-accumulate operation. A characteristic example is the Finite Impulse Response (FIR) filter:

$$Y[n] = \sum X[n-k]h[h]$$

where X[n] is the sampled input, h[k] are the filter coefficients that characterize the particular filter and Y[n] is the output.

As indicated above, the filter is composed of registers, multipliers and an adder, therefore the core that is repeated is comprised of subsequent additions of a product. For the DSP to be effective, this core has a dedicated hardware unit to perform the multiply-accumulate operation (MAC). So a MAC instruction of "MAC A,B,C" actually implies "A = A + B \* C". There has been a lot of research in trying to optimize the MAC unit, because in many cases that is where the bottleneck of the whole system lies. Another common way used to accelerate communication

1.1. Motivation 3

algorithms is by optimizing encoding and decoding forward error correction codes.

#### Performance versus power consumption

In contrast with the desktop/server market, in the embedded market power consumption and production cost play a much greater role. Desktop and server systems have a stable power supply whereas most embedded systems rely on battery supply. Therefore, embedded systems compared to desktop ones are not only constrained in terms of cost, physical area and memory size but also in energy consumption. As a result the designers have to measure carefully the metrics of their system, weighting performance against energy consumption. For example, it would be inefficient to produce an embedded system that has great performance, but drains the battery really fast, or the other way around, one that has an excellent low power consumption but takes a really long time to perform its given task.

To measure effectively and accurately the performance and power consumption, specific benchmarks are used (like EEMBC). Figures 1.1 and 1.2 show the relative performance per watt of typical operating power and raw performance compared a specific processor respectively. From these two figures it is very interesting to notice certain points that stand out. For example, the NEC VR 4122 is probably the best one in terms of performance per watt, especially for the telecomm benchmark, but is second-last when it comes to raw performance. On the other hand the PowerPC has the best performance but is draining a lot of power that makes it unsuitable for battery-powered embedded systems.

Figure 1.1: Relative performance per watt for five embedded processors [Henn06].

**Figure 1.2:** Raw performance for five embedded processors, The performance is presented as relative to that of the AMD ElanSC520 [Henn06].

#### **Embedded multiprocessor systems**

Nowadays, mainly in servers but also in desktop systems, using multiprocessors is a common way to boost performance. Likewise in embedded systems, multiprocessors are used, with different special-purpose processors. This proves highly effective, since each specialized processor can handle efficiently specific functions. A prime example of an embedded multiprocessor is a modern mobile phone, equipped with one or more ARM cores, several DSPs and even more dedicated ASIC co-processors for specific tasks, like Viterbi decoding<sup>1</sup>.

There are also two reasons for the popularity of multiprocessors in the embedded space. The first one is that they make it easier to exploit the parallelism that already exists is many applications, by assigning parts of the code to different special-purpose processors. The second is that, as mentioned before, the parts that are most commonly used are optimized for each embedded processor, and that eliminates the problem of binary software compatibility that still troubles many desktop systems.

#### 1.1.2 Processor design and instruction set architecture

Processor designers today face a complex problem. When designing a processor, they have to determine which attributes are more important, and in general try to design a processor with as great performance as possible while at the same time keeping in line with the constraints in area, power and cost. As

<sup>&</sup>lt;sup>1</sup>Viterbi decoding uses the Viterbi algorithm to decode a bitstream that is encoded using forward error correction based on convolutional code. It is resource-consuming but does maximum likelihood decoding

1.1. Motivation 5

mentioned very precisely on [Catth10], processor design is a game of many tradeoffs, and the designer has to balance the attributes of the processor and many other aspects including instruction set architecture, organization, logic design and implementation. The implementation may include integrated circuit design, packaging, power and cooling. Optimizing the design requires familiarity with a wide range of technologies, from compilers and operating systems to logic design and packaging.

The *instruction set architecture (ISA)* is the most defining part of processor and what defines the communication between the hardware and the software. The main characteristics of an ISA[Henn06] are clearly defined as follows:

- 1. *Class of ISA* General or special purpose architecture. Register-memory or load-store oriented.

- 2. *Memory addressing* All desktop and server computers use byte addressing to access memory operands. Some ISAs also require that the data has to be aligned to be read and written correctly.

- 3. Addressing modes They specify registers, constant operands and the address of a memory object.

- 4. Types and sizes of operands Common examples for fixed-point are 8-bit(ASCII character), 16-bit(half-word or unicode character), 32-bit(word or integer) or 64-bit(double word) and for floating point 32-bit(single precision), 64-bit(double precision) or even 80-bit(extended double precision).

- 5. Operations Data transfer, arithmetic, logical, control etc.

- 6. *Control flow instructions* Conditional branches, unconditional jumps, procedure calls and returns.

- 7. *Encoding an ISA* Usually fixed length or variable length. More about this on chapter 3.3.

#### VLIW and vector processors

Very Long Instruction Word (VLIW) processors are multiple-issue processors that use many, independent functional units to exploit instruction-level parallelism (ILP). Instead of using multiple instructions for different units, VLIW processors have a single very long instruction word that contains multiple operation instructions, one for each of the functional units. Taking full advantage of a VLIW requires to focus on a wider-issue processor so as to maximize the issue rate. In order to fully utilize this architecture, the code generated by the compiler must contain enough parallelism to provide instructions to as many of the functional units as possible in each cycle. Modern compilers use code

transformation techniques like loop unrolling or scheduling techniques like local or global scheduling to detect and enhance the required parallelism.

Explicitly parallel instruction computing (EPIC) processors were introduced by HP and Intel to address and overcome some of the common problems of VLIW, mainly in flexibility, code size and improved software speculation. By using explicit indicators for possible instruction dependencies and multiple instruction formats instead of the fixed instruction format of VLIW and so is able to express parallelism more flexibly and reduce the size of the generated code.

Of course, nowadays there is also the choice of *vector processors* for some applications. Vector processors offer operations that can process a lot of data at the same time in special vector functional units, provided that those data are *vector* form, linear arrays of numbers. So vector processors can provide faster results at the same cost but only for specific applications in structured code that the vectorization can be applied. Otherwise, VLIW are preferred for their ability to extract parallelism from less structured code and adapt to all forms of application data.

One of the most common vector architectures used for both desktop and embedded systems is *Single Instruction Multiple Data(SIMD)*, as it was classified by Flynn's taxonomy. SIMD can exploit data-level parallelism, by applying the same operation to multiple data in parallel (vectorized data). It is most effective in applications that show great data-level parallelism, like high performance applications, graphics acceleration and many digital filters.

#### Orthogonal instruction set

Orthogonal instruction set is a term used in computer engineering to classify an instruction set architecture where any instruction can use data of any type through any addressing. The word orthogonal, meaning "right angle" in greek, is used in a similar way to geometry and mathematics and implies that the ISA provides the capability to move along the operations axis independently of the other addressing mode axis and vice versa, thus enabling all possible operation and addressing mode combinations but forcing a limited set of operational codes and addressing modes.

Many CISC based computers generally follow the orthogonal instruction set, by allowing an instruction to access either the register file or the main memory in several different ways. There are several fully orthogonal computer systems like PDP-11 and VAX-11 or others that are nearly orthogonal like DEC PDP-11 and Motorola 68000.

In RISC architectures, orthogonality is also used, but not full orthogonality because that would lead to a less efficient architecture, and several instruction bits are used instead for other purposes. So there is a trade-off that is usually made for each architecture between orthogonality and enabling other techniques 1.1. Motivation 7

like virtual addresses, longer immediate data or larger register files.

#### 1.1.3 Application specific instruction-set processors

Traditional ASICs (Application Specific Integrated Circuits) have great performance and low energy consumption but lack flexibility since they are designed and optimized to perform a specific task. DSPs (Digital Signal Processors) are flexible and their performance is very good but they are not energy efficient at all. And that is the reason why ASIPs are developed. They perform almost equally well and can also be energy efficient, but their strong point is their flexibility (fig:1.3). The design effort for mapping code on an ASIP is quite low, but still higher than that of an ASIC [Catth10]. Thankfully, there are many automated tools that can help in this and make it less of a challenge.

**Figure 1.3:** Different design styles target different design metrics [Catth10]

Application Specific Instruction-set Processors (ASIPs) are nowadays used increasingly in System-on-Chip design to design a programmable processor with an instruction-set tailored to fit the needs of a specific application domain. They bridge the architectural gap between general purpose processors and ASICs (Application Specific Integrated Circuits) combining the advantages of both "worlds". They are developed using a user-friendly processor description language called *Architecture Description Language (ADL)* (see 2.5), an efficient retargetable C compiler along with accurate simulation and profiling tools, and so considerably decrease the time needed to develop a new processor.

In the application domains of image and video processing, ASIPs can use a

combination of VLIW and SIMD along with powerful compilers and other tools and techniques to maximize efficiency and make optimal architectural trade-offs.

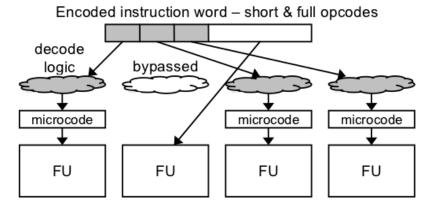

# Instruction word size against instruction decoder complexity for energy efficiency

Recent results on the power dissipation figures of various latest processor cores show an increasing percentage of the overall consumption is due to the instruction memory and the decoder. As seen both in the ultra-low power biomedical signal processor CoolBio of IMEC, Holst Centre and NXP and ICORE[Zhang08], the power consumption attributed to the decoder takes up 28-42% of the total consumption.

**Figure 1.4:** Power consumption for different components of CoolBio executing ECG v1.0 code

In commercial processors in the effort to increase their capabilities their instruction set contains not only a lot of instructions compared to the small instruction word, but also these instruction often are very complicated in their structure and addressing modes they have to support.

Concurrently, as noticed on latest commercial SRAM memories, doubling the size of the memory width does not incur an equal rise in power consumption. More about that on a later chapter.

As illustrated in figure 1.5, for a commercial ASIP the average power consumption and the performance required are included in the shaded area of the triangle. For different code optimization level there is also a different different performance required, meaning that better optimized code requires a lower operational frequency, that results to lower power consumption. This

1.1. Motivation 9

means that the average power drops while the mW/MHz for a task rises. If the instruction set is tailored for the functions then the code can be executed faster and more efficiently. Increasing the supply voltage would increase the power consumption and thus the lines of the triangle would rise in the Y axis, at a "steeper" angle. Leakage is omitted for now. Therefore, since bigger frequencies have a negative impact on power consumption and the aim is not simply a low power consumption but a smaller energy consumption per task. So instead of mW/MHz, using J/function is more a accurate metric for energy efficiency.

**Figure 1.5:** Average power and performance depending on the level of code optimization for a commercial ASIP

So it needs to be looked into whether the energy gains from having a longer, simpler and more orthogonal instruction set in an ASIP, or even a fully orthogonal VLIW processor (see fig.1.6) can compensate for the extra energy incurred by the bigger memories needed.

It also the purpose of this thesis to explore the capabilities of a commercial ASIP development tool, like the Target tool suite used for the development of several ASIP cores, investigate the limits of those capabilities and give suggestions for future additions that could be added. This study also looks into how the ASIP tools can be fully utilized to exploit the energy efficiency dynamics of a design for a specific application domain.

Figure 1.6: VLIW data paths: a) orthogonal b) clustered [Leup00]

## 1.2 Objectives

The main objectives of this thesis are the following:

- Investigate how different components and overall power consumption are affected by changes in the width of the instruction.

- Experiment with different encodings for the instruction set of an ASIP and notice their effect on the instruction decoder.

- Find the best trade-off between the width of the instruction and the memory size for low power consumption, considering that the former has a very strong impact on the instruction decoder.

- Benchmark and provide suggestions for improving and extending existing designs.

- Automate the whole procedure from designing an ASIP processor to generating the HDL and benchmarking its area and power performance and provide suggestions and feedback to Target

1.3. Thesis Outline

#### 1.3 Thesis Outline

The main body of this report is divided as follows.

Chap. 2 provides related work on the fields of ultra-low power processor design, code compression and encoding and ASIP methodology which are associated with this thesis as well as the background information and case studies that are needed to understand it.

Chap. 3 provides the development framework of Target tool flow, analyzing the way the nML grammar is used to describe an instruction set architecture and tools along with the basic options that they offer.

Chap. 4 includes the analysis and implementation of a SIMD processor and another soft-SIMD and the experimental results of their comparison to a scalar processor and to each other,

Chap. 5 deals with the basic implementation of an orthogonal processor and the various experiments conducted on it to achieve power efficiency. It also shows the results of all the implementations during this thesis.

Finally, Chap. 6 summarizes what's been achieved, provides the conclusions of this study, the open questions and what could be done next.

# Chapter 2

# **Background and Related Work**

The last fifteen years there has been a lot of work about ASIPs and various low-power design techniques. This chapter provides an insight to several state of the art approaches to problems and challenges in the field related to this thesis, but also slightly older ones that can be revisited.

## 2.1 Ultra-low power processor design

Having a an power efficient processor is of grave importance in most systems, but it is difficult goal to achieve because improving power consumption creates a contradiction with other main characteristics of the processor, like performance or flexibility. There are various techniques that can be used for efficient ultra-low power processor design [Piguet06], like CPI (cycles per instruction) reduction, gated-clock mechanisms, optimal pipeline length, hardware accelerators, reconfigurable units and techniques for reducing the leakage power. DSPs are a prime example that helps demonstrate the necessary tradeoff between flexibility and energy efficiency.

The two main constraints for SoC design are none other than power efficiency and computation power. When it comes to the portable consumer market, power efficiency is the defining constraint, particularly in deep submicron technologies, where designers are coming up against new problems, like very low supply voltages, high leakage, long wire delays, networks on chip, signal input slopes, noise and crosstalk effects.

The components that commonly take up a big part of the power pie are the memories. There are various well-known methods for reducing the power consumption of memories (more about that on chapter 2.2), but it should be still kept in mind that the power consumption of the processor itself can also be improved, and that it is the processor that defines the types and sizes of memories needed. But coming up with the "ideal" processor, meaning one that is flexible,

has great computational power and is also power efficient is virtually impossible. So there has to be a tradeoff between those three, and the best criterion for that would be to base them on the needs of the application of the processor.

#### 2.1.1 Power dissipation

In order to understand how low power techniques work, it is vital to have in mind the various factors that make up *power dissipation*.

Power dissipation is divided itself in *dynamic* and *static* components. Dynamic is attributed to the switching activity caused by temporary current paths (while pMOS or nMOS stacks are partially ON) and charging or discharging the capacitors as gates switch, so it is directly proportional to the switching frequency. The static component is the power dissipated due to static conductive paths between the supply rails or leakage currents, which is there even if there is no switching activity. *Leakage* can be either sub-threshold through OFF transistors, gate leakage through gate dielectric or junction leakage from source/drain diffusion.

A chip and thus power can be considered to be in one of three modes at any time: *active*, *standby* or *sleep*. Active is the power consumed while the chip is working, and is dominated by the switching power. Standby power is consumed while the chip is idle, so if the clocks are stopped it is mostly leakage power. Sleep power is consumed when various components are not needed for a certain time period and their power is turned off to drastically decrease the leakage. However there is an extra cost in energy and time needed to put a component to sleep or wake it up, therefore making this a viable solution only if the component is not going to be used for a long period.

#### 2.1.2 Energy or power focus

The term *power consumption* defines the amount of energy consumed per operation and the heat dissipation of a design, and those two in turn affect several other aspects of the design, like battery life, cooling, placement and packaging. Therefore, power dissipation plays an important part in the design.

Many times, the power characteristics of a chip are described with power for a set frequency, i.e. 10mW @ 1GHz. It is easy to calculate the energy but reporting an energy number makes things much more clear and helps avoid misunderstandings.

A common misunderstanding in embedded system design on whether a designer should aim for energy or power optimization, considering that the two are relative to each other (Energy = Power x Time). But as shown on figure 2.1, there is a distinct difference between energy and power, considering that power is the instantaneous power in the device but it is energy (the area under the curve

in the figure) that is truly important for portable systems and actually determines the duration of the battery.

In high performance systems, where the basic focus is performance, there is a consumption limit set by the technical characteristics of the chip and its cooling capabilities. However, in portable and embedded systems it is of great importance to keep a low *energy* limit, because the focus lies in the maximum number of computation in the time range between battery charges. So, in portable and embedded systems having a system with 50% less power consumption that is compelled to run on 50% its frequency (to keep the power consumption at low levels) leads to exactly the same energy, since the total energy consumed for the same task that runs on 50% "low-power" but takes twice the time to complete is still the same. So low power consumption by itself is clearly not enough.

**Figure 2.1:** Power versus energy [Keat07]

#### 2.1.3 Low energy metrics

In literature normally the power efficiency of processors is indicated with figures of merit like mW/MHz or pJ/cycle describing the energy cost of processor cycles. It is interesting to have a low number since that shows the low-power properties of a processor core. It shows the power dissipation at a predetermined clock frequency. Using this figure of merit disguises however the more important aspects of processors for wireless sensor nodes (and other battery-operated) devices. The amount of energy to do a certain job is a more important metric. What really needs to be optimized is the amount of energy a task consumes. Therefore, an important figure of merit would be Joule per task, irrespective of the number of clock cycles (or clock frequency) a processor core needs.

Another popular way to calculate the performance to power consumption ratio is in MIPS/w (Million Instruction per Second per Watt) or w/MIPS respectively. Using this figure it is relatively easy to estimate the energy consumption for a given application or task.

A very important motivation that explains the reason why DSPs and ASIPs were introduced is due to the large variation in instruction sets. Processors with large data paths typically need less cycles to complete a task, at a higher J/cycle cost, but typically consuming less energy for the job. For low energy design this also is beneficial.

Processor optimization often leads to complicating the instruction set extensively to keep it small. However the introduced overhead in instruction decoding can potentially lead to increased area and energy.

#### 2.1.4 The deep sub-micron era

Technology is advancing rapidly, and that has a strong impact on the relative merits of different circuit techniques, and ultimately the way designers handle them, with regard to the future. For example, gate delays are improving way more rapidly than the delays of the interconnecting wiring, and threshold drops are becoming more dominant of the supply voltage. Also leakage is increasing. A designer needs to be aware of impending changes like these to ensure the continuity of his creations.

With the increasing complexity of the digital integrated circuits, it is anticipated that in future smaller scale technologies the problem of energy consumption will only get worse. Lower supply voltages are becoming more attractive, because reducing  $V_{DD}$  has a quadratic effect on the dynamic power consumption, assuming the same clock rate is sustained.

Many nanometer processes have now reached a point where it is no longer possible to design a high-performance chip without paying attention to its power consumption, because high power consumption results to high heat output and that might prove impossible to cool. Thus, in modern systems designed for speed that use extra logic to be more efficient, a common method is to simplify them. So, if for example a core can be simplified in order to have 80% of its performance for only half of the power consumption, then we can use two cores to have 160% of the performance for the same power consumption.

Another common problem is that many designers are accustomed to focusing on dynamic power. But *leakage* in its various forms (see 2.1.1) is becoming increasingly important in nanometer processes. Failing to account for that can very well lead to much higher than expected consumption and also functional failures in the more sensitive components.

# 2.1.5 Performance to power consumption ratio in different processor types

As shown on figure 2.2, there are many different architectures that can be used for the same purpose. The more specialized the architecture, the better the

performance and power efficiency but less flexible the resulting processor. So for example we can use a general-purpose microprocessor with reduced performance but high flexibility or a custom ASIC with high performance and no flexibility whatsoever. The same task on a processor of different level, can have great variance in execution time. Therefore the right processor, or co-processor should be picked to handle each task efficiently. For example, the number of clock cycles executed for the simple task of a counter can vary from one cycle in a hardware counter or several instructions with each one requiring many clock cycles each.

**Figure 2.2:** MOPS/watt versus flexibility [Piguet06]

But apart from those two extremes, there are several solutions in between, mainly reconfigurable processors and the aforementioned DSPs (chap. 1.1.1) and ASIPs (chap. 1.1.3). Reconfigurable processors prove to be very useful, as they allow the configuration of specialized instructions and execution units to the specified application.

The rest of the parameters that need to be defined is matching the *data width* of the processor (and subsequently the memory) to the required data. The required data does not necessarily need to be the same as the processor, so it is possible for example to execute 16-bit data on a 8-bit processor, but there is an extra cost and increased execution time for that. Additionally, each processor performs considerably better when facing the task it was developed for, and no processor is best for everything. For example, a DSP processor is much better than a microcontroller in performing a filter, but the microcontroller can handle control operations more efficiently. That is why we usually use a microcontroller with several dedicated co-processors to handle everything properly. This way each task is executed by the smallest and most energy-efficient component, but rarely all of them are working at the same time in parallel.

## 2.2 Memory efficiency

#### 2.2.1 SRAM

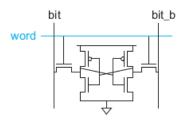

A SRAM is a memory cell array consisted of SRAM cells that are able to read, store and write data for as long as the power supply is on. A common 6-transistor SRAM cell(fig2.3) can be an order of magnitude smaller than a flip-flop. This 6T cell is compact, requiring less wiring and so features a small dynamic power consumption.

**Figure 2.3:** A typical SRAM cell composed of 6 transistors (6T)[Westell]

The cell contains a pair of weak cross-coupled inverters holding the state and a pair of access transistors to read or write it. In order to write in the cell the desired value and its complement are driven to the bitlines, bit and bit\_b and then the wordline, word is raised. This way bit or bit\_b are pulled down to indicate the new value. The challenge in SRAM design is have as small an area as possible but ensuring that the state is stong enough to withstand the influence of leakage and keep the state during a read, but weak enough to be overwritten during a write.

SRAM cells are structured in memory arrays of m address lines and m data lines. So the size of an SRAM is  $2^m$  words, or  $2^m \times n$  bits. Memory cells can have one or more ports for access. These ports may be read-only, write-only or support both, but not simultaneously. For larger SRAM memories, multiple smaller arrays are combined so that the wordlines and bitlines can be fast, narrow and low-power.

## 2.2.2 Memory power efficiency

There are various well-known techniques for low power consumption of memories. That usually includes cutting the memory in small pieces and only one piece is addressed to fetch or to store data (cache, hierarchical, divided workline and divided bitline).

In the quest to optimize processor cores for energy and performance, somewhere a bandwidth limitation of memory is hampering further optimization. Therefore often multiple, local scratchpad, memories are used. We have found that memory consumption may easily become a power dominating component. If

there is a strongly memory-intensive application, the memory accesses can go over 50% or even 60% of the total power budget of a typical DSP processor. As a result most DSP processors try to exploit the memory hierarchy and the register file in an effort to reduce the memory accesse. Pre-fetch techniques are particularly effective in DSP designed for applications with large data objects. Code density is also very effective, provided that the overhead of encoding and decoding makes up for the benefits.

The general guidelines followed to reduce memory consumption are turning on only the necessary subarrays to minimize the dynamic power, keep the other subarrays in sleep mode to minimize leakage and reduce the voltage levels to a the minimum required for the memories to function without loss of data or vulnerability to interference.

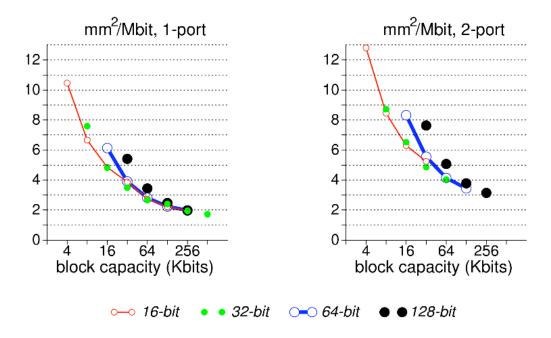

Modern SRAM memories have developed a lot during the last decade. As we can see in figure 2.4, featuring slightly old generation (2008) SRAM memories at 90nm, larger memory block are more area-efficient than smaller ones[Katev11]. Also, the difference between the different word sizes in area starts with a big overhead for the smaller word sizes, but become negligible in larger block capacities.

Figure 2.4: SRAM area needed for different block sizes[Katev11]

Figure 2.5 shows the power to performance ratio for different block capacities. Power consumpion is proportional to access frequency ( $\mu$ W/MHz). It can be observed that for every single one of the word sizes, the power to perfomance ratio rises slowly for the first few block capacities (due to increasing word-line and bit-line capacitance), but as the block capacities increase the average power increases at a much faster rate (because at some point more sense amplifiers are

required). It is also notable that the gap between the power consumpion of each of the word sizes is getting bigger for larger word sizes and for larger block capacities as well.

**Figure 2.5:** SRAM Power consumption for different block sizes[Katev11]

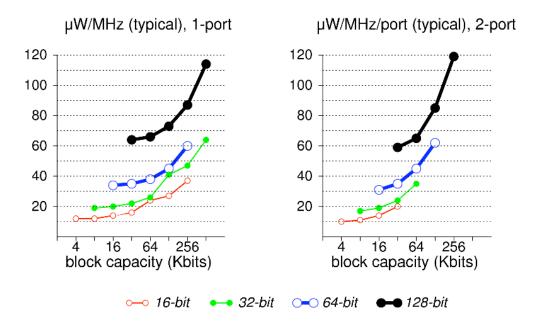

There were several measurements taken on the commercial memories available (fig.2.6) for different word sizes of  $2^5$  to  $2^{14}$  and data width sizes of 16 to 80 bits. We can see that it is possible to double the memory size (and also the instruction width) without also having a double power cost per memory access.

This shows that that bigger memories can used and despite the extra power cost, the total design can benefit if this helps the rest of the components of the processor.

### 2.2.3 Memory addressing modes

For specific purpose processors like DSP, there needs to be a well defined set of special addressing modes. These assist the processor in handling special data types or large data in less clock cycles, so this results in less energy consumed for the same application.

The design has to balance the benefits of the extra addressing modes against the extra complexity they introduce. They can be especially effective when it comes to FFT and other similar computations, however there needs to be careful planning of both the addressing and the software stack support if they are to provide efficient data structures that minimize the use of memory.

**Figure 2.6:** Power consumption for different word and block sizes in commercial SRAM memories

#### 2.2.4 Loopbuffers