# Materials for High-Density Electronic Packaging and Interconnection

Committee on Materials for High-Density Electronic Packaging, Commission on Engineering and Technical Systems, National Research Council

ISBN: 0-309-53669-3, 156 pages, 8.5 x 11, (1990)

This PDF is available from the National Academies Press at: http://www.nap.edu/catalog/1624.html

Visit the <u>National Academies Press</u> online, the authoritative source for all books from the <u>National Academy of Sciences</u>, the <u>National Academy of Engineering</u>, the <u>Institute of Medicine</u>, and the National Research Council:

- Download hundreds of free books in PDF

- Read thousands of books online for free

- Explore our innovative research tools try the "Research Dashboard" now!

- Sign up to be notified when new books are published

- Purchase printed books and selected PDF files

Thank you for downloading this PDF. If you have comments, questions or just want more information about the books published by the National Academies Press, you may contact our customer service department toll-free at 888-624-8373, visit us online, or send an email to feedback@nap.edu.

### This book plus thousands more are available at http://www.nap.edu.

Copyright © National Academy of Sciences. All rights reserved.

Unless otherwise indicated, all materials in this PDF File are copyrighted by the National Academy of Sciences. Distribution, posting, or copying is strictly prohibited without written permission of the National Academies Press. Request reprint permission for this book.

# Materials for High-Density Electronic Packaging and Interconnection

Report of the Committee on Materials for High-Density Electronic Packaging

National Materials Advisory Board Commission on Engineering and Technical Systems National Research Council

> NMAB-449 National Academy Press 1990

NOTICE: The project that is the subject of this report was approved by the Governing Board of the National Research Council, whose members are drawn from the councils of the National Academy of Sciences, the National Academy of Engineering, and the Institute of Medicine. The members of the committee responsible for the report were chosen for their special competences and with regard for appropriate balance.

This report has been reviewed by a group other than the authors according to procedures approved by a Report Review Committee consisting of members of the National Academy of Sciences, the National Academy of Engineering, and the Institute of Medicine.

The National Academy of Sciences is a private, nonprofit, self-perpetuating society of distinguished scholars engaged in scientific and engineering research, dedicated to the furtherance of science and technology and to their use for the general welfare. Upon the authority of the charter granted to it by the Congress in 1863, the Academy has a mandate that requires it to advise the federal government on scientific and technical matters.

Dr. Frank Press is president of the National Academy of Sciences.

The National Academy of Engineering was established in 1964, under the charter of the National Academy of Sciences, as a parallel organization of outstanding engineers. It is autonomous in its administration and in the selection of its members, sharing with the National Academy of Sciences the responsibility for advising the federal government. The National Academy of Engineering also sponsors engineering programs aimed at meeting national needs, encourages education and research, and recognizes the superior achievements of engineers. Dr. Robert M. White is president of the National Academy of Engineering.

The Institute of Medicine was established in 1970 by the National Academy of Sciences to secure the services of eminent members of appropriate professions in the examination of policy matters pertaining to the health of the public. The Institute acts under the responsibility given to the National Academy of Sciences by its congressional charter to be an advisor to the federal government and, upon its own initiative, to identify issues of medical care, research, and education. Dr. Samuel O. Thier is president of the Institute of Medicine.

The National Research Council was organized by the National Academy of Sciences in 1916 to associate the broad community of science and technology with the Academy's purposes of furthering knowledge and advising the federal government. Functioning in accordance with general policies determined by the Academy, the Council has become the principal operating agency of both the National Academy of Sciences and the National Academy of Engineering in providing services to the government, the public, and the scientific and engineering communities. The Council is administered jointly by both Academies and the Institute of Medicine. Dr. Frank Press and Dr. Robert M. White are chairman and vice chairman, respectively, of the National Research Council.

This study by the National Materials Advisory Board was conducted under Contract No. MDA 903-89-K-0078 with the U.S. Department of Defense and the National Aeronautics and Space Administration.

Library of Congress Catalog Card Number 90-60385. International Standard Book Number 0-309-04233X

This report is available from the Defense Technical Information Center, Cameron Station, Alexandria, VA 22304-6145. SO116

Cover: Schematic cross section of a molded plastic leaded chip carrier (Courtesy of AT&T Bell Laboratories) Printed in the United States of America First Printing, April 1990 Second Printing, November 1990

# About this PDF file: This new digital representation of the original work has been recomposed from XML files created from the original paper book, not from the original typesetting files. Page breaks are true to the original; line lengths, word breaks, heading styles, and other typesetting-specific formatting, however, cannot be retained, and some typographic errors may have been accidentally inserted. use the print version of this publication as the authoritative version for attribution

## **Abstract**

Electronic packaging and interconnections are the elements that today limit the ultimate performance of advanced electronic systems. Materials in use today and those becoming available are critically examined to ascertain what actions are needed for U.S. industry to compete favorably in the world market for advanced electronics. Materials and processes are discussed in terms of the final properties achievable and systems design compatibility. Weak points in the domestic industrial capability, including technical, industrial philosophy, and political, are identified. Recommendations are presented for actions that could help U.S. industry regain its former leadership position in advanced semiconductor systems production.

About this PDF file: This new digital representation of the original work has been recomposed from XML files created from the original paper book, not from the original typesetting files. Page breaks are true to the original; line lengths, word breaks, heading styles, and other typesetting-specific formatting, however, cannot be retained, and some typographic errors may have been accidentally inserted. Please use the print version of this publication as the authoritative version for attribution.

# This new digital representation of the original work has been recomposed from XML files created from the original paper book, not from the original typesetting files. Page breaks are true About this PDF file:

## **Preface**

What is packaging? The subject of this report is commonly referred to as electronic packaging, but the term "packaging" carries connotations that tend to trivialize the highly technical and critically important electronic context. Electronic packaging now goes well beyond physical protection and includes electric power distribution, signal transmission between integrated circuits, and, of growing importance, the removal of heat associated with the very high densities of circuit elements that are being achieved. Modern system performance is as much limited by these functions as by the operation of the integrated circuits. Thus, electronic packaging and interconnection are essential enabling technologies that underlie vital computer and other electronic applications. Success in integrating these enabling technologies into the nation's microelectronics efforts is directly related to how well the United States will succeed as a major competitive force.

The specific subject of this report is the materials employed in high-density electronic packaging and interconnection. Materials issues are closely coupled to other systems design factors, and all materials advances must be coordinated as the field progresses. A successful competitive position cannot be maintained without leading-edge materials engineering and science. Coordination of physical design, materials properties, and materials processing is essential. The competitive position of the United States in an area of the highest leverage is at stake.

This report focuses on first-and second-level packaging—i.e., the integrated circuit chip package and the printed circuit to which the chips are attached. The connectors, backplanes, cables, and other higher-level interconnect structures have been omitted because it was perceived that materials problems in these areas were less urgent. In addition, the higher interconnection levels are, at present, undergoing some degree of conversion from electrical to optical, and optical interconnections are outside the scope of this study. The committee believes that optical interconnection is a very important technology and will certainly spread to the board level and beyond in the course of time. Optical technology has many advantages and could depart radically from the geometries required of "wire"-based systems. An additional study of optical interconnection is strongly recommended <sup>1</sup>.

The literature on electronic packaging has recently been unified through publication of an authoritative monograph<sup>2</sup>. This handbook gives a coherent, balanced discussion of all aspects of electronic packaging and interconnection, with materials considerations appropriately integrated into physical design. In addition, the ASM INTERNATIONAL has published a

comprehensive document on packaging, its first that is directed specifically to electrical and electronic materials<sup>3</sup>. Concurrently with the preparation of the present report, a group has been working on a related project sponsored by the National Security Industrial Association (NSIA). Dr. Bruce E. Kurtz, chairman of the NSIA Electronics Packaging/Interconnection Task Force, has kindly provided the committee a draft of this material which was found to be highly valuable. The materials and processing interaction in packaging is effectively covered in a recent McGraw-Hill publication<sup>4</sup>.

Anticipating that further advancements in IC technologies would be hampered by limitations of currently available materials and processes, the Department of Defense and National Aeronautics and Space Administration requested the National Materials Advisory Board to examine the situation. A committee was appointed that included representation from industry, university, and research institutions and provided a balance of experience and knowledge in chemistry, polymer science, ceramics, materials science, electronics, and physics. A biographical sketch for each committee member is found in Appendix G.

A major objective of this study was to assess the current state of the art in packaging and to anticipate the requirements for new materials and processes for packaging highly integrated semiconductor chips and future designs, particularly for military and space applications. The committee was asked to assess the existing capability for packaging electronic components and existing limitations, identify probable needs in new materials and processing techniques to accommodate new package designs, determine where superconductor breakthroughs may be properly employed, identify the electrical, thermal, and mechanical properties of materials needed for the newly designed chips and interconnects, recommend where R&D efforts should be directed toward developing the needed materials and systems for future electronic packages, and, to the extent possible, assess the U.S. position relative to that of world competition—i.e., Japan, Europe, and others. Although the report is directed primarily to the sponsoring agencies, it is presented in a broad-based manner for a wider readership, to help them understand the current situation and gain a perspective on what actions are needed to enhance the domestic capability to compete in a global market. A discussion of nontechnical issues was not in the scope of the committee's task, however, thoughts on such issues were included to explain why certain actions are advised to help improve the industry's competitive position.

<sup>&</sup>lt;sup>1</sup> Photonics: Maintaining Competitiveness in the Information Era. Panel on Science and Technology Assessment. Washington, D.C.: National Academy Press, 1988.

<sup>&</sup>lt;sup>2</sup> Microelectronics Packaging Handbook. Rao R. Tummala and E. J. Rymaszowski, editors. New York: Van Nostrand Reinhold, 1989.

<sup>&</sup>lt;sup>3</sup> Electronic Materials Handbook, Vol. 1, Packaging, M. L. Minges, technical chairman. Materials Park, Ohio: ASM INTERNATIONAL, 1989.

<sup>&</sup>lt;sup>4</sup> principles of Electronic Packaging, Design and Materials Science. D. P. Seraphim, C. Lasky, and Che-Yu Li, editors. New York: McGraw-Hill, 1989.

# This new digital representation of the original work has been recomposed from XML files created from the original paper book, not from the original typesetting files. Page breaks are true About this PDF file:

# Acknowledgments

The committee is grateful to a number of individuals who provided extensive background materials for committee use. Experts were invited to committee meetings to present current data on specific topics of concern. The following are thanked for their generous participation:

### **MEETING 1**

- R A. Boudelaise of Westinghouse Defense and Electronics Center discussed Phase I of MANTECH packaging needs.

- J. L. Heaton of Sanders Microelectronics Center discussed MMIC packaging needs.

- M B. Ketchen of IBM's, T. J. Watson Research Center discussed Josephson packaging technology.

- P. V. McEnroe of Digital Equipment Corporation discussed wafer-scale integration.

- M. C. Peckerar of the U.S. Naval Research Laboratory presented an overview of VHSIC packaging needs.

- R. Smolley of TRW's, Electronics and Technology Division discussed VHSIC Phase II, advanced development of packaging needs.

- R. J. Willis of Floating Point Systems, Inc., discussed packaging of massive passive parallel systems.

### **MEETING 2**

- L. E. Cross of Pennsylvania State University discussed inorganic packaging materials and interconnects.

- D. C. Hofer of IBM's, Almaden Research Center discussed organic packaging materials from a customer's viewpoint.

- R. Jensen of Honeywell Sensors and Signal Processing Laboratory discussed copper-polyimide thin film interconnection technology for IC packaging.

- J. Kim of IBM's, T. J. Watson Research Center discussed IBM's thermal conduction module.

- J. A. Nelson of Unisys Corporation was unable to attend but submitted comments on packaging materials needs and challenges for large computers.

- R. M. Rivett of Edison Welding Institute discussed microelectronics metals joining.

- R. M. Rosenberg and J. F. Strange of DuPont discussed materials for packaging and interconnects from a vendor's viewpoint.

### **MEETING 3**

- J. E. Anderson of Ford Motor Company discussed materials for electronic packaging in automotive applications.

- J. S. Browning of Sandia National Laboratory discussed radiation effects in microelectronics.

- A. Christou of the U.S. Naval Research Laboratory discussed gallium arsenide interconnects.

- A. Huang of AT&T Bell Laboratories discussed optical digital computers, the devices and architecture.

- A. Husain of Honeywell Sensors and Signal Processing Laboratory discussed trends in optical interconnect technology.

- W. B. Jones of Sandia National Laboratories discussed performance and metallurgy of aluminum metallization interconnects.

- L. M. Levenson of General Electric Company presented the highlights of the Santa Barbara Engineering Foundation Conference of 1988.

The government liaison representatives are thanked for participating in committee discussions and providing valuable support materials and data for committee use. D. R. Franck (President of Empire Planning Group, Ltd.) is thanked for undertaking an assignment for the committee to provide data on systems technology projections through 1994. In addition, some specific industry data in Appendix B are taken from a report, *Chip Carriers and Other Integrated Circuit Packages: A Review and Update, 1988*, (copyright 1988), with the kind permission of James D. Welterlen, President of Welterlen, Inc. These tables illustrate the complexity of the chip encapsulation picture, but they cover only a fraction of the field covered in Welterlen's annual reports.

The committee is indebted to committee member J. C. Logue, whose years of packaging experience at IBM was invaluable in its deliberations by providing technical insight and details for the report. The chairman acknowledges with thanks the extra efforts of Mr. Logue for his assistance in coordinating various inputs to the report. The committee members are thanked for their dedication and for their patience during the lengthy task of

preparing and revising the report to ensure its accuracy and currency. Particular thanks go to the members of the committee who served as chapter or section coordinators for assembling pertinent facts for various parts of the report and presenting the data in a timely, open-minded, and professional manner. Specifically, Paul Penfield and J. C. Logue coordinated Chapter 3, C. A. Neugebauer coordinated Chapter 4, and Jack Hilibrand contributed heavily to Chapter 7. Discussions in the report are based on data compiled through Spring, 1989.

Special thanks are owed to colleagues at AT&T Bell Laboratories in connection with Chapter 4. D. W. Johnson, L. T. Manzione, and J. M. Segelken contributed important sections and provided expert advice on packaging issues generally, and L. L. Blyler, Jr., and L. D. Loan consulted extensively on this material. M. John Drobny provided the professional renderings for the report figures. Special thanks go to Shiro Matsuoka for his invaluable assistance as technical advisor to the committee. Ms. Irene M. Fedun greatly assisted in coordinating and assembling the preliminary report draft, efforts which are appreciated by all concerned.

Finally, the committee gratefully acknowledges the untiring support of George Economos, senior program officer of the National Materials Advisory Board, and his secretary Ms. Aida Neel, in all stages of report preparation.

DAVID W. MCCALL CHAIRMAN

About this PDF file: This new digital representation of the original work has been recomposed from XML files created from the original paper book, not from the original typesetting files. Page breaks are true to the original; line lengths, word breaks, heading styles, and other typesetting-specific formatting, however, cannot be retained, and some typographic errors may have been accidentally inserted. Please use the print version of this publication as the authoritative version for attribution.

### Committee on Materials for High-Density Electronic Packaging

### Chairman

DAVID W. McCALL, AT&T Bell Laboratories, Murray Hill, New Jersey

### **Members**

GENE M. AMDAHL, Andor Systems, Inc., Cupertino, California

DEBORAH D.L. CHUNG, State University of New York, Buffalo

BARRY K. GILBERT, Mayo Clinic, Rochester, Minnesota

JACK HILIBRAND, G. E. Aerospace Company, Philadelphia, Pennsylvania

DONALD C. HOFER, IBM Corporation, San Jose, California

JOSEPH C. LOGUE, Consultant, Poughkeepsie, New York

CONSTANTINE A. NEUGEBAUER, General Electric Company, Schenectady, New York

R. FABIAN W. PEASE, Stanford University, Stanford, California

PAUL PENFIELD, JR., Massachusetts Institute of Technology, Cambridge, Massachusetts

RICHARD L. SCHWOEBEL, Sandia National Laboratories, Albuquerque, New Mexico

BARRY H. WHALEN, Microelectronics & Computer Technology Corporation, Austin, Texas

### **Report Coordinator**

JOSEPH C. LOGUE, Consultant, Poughkeepsie, New York

### **Technical Advisor**

SHIRO MATSUOKA, AT&T Bell Laboratories, Murray Hill, New Jersey

### **Liaison Representatives**

ROBERT L. DENISON, Wright-Patterson Air Force Base, Ohio MARTIN C. PECKERAR, U.S. Naval Research Laboratory, Washington, D.C. OWEN P. LAYDEN, Department of the Army, Ft. Monmouth, New Jersey MICHAEL A. STROSCIO, Army Research Office, Research Triangle Park, North Carolina GEORGE G. HARMAN, National Institute of Standards and Technology, Gaithersburg, Maryland JAMES D. MURPHY, Defense Advanced Research Projects Agency, Arlington, Virginia JEROME PERSH, The Pentagon, Washington, D.C.

### **NMAB Staff**

GEORGE ECONOMOS, Senior Program Officer AIDA NEEL, Senior Secretary

CONTENTS xiii

# **Contents**

|           | Executive Summary                                                      | 1  |

|-----------|------------------------------------------------------------------------|----|

| Chapter 1 | Introduction                                                           | 9  |

| Chapter 2 | Microelectronic System Trends and Packaging Needs                      | 21 |

| 1         | Scaling Theory                                                         | 22 |

|           | Gallium, Arsenide Technology                                           | 28 |

|           | Rent's Rule                                                            | 29 |

|           | Chip Technologies                                                      | 31 |

|           | Some Package Design Considerations                                     | 36 |

|           | References                                                             | 38 |

| Chapter 3 | Packaging Strategies and Associated Materials and Process Requirements | 41 |

|           | Future Packaging Strategies                                            | 45 |

|           | Packaging Materials, Requirements                                      | 51 |

|           | Summary of Future Packaging Materials and Processes Needs              | 56 |

| Chapter 4 | Materials Issues                                                       | 59 |

|           | Dissipation of High Thermal Loads                                      | 60 |

|           | Dielectrical Properties                                                | 62 |

|           | Interconnect Voiding                                                   | 64 |

|           | Thermal Fatigue                                                        | 64 |

|           | Interfacial Processes                                                  | 64 |

|           | High Temperature Stability and Chemical Reactions                      | 65 |

|           | Trace Radionuclides in Packaging Materials                             | 65 |

|           | Electromagnetic Interference                                           | 66 |

|           | Encapsulants and Hermeticity                                           | 66 |

|           | Materials-Related Reliability Issues                                   | 67 |

|           | Military Packaging                                                     | 68 |

|           | References                                                             | 69 |

| Chapter 5 | Some Specific Materials                                                | 71 |

|           | The Evolution of Epoxy Materials in Plastic Packaging                  | 71 |

|           | Future Trends in Plastic Packaging Materials                           | 73 |

|           | Organic Printed Circuit Board Materials                                | 76 |

|           | Processing Technology for Ceramic Packages, Board, and Substrates      | 77 |

| CONTENTS   |                                                        |     |

|------------|--------------------------------------------------------|-----|

|            | Other Ceramic Materials                                | 79  |

|            | Polyimides in High-Density Packaging                   | 84  |

|            | Tape Automated Bonding                                 | 87  |

|            | Diamond                                                | 88  |

|            | Superconductors                                        | 88  |

|            | Composites                                             | 89  |

|            | Materials for Very-High-Frequency Digital Systems      | 91  |

|            | Materials for Connector Applications                   | 92  |

|            | The Thermal Conduction Module                          | 92  |

|            | References                                             | 94  |

| Chapter 6  | Organizational, Funding, and Policy Issues             | 95  |

|            | Integration                                            | 95  |

|            | Systems Versus Materials Approaches                    | 97  |

|            | Programs and Consortia                                 | 98  |

|            | Sematech                                               | 99  |

|            | The University Role                                    | 100 |

|            | Emigration of Technology                               | 102 |

|            | Private Funding and Public Funding                     | 103 |

|            | Conclusion                                             | 104 |

| Appendix A | Glossary of Some Terms and Acronyms Used in the Report | 105 |

| Appendix B | Some Industry Component Data                           | 109 |

| Appendix C | Microprocessor Operating and Structural Parameters     | 115 |

| Appendix D | Examples of Developments in Board Technologies         | 119 |

| Appendix E | Materials Properties                                   | 123 |

| Appendix F | Examples of Multichip Modules                          | 127 |

| Appendix G | Biographical Sketches of Committee Members             | 135 |

# **Executive Summary**

Electronic packaging has become an important element in electronic systems and may very well be a critical pacing feature in the future. Modern packaging technology embodies a host of materials science and technology issues and necessitates an integrated design approach that includes packaging considerations from the very outset. Integrated circuit performance can be limited or enhanced by packaging features, and the designer no longer has the latitude to ignore such considerations until the electronic portion of the design is complete. Packaging, with all its implied materials issues, is a basic design feature. The materials of packaging and interconnection that are intrinsic to the design effort are the subject of this report. The ability to incorporate these issues into microelectronics products will be a key factor in maintaining this nation's competitive position in the world market for advanced electronics.

Electronic systems needed in the next few years will require unprecedented packaging technology. The rapid advances in integrated circuit chip capabilities will continue to increase demand for enhanced interconnect capability as regards numbers of connections (pinouts), pinout configuration, heat removal, signal rise time, signal transit time, power lead inductance, power supply current, and environmental protection. The projected evolution of chip parameters is presented in the format suggested by scaling theory for three families of chips [bipolar, CMOS, and GaAs], and the concomitant implications for packaging and interconnection are discussed. Appendix A contains a list of many special terms used in this report. No attempt is made to explain all terms commonly used in the industry. For individual chips, there will be hundreds of pinouts, tens of watts, and subnanosecond rise times in the 1990s. Clearly, interconnect structures will require considerable enhancements to translate these chip capabilities to system performance. Heat dissipation in thousands of watts and power supply requirements of thousands of amperes are projected at the board level. Special physical design problems arise with very-high-frequency and very high-speed circuits. There is concern that the United States is relying too heavily on foreign sources of packaging and interconnection materials for high-density electronic circuitry.

The United States has lost significant market share in advanced chip technology, and the process continues. As domestic production is lost (e.g., in DRAMs), advanced packaging and interconnection strategies will be handicapped by reluctance of foreign chip makers to supply ICs in unpackaged or other non-standard forms. Printed wiring board (PWB) technology continues to evolve with the introduction of efficient surface-mount technology, finer

patterns, greater numbers of signal layers, and improved board resins for greater dimensional control. Forty-layer boards have been achieved. PWBs will certainly be important for many years to come, but their limitations in very-high-density electronics will have to be addressed in terms of new design strategies in which materials innovations will play a key role.

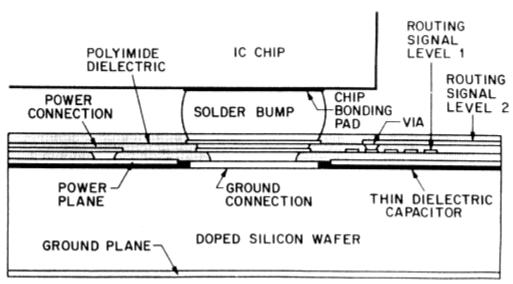

Packaging is now approaching a turning point at which single-chip packages cannot be assembled directly onto conventional circuit boards without impairment of performance. A new level of packaging, the multichip module (MCM), is coming into prominence. MCMs consist of inorganic base layers, to provide power, ground and decoupling capacitances, and signal interconnect patterns fabricated of high-conductivity metals and low-dielectric-constant organic polymer dielectrics. The individual chips are assembled on top, either in unencapsulated form or in low-impedance single-chip packages. The signal interconnection density achievable is very high, owing to the fineness of the patterns. Two layers of MCMs can replace dozens of layers in conventional PWBs. Materials support for MCM designs must be strongly encouraged in the United States.

Materials issues emphasize both process and final property aspects of design, and material compatibility is a critical issue. Many different properties and compatibilities must be optimized simultaneously. Issues of importance include the following:

- · coefficient of thermal expansion

- dielectric properties

- thermal conductivity

- electrical conductivity

- · interfacial chemistry

- adhesion

- mechanical strength and toughness

- impact strength

- · long-term stability

- purity (including absence of radioactivity)

- vapor permeability (especially water)

- corrosion

- metal migration

- process control and reproducibility

- process compatibility

The engineering-design-manufacturing process sequence is somewhat difficult to describe briefly while emphasizing materials factors. Discussing some specific packaging and interconnection materials (see Chapter 5) can give a flavor for the complex compromises that must be made. These systems include epoxies for encapsulation and PWBs, ceramic materials for packages and co-fired circuits, polyimides for dielectric layers, and more exotic materials, such as superconductors, synthetic diamond layers, and composites.

Beyond the domain of engineering, packaging and interconnection materials are strongly affected by business, organizational, and government policy issues. International competition presents implications in terms of economics and national security. These interacting business and government

issues have much in common with many other high-technology areas, but packaging materials is a field in which the organizational problems are important, competition is fierce, and the financial consequences of losing out are massive. The United States has already lost consumer electronics and the entire computer market could follow. Packaging is one of the essential ingredients in the future U.S. position.

In certain respects, the United States is poorly positioned in regard to materials employed for packaging and interconnection. In the sequence of raw materials, intermediates, formulated materials, completed piece parts, and assembled modules and systems, materials and information move from one company to another in a highly incomplete and imperfect way. The sequence is fragmented, and the technology is migrating to other countries, leaving U.S. manufacturers dependent on foreign supply houses. Some form of domestic supply chain that accomplishes the advantages of a vertically integrated corporation is urgently needed.

A further problem exists in connection with government-funded research and development. The most substantial source of federal money is the Department of Defense, and many important initiatives have received timely funding from that agency. Unfortunately, electronic packaging of military systems has evolved along lines that differ significantly from computer, consumer, automotive, and other electronic subareas. There are some hopeful signs of rationalization, but much remains to be done.

In recent years, many consortia have been formed to address problems faced by the United States in regard to international competition in technological matters. Groups of companies and other organizations come together to address common issues in a coordinated way and to pool resources. A consortium specifically addressed to materials for electronic packaging and interconnection could be an effective approach to some of the problems faced. Coupling to system design and engineering and the involvement of first-class engineering talent are essential features. An alternative to an independent consortium on packaging might consist of an expanded emphasis on packaging and interconnection by existing consortia.

The United States has enormous intellectual resources in the university system, and it will be important to bring this potential to bear on the critical area of electronic packaging. Coordination of efforts of the various relevant university engineering and science departments will not be easy for this interdisciplinary field. Coupling of university programs to industrial design, development, and manufacturing projects in productive arrangements will require creative management. Similarly, involvement of national laboratories and other organizations also must be implemented. Issues of organizational culture complicate communication among the potential contributors. The National Science Foundation's program on engineering research centers is a recent approach to finding a useful format, but it is directed to support large centers. Smaller grants that encourage materials innovations and industrial collaboration are needed.

The United States has lost significant segments of the electronics market in recent years. The future position of the United States as a world

power and the U.S. standard of living depend on a broadly-based response to foreign competition. Any response that does not include aggressive materials and packaging programs will fail to regain and sustain the U.S. position. Both domestic comfort and national security are at stake.

The committee's conclusions and recommendations regarding specific areas follow.

National policies. Antitrust laws still wield considerable influence in U.S. business circles. The need for

strict interpretation of the laws has been largely eliminated by the growth in overseas competition,

which will prevent any U.S. combine from raising prices to the disadvantage of the public.

Modernization of these laws should be undertaken with emphasis on the features that affect the

competitivness of U.S. corporations in critical world markets.

The introduction of advanced packaging technology and materials in U.S. industry could be facilitated by selectively removing antitrust restrictions on "buying cooperatives." Specifically, if U.S. companies were permitted to aggregate demand for new products (e.g., packaging materials), U.S. producers would be stimulated to risk their capital and develop the needed manufacturing capability. The committee concludes that a major impediment to U.S. competitiveness in computer and other electronic systems is the unwillingness of domestic material suppliers to invest capital for research, development, and production in long-term ventures. By aggregating market demand (as is done in Japan), U.S. electronics manufacturers would provide a more attractive market that would stimulate production of advanced materials and build a self-sustaining market. This would help compensate for systemic advantages of similar actions enjoyed by foreign materials companies.

Foreign companies also enjoy low-interest loans that encourage greater patience in market development. Some form of selective capital encouragement should be considered as a part of a broadly-based U.S. strategic plan to revive, sustain, and create critically-important base technologies. This could be done at the state level as well as on the federal level. It is difficult to overstate the need for actions that will encourage the long-range research and development necessary to provide the technology for future industries. Low-interest money is needed. Tax credits for research and development are an alternative approach that should be considered.

In an era of emphasis on short-term financial results, it is important to provide incentives for long-term investment in technologies that will build wealth for the nation. Although it has not been discussed widely, the much-admired U.S. corporate research and development laboratories are increasingly under pressure to shorten their sights and turn over quick profits. The current frenzy for mergers, acquisitions, and other forms of corporate churning is destabilizing and destroying the climate for long-range technical development. Some form of legislation that would discourage these practices seems desirable. Legislative solutions by their nature are long term. Thus, it is all the more important that a national strategiic program be undertaken to find remedies for our present malaise. The problems do not show signs of self-cure.

The committee discussed some changes in regard to patent procedures that could enhance U.S. competitiveness in the packaging materials area. Legislation would not be required for a system that gives priority on Patent Office and Patent Court dockets for submissions in the packaging area. (This already has been done for high-temperature superconductivity.) The ad hoc nature of this approach is a negative aspect. Legislation to allow the formation of patent pools and licensing arrangements by removing antitrust constraints for a period of 10 to 20 years has been proposed. As U.S. corporations become owned by and allied with foreign companies, legislative and procedural efforts to favor U.S. firms become awkward and difficult to administer.

User consortium. The committee exhibited considerable enthusiasm for an industry-led consortium of

packaging-materials users, with the objective to develop a stronger U.S. base of packaging-materials

suppliers. This consortium would develop materials requirements and materials application technology,

and would cultivate domestic sources of supply. The analogy with Sematech, the U.S.-based consortium

aimed at integrated circuit process equipment, is strong, and the term "Sepatech" was coined for

purposes of discussion among committee members. Table 1 illustrates the analogy.

Table 1 Analogy of U.S.-Based User Consortia

| Parameter                                              | Sematech                                                                                                           | "Sepatech"                                                                                                        |

|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| Intended to motivate                                   | Equipment suppliers to integrated circuit manufacturers                                                            | Chemical suppliers, compounders, and other materials suppliers                                                    |

| Set up by:                                             | Chip makers                                                                                                        | System companies using packaging and inter-connection technology                                                  |

| Activity:                                              | Prototype and build leading-edge parts,<br>working with equipment suppliers to<br>integrated circuit manufacturers | Perform materials and process evaluation,<br>build some demonstration systems, and<br>establish sources of supply |

| Vehicles for activity:<br>Full-scale manufacturing by: | Memories (advanced DRAM and SRAM US Memories, Inc., employing the apparatus, materials, and processes developed    | Advanced work stations System houses employing materials and processes                                            |

The consortium approach offers an increasingly acceptable way for manufacturers to pool their resources and aggregate their markets at a precompetitive stage. The approach places responsibility and control in the hands of the user industry and, therefore, ensures development along relevant paths. Financing must be substantially industrial ("earnest money"), but government investment can significantly encourage and facilitate establishment of the combine. Indeed, government funding at some level is probably essential and justified.

Consortia are controversial, and there is a lot to be learned in their organization, strategic objectives, and operation. Clearly, success depends on the participating organizations, which must provide quality people at all levels and viable long-term career paths for individuals. The committee is aware that consortia are subject to diverse forms of criticism, but the consortium approach is a positive mechanism to relieve the problems of U.S. industrial fragmentation. There are not many readily implementable alternative approaches.

- Military packaging. The packaging of integrated circuits for U.S. military systems must be hermetic, which has caused military electronics systems to lag considerably in terms of overall capabilities. The committee urges that alternative means be found to allow military hardware to move into the mainstream of electronic packaging, while still preserving reliability over long periods in difficult environments. Some study programs are under way in specific areas (e.g., silicone gel coatings), but a broadly-based action group should confront the issue and initiate studies that will lead to needed change. Although it is possible to obtain high levels of performance under hermetic constraints, the committee believes that pursuit of other options is a promising approach that should be encouraged.

- Industry-national laboratory-university coupling. Although systems manufacturers have been very active in work on packaging and interconnection materials and structures, relatively little activity in this area is evident in universities and the national laboratories. The committee feels that interconnection and packaging are regarded as insufficiently exciting by many members of the academic community. Some means is needed to stimulate university work in the area. The National Science Foundation's Engineering Research Center program would be well suited for establishing a close coupling of industrial scientists and engineers as an explicit part of the basic format. A program of smaller grants, similarly structured, could be highly useful. Also, coupling of national laboratory talent in the area should be pursued. Clearly, new and innovative means must be found to focus more of the considerable U.S. technical power on the issues electronic packaging.

- Specific materials for support. The following specific materials and process areas are recommended for support in connection with electronic packaging and interconnection. In any such list, there is the danger of important omissions, statement of the obvious, and possible emphasis on areas

that lie close to the interests of the committee members. The following list had general support:

- Present mainline materials should be pursued to bring U.S. capability up to a position of world leadership. Briefly, this includes copper, gold, and aluminum metallization with progress on high reliability in high current density; alumina and aluminum nitride, and other ceramic processing for preparation of advanced interconnect details; further development of epoxies for encapsulation, board resins, and adhesives; and development of polyimides and other high-temperature polymers for substrates, interlayer dielectrics, and other uses. Benzocyclobutanes are a very promising class of low dielectric constant polymers that are beginning to appear in electronic products.

- Glass-ceramic substrate compositions that can be co-fired with copper are viewed as an area of the highest priority. Much work has been done, but the problem has not been solved.

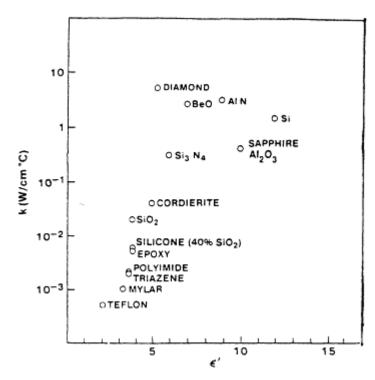

- 3. Low-dielectric-constant materials and interlayers are becoming increasingly important because signal transit time limits circuit performance. Polymeric materials are available with electric permittivity as low as 2, but substantial development is needed to bring the many other properties and process variables into useful ranges. Ceramics seem less likely for low permittivity.

- 4. High-thermal-conductivity materials for packaging are needed. Composites offer advantages in this area. Thermoelectric cooling offers an alternative approach.

- Materials for high-reliability encapsulation are extremely important. Hermetic structures are expensive and not entirely reliable. Silicone gels are currently under study, with promising initial results.

- 6. New solder compositions that are creep resistant would be valuable. Solder substitutes (e.g., anisotropically conducting polymers and ceramics) can be used for low-temperature assembly.

- Composite materials can be employed to engineer combinations of properties not achievable with homogeneous substances.

- 8. Materials amenable to environmentally benign processing (e.g., dry processing, aqueous-based systems) will become increasingly important. Circuit-board cleaning is a major source of solvent loss to the atmosphere, which leads to ozone depletion and other ills.

- High-temperature superconducting oxides are exciting candidates for interconnects. Chemical stability, electrical contacts, and other problems remain to be solved. (Bear in mind that copper, aluminum, and other metals also are considerably better conductors at liquid nitrogen temperature than at room temperature.)

10. Synthetic diamond films offer great promise for mechanical protection, chemical isolation, and electrical insulation. The thermal conductivity is uniquely high.

11. The ability to design materials with thermal expansion tailored to the application is emerging and should be extremely important for interconnect structures.

# Chapter 1

### Introduction

In the 40 years since the invention of the transistor, much attention has been given to silicon devices and integrated circuits (ICs). (See Appendix A for some terms and acronyms.) The impact of silicon electronics triggered the era of information processing and continues to produce amazing progress. The size of the circuit elements, the speed of their operation, the minimal power consumed, the cost per element, and the reliability of the circuits have improved dramatically. Today, silicon integrated circuits (chips), about the size of a fingernail, may contain a million transistors and cost a few dollars or tens of dollars (or hundreds in extreme cases), depending on the type and production level. There are good reasons to expect that some chips will contain a billion elements by the end of this century, and other characteristics will be improved as well. The recognition and praise lavished on silicon electronics over the past 4 decades is entirely justified, and the future remains promising.

And yet, integrated circuit chips are not useful until they have been woven into the fabric of interconnections and packaged. Packaging and interconnection (interconnects) provide structural support, mechanical and chemical protection, thermal management, power, ground, and signal transmission, including timing. The package must be durable and manufacturable and allow access for testing and repair. System performance in today's advanced systems is as likely to be limited by packaging and interconnection as by the chips themselves. In this report, high-density electronic packaging and interconnection will be described from the point of view of the materials of construction. The time frame of this report covers the present (1989) and the period in which present practice evolved and extends toward the end of the century. It is probable that reasonable predictions can be made extending for 5 or 10 years, but foreseeing system trends in the next century is highly speculative.

The many different sectors that encompass the field make it difficult to separate those to include or exclude. Consumer products, computer mainframes, supercomputers, telecommunications switching, personal computers, work stations, automotive components, and various military classes and other subareas all represent modern practice in the context of specific needs. Some consumer products use an aggressive packaging strategy. Veryhigh-frequency systems are often not high density. Advanced areas (e.g., computer mainframes) are inherently expensive and thus do not represent the leading

edge of developments in other applications. Therefore, this report concerns itself with high-density packaging, in the sense of chips with large numbers of I/Os (inputs, outputs, or both) and the need for high-speed communication between chips.

Materials properties play a critical role in system performance and in manufacturing process effectiveness. The materials in use have evolved along with the physical design of the electronic systems, and today's structures represent engineering optimization of many factors. It is of little benefit to consider the properties of the materials outside the context of the application. Furthermore, the packaging and interconnection structures are composites containing many different materials in close proximity. Thus, interfacial properties and materials compatibility factors are often more important than bulk properties of the isolated materials. The dependence of the materials properties on the manufacturing process is also important.

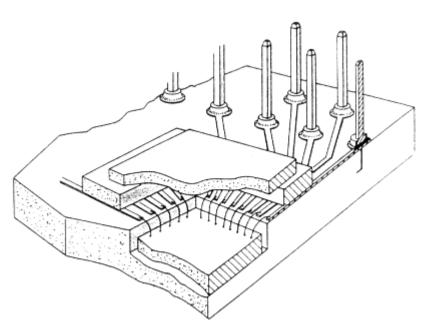

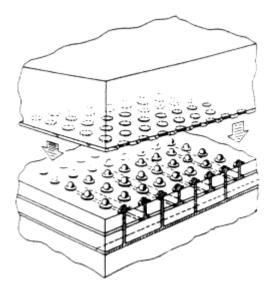

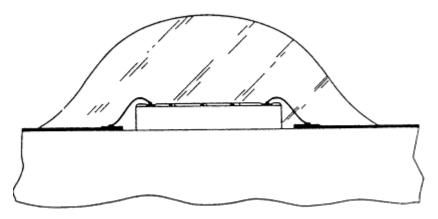

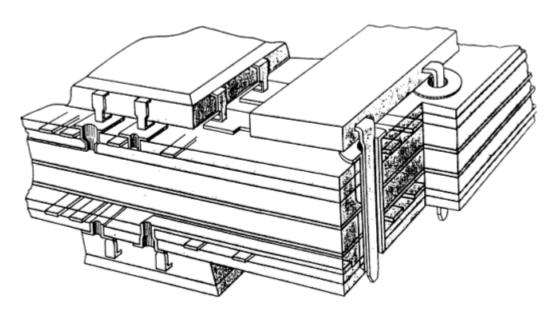

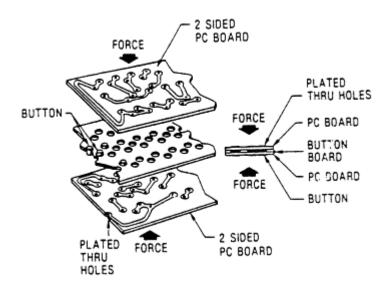

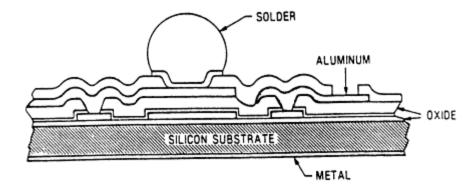

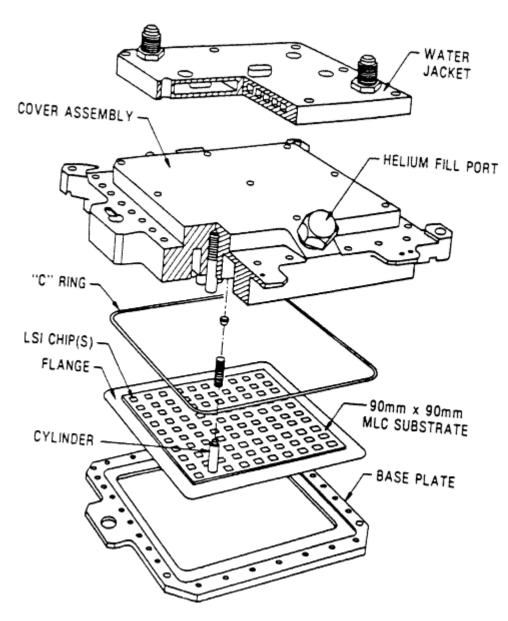

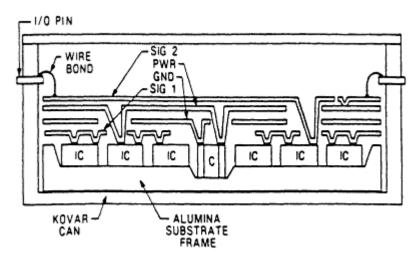

Electronic packaging includes all structures that are designed to protect the integrated circuits, the attendant interconnections and the related circuitry from physical damage and any other impediment to achieving design performance. Interconnections include all means of communication (power, timing, data, results) from one integrated circuit to another or from one system of circuits to another. Interconnections on the chips themselves is not considered in this report, and interconnection by means other than electrical (e.g., photonic) are also excluded. Thus, the subject matter of this report concerns materials issues involved in electric circuits that run from the bonding pad of a chip through the chip package (if any) by means of a lead frame (or other fan-out to leads), through strip-line circuits on a substrate that may be connected by "vias" perpendicular to the plane of the substrate, and end at other integrated circuit bonding pads; it also includes other components or connectors that lead to other circuit boards, shelves, or frames. The physical nature of this packaging and interconnection hierarchy is indicated in Figures 1-1 through 1-7.

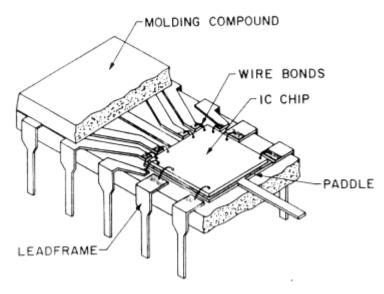

Figure 1-1 Cutaway view of a plastic DIP.

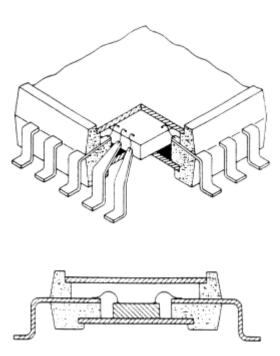

Figure 1-2 Schematic representation of a chip carrier. The chip is die bonded to the package. The signal, power, ground, and timing leads are wire-bonded to bonding pads on the chip. (A TAB inner lead frame could replace the wire bonds shown.) The exterior case may be premolded plastic (as shown) or ceramic.

Figure 1-3

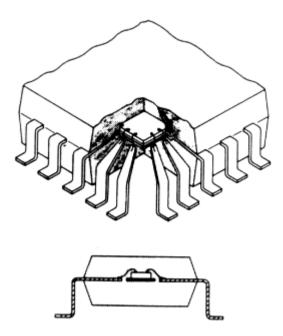

Molded plastic quad design or plastic leaded chip carrier (PLCC). The chip is diebonded to the paddle, which is connected to one or more ground leads. Signal, power, ground, and timing leads are connected by wire bonding pads. (A TAB inner lead frame can be used for this purpose.)

Figure 1-4

Cutaway of a PGA. The chip is die-bonded in the ceramic cavity and wire-bonded to the conductor fan-out, which is plated onto the ceramic. The outer end of each fanout finger is terminated onto a brazed pin, which is inserted into a through-hole on the PWB. This package can then be sealed hermetically with a lid (ceramic or metal). Similar packages with surface-mount leads are also employed. The device is shown inverted, and in use the active side of the chip would face the PWB (face down). The pins can be made to exit the ceramic on the opposite side (face up). The face-down option shown offers a favorable surface for heat-sink attachment.

Figure 1-5 A field of solder bumps with device ready for mounting in C4 attachment (controlled collapse chip connection).

Figure 1-6 Direct chip attachment with protective polymer overcoat ("glob top").

Figure 1-7

Printed wiring board circuit shown in cutaway to reveal inner connector layers and vias. A surface-mount device (left) and a through-hole device (right) are illustrated. Note that surface-mount devices can be mounted on both sides of the board (as shown) and do not consume valuable inner layer space with the through-hole.

Integrated circuit chips are encapsulated in three types of packages: dual in-line packages (DIPs), chip carriers (CCs), and pin grid arrays (PGAs). Each option has many variants, and only the most elementary description is attempted herein. In terms of numbers of units manufactured, the DIP is most important. Chip carriers, however, are now being adopted widely and should rival DIPs in numbers within a few years. In monetary terms, DIP and CC packaging are comparable today, owing to the higher average cost per unit of the CC option. PGAs are very expensive and are employed only for chips with large numbers of external connections (I/Os).

The magnitude of the packaging market for 1987 is summarized in Table 1-1. The \$2.0 billion packaging total is part of a total U.S. IC market of \$9.3 billion. The 1987 market for printed circuit boards amounted to \$5.1 billion, and edge connectors for boards amounted to \$0.8 billion. Thus, the 1987 silicon cost of \$7.3 billion was supported by more than \$7.9 billion in packaging and interconnection. These numbers are imperfect, owing to the omission of captive production by equipment suppliers and other factors, but nonsilicon costs are comparable to and probably greater than silicon costs. The numbers also omit the hybrid market (U.S. 1987, about \$4 billion), a substantial portion of which can be classified as interconnection and packaging. In view of the rate at which silicon costs are dropping, this spread in costs will increase unless packaging technology is given more emphasis.

Table 1-1 U.S. Packaging Market, 1987 Estimate

| Туре         | Units (billion) | Average Cost (\$/unit) | Total Cost (billion \$) |  |

|--------------|-----------------|------------------------|-------------------------|--|

| DIP          | 7.4             | 0.13                   | 0.93                    |  |

| CC           | 0.7             | 0.68                   | 0.47                    |  |

| PGA          | 0.05            | 6.61                   | 0.31                    |  |

| Other        | 0.7             | 0.34                   | 0.25                    |  |

| Total (avg.) | 8.9             | 0.22                   | 1.96                    |  |

The lead frames of DIPs are inserted in holes (vias) that extend through the printed circuit board. These holes are usually drilled on a 100-mil (0.1 in.) grid and each (copper plated) hole passes through each layer of a multilayer circuit. Chip dimensions are conventionally discussed in terms of micrometers (µm). Printed wiring interconnection structures are usually described in terms of mils (i.e., 0.001 in.). Advanced interconnection structures may involve both units; 1 mil is equal to 25.4 µm. The holes account for an appreciable fraction of the board area and thus limit the number of interconnections that the board can support. Chip carriers (CCs) are bonded only to the top surface (surface mount assembly, SMA) of a multilayer circuit, and no grid of holes are needed. With SMA, components can also be mounted on both sides of the board. Therefore, CCs with SMA are

capable of a higher density of interconnection, which is an important driving force for CCs to displace DIPs. Pin grid arrays (PGAs) are also available in surface-mount form.

Chips are attached to the lead frame by "die-bonding" on the back side with solder or conducting adhesive, and the bonding pads are connected to the lead frame fingers by means of fine gold or aluminum wires. A "ball" bond is formed at the chip bonding pad and a "wedge" bond is formed at the inner lead frame finger. The process of wire bond formation is automated and very fast, although they are done serially, one at a time. The bonding pads on the chip are usually restricted to the perimeter. The spacing between bonding pads is, however, limited (about 6 mils) by the size of the wire-handling tool, which is an important design factor affecting chip die size for circuits with a large I/O count. An alternative to wire bonding is tape automated bonding (TAB), in which the lead frame is a thin copper layer supported by polyimide film and all the inner fingers are bonded to the chip pads in a single operation. By supporting the leads on film and eliminating the wire bonding tool, finer lead spacing (about 4 mils) and higher interconnection density are possible. This technology has been available for many years, but no large-scale displacement of wire bonding has occurred. Difficulties involved in preparing the pads or tape fingers ("bumping") and in the simultaneous bonding operation are significant.

Preformed packages (premolded plastic or ceramic) are sealed by affixing a lid. The chip resides in a cavity. If the package material is ceramic, the seal may be hermetic, a feature required for most military and other high-reliability circuits. All plastic materials are permeable to some degree, and thus hermeticity cannot be achieved today in plastic packages. Even so, plastic packages can be highly reliable. Plastic packages can be premolded, but they are more likely to be transfer-molded after the wire bonds have been formed. In this process, the chip, bonded to the lead frame, is placed in a mold tool and molten plastic is forced in to fill the cavity completely. Good adhesion between the plastic and the chip and the lead frame is achieved, which makes the structure durable. After the chip has been sealed in its package, it can be tested, transported, and mounted on a printed circuit board.

An alternative approach involves direct mounting of unpackaged chips on circuit boards. In the soldering process, the chips "float" (face down) on solder balls that form the conducting bridge to the circuit. This approach is sometimes called C4 bonding (for controlled\* collapse\* chip\* connection\*). The bonding pads are not restricted to the periphery of the chip, thereby offering considerable advantage. Other "bare chip" options exist, including the use of face-down, "beam-lead" or TAB lead frame arrangements, and also face-up wire-bonded configurations. Following assembly, these chips may be covered with a plastic coat ("glob top") for protection (see Figure 1-6). Chip-on-board (COB) interconnection is not amenable to the burn-in and testing required for military use, and hence this approach has been more popular in consumer-grade systems.

Printed circuit boards may have only one or two layers of circuitry, but high-density interconnection usually implies many layers, typically eight but

possibly as many as 40. Patterns of metal are defined photolithography by means of a resist process on interlayer substrates, whereby "via" (i.e., through-sheet) connections are formed. The various layers are then "piled up" and processed to form the registered multilayer structure. For ceramic structures, the metals can be screen-printed in paste form, and the lamination is accomplished by "firing" at a high temperature (about 1600°C for alumina). Cofired ceramics undergo large material shrinkage during processing, and thus present registration difficulties in multilayer structures. For epoxy-glass boards, copper patterns are etched (or plated) on partially-cured (B-staged) epoxy, and final bonding and curing are carried out under pressure at about 200°C. Vias are formed by electroless plating, after lamination for through-hole boards and before lamination for surface-mount boards. These processes are extremely demanding because the circuits are large in area and layer-to-layer registration must be maintained.

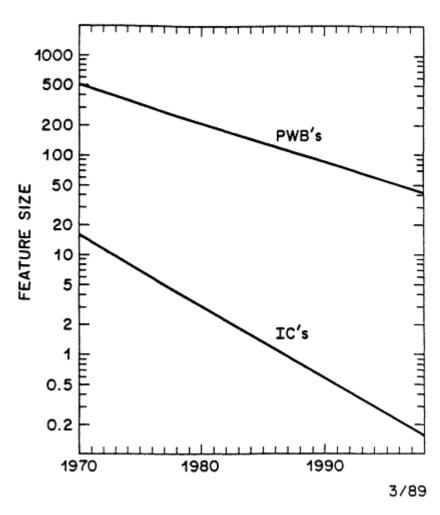

Figure 1-8 illustrates progress in chip and printed wiring board (PWB) miniaturization as measured by linear dimensions of conductor width or smallest circuit feature. Although there is much detail that is obscured by these lines, the progress is dramatic and real. Clearly, on-chip features have been reduced at a rate that consistently exceeds that for PWB patterns. Where chip features were an order of magnitude smaller in the 1960s than earlier designs, they are now nearly two orders of magnitude smaller than that. This, and other factors, will lead to an increasingly important intermediate level of interconnection. In fact, interconnect structures of intermediate size have existed right along in the form of thin-film hybrids. At this time, however, there is a great proliferation and diversity in the development of multichip modules (MCMs) that are at least a significant advance in hybrid technology and may be considered a new level of packaging. Multichip modules will probably become component-assembled on both hybrids and PWBs.

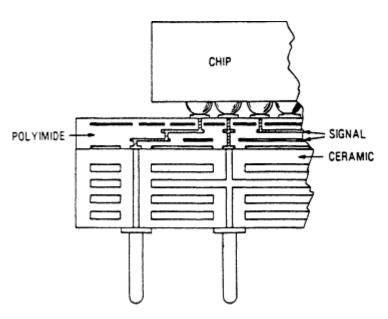

Multichip modules typically consist of a ceramic base section with power and ground planes. Interconnect circuitry is placed on top with fine metal traces, usually copper, separated by organic dielectric interlayers, usually polyimide. Because of the fineness of the signal traces, two layers on a MCM can replace many (>20) signal layers of a thick-film (screen-defined) structure.

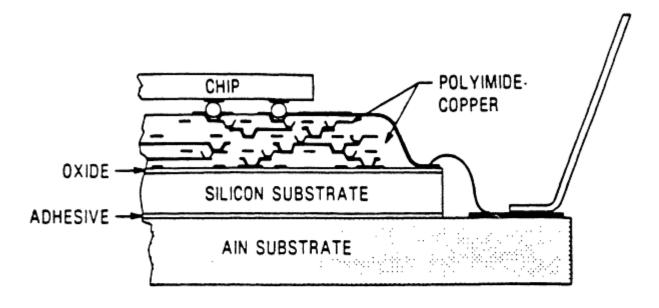

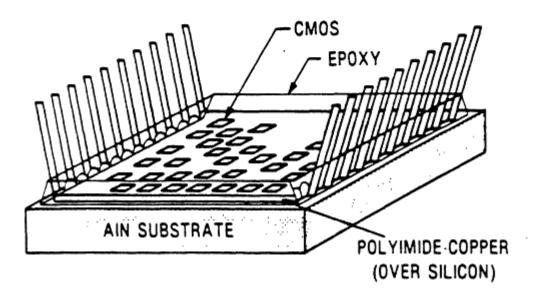

In some MCMs, silicon wafers are employed as the substrate in place of ceramic. This form of MCM should not be confused with wafer-scale integration (WSI) technology, in which both chips and interconnections are fabricated on a single silicon wafer to form an independent system or subsystem. Yields are never 100 percent, and design redundancy is an inherent feature of WSI. This is a very demanding technology, and success has not been achieved, despite vigorous and well-conceived efforts. In the MCM approach, interconnect structures are built up on the silicon wafer, and tested chips are attached. The use of pretested chips greatly reduces yield loss. It seems evident that MCMs will play a central. role in high-density electronic packaging over the next decade.

Figure 1-8

Progress in IC chip (in development) and PWB miniaturization (line widths expressed in μm). In Chapter 2 a more conservative extension of the IC line is developed.

Solder is employed for attaching chip packages to circuit board substrates. For DIP through-hole mounting, a solder wave is passed across the back side of the board (i.e., on the side with no components), which subjects the board to a brief thermal shock, although it is benign from the point of view of the components. For a surface-mount assembly, the entire structure must be brought to solder reflow temperature, which can place an unusual stress on the components. As the assembly is cooled following the soldering operation, thermal stress can arise if the thermal coefficients of expansion (TCEs) of the chip package and board substrate are not closely matched. This problem is accentuated as package size increases. When the TCEs are not well matched, the chip package must be provided with compliant leads that can adjust to the dimensional mismatches that develop with temperature changes. Conductive polymers, both isotropic and anisotropic, are being developed to replace solder, but widespread use in the next decade is unlikely.

The materials of electronic systems can be summarized in terms of relatively few basic elements and compounds. The chips are silicon with aluminum metallization, and with silicon dioxide (silica), silicon nitride, or polyimide as the dielectric. A glass (P-glass) or silicon nitride is used for passivation. The chips are packaged in epoxy molding compounds filled with silica powder. Electrical connections are made with gold wires that go from chip bonding pads to lead frames constructed of copper or an alloy of iron and nickel. The packaged chips are attached by solder to printed circuit boards composed of epoxy-glass (or sometimes polyimide) substrates that support the copper interconnection patterns. In some cases, alumina substrates are employed with interconnections of refractory metals. Connections to other boards are made through connectors composed of molded plastic (e.g., diallyl phthalate, polyphenylene sulfide, etc.) with beryllium-copper contact fingers and cables with copper conductors insulated with extruded plastic.

This summary, while substantially accurate for the great majority of circuits, fails to reveal the enormous amount of materials engineering work that makes possible the manufacture and use of electronic systems. Each material has to be carefully tailored for specific purposes, and issues of material compatibility are of critical importance. The process sequence, often involving hundreds of steps, must be such that conditions later in the manufacturing sequence do not undermine structures formed earlier. This abbreviated description includes only the materials that remain in the final product. In fact, many other materials are necessary to the processes that give rise to the structures but are not an integral part of the final structure. Process control is increasingly critical. Thus, packaging materials present challenging demands. The package must provide timing information to all parts of all chips with manageable skew. Data must be delivered to and from chips with delays that are consistent with chip circuit switching times, and an increasing number of access points are required as chips evolve. Electrical power and ground must be supplied over leads having small impedance, which translates to extremely short paths. The heat generated by the chip circuitry must be transmitted to the environment effectively, lest the chip temperature rise disastrously.

In material terms, the electrical signal paths require high-conductivity metals (e.g., copper, aluminum, gold) and low-dielectric-constant insulation materials (e.g., polyimides, epoxies, hydrocarbons, and fluorinated polymers). The speed of light is a practical limiting factor in advanced circuits. For power delivery, high-conductivity metals are again necessary, but high capacitance that is physically close (i.e., low impedance) to the chip requires high-dielectric-constant capacitor materials, usually ceramic. Thermal conductivity favors metal, whereas other ceramic paths and polymers are thermal insulators. Thermal coefficient of expansion (TCE) is a critical factor in package design. Silicon has a low TCE compared with common metals and organic polymers. Thus, mechanical stresses are created when temperature changes occur as in manufacture, temperature-cycle testing, and use. The problem becomes more difficult as chip size increases. Thinner sections of the molded body are more susceptible to thermal-mechanically induced cracking failure. TCE of polymeric materials can be controlled by the addition of low-TCE fillers, as is conventional for molding compounds and printed wiring board

resins. Many packaging and interconnection materials are composites designed to improve the TCE match.

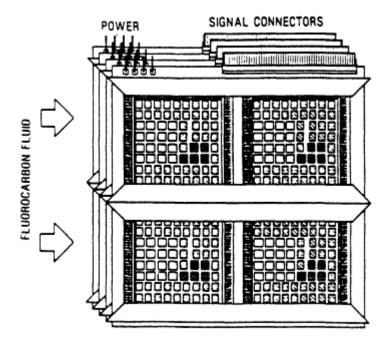

As electronic equipment density increases, power dissipation becomes an ever greater problem. In general, heat is conducted away from the chips by the thermal conductivity of the materials employed. Metals and ceramics are relatively good thermal conductors, but polymeric materials as a class are poor conductors, a factor that will assume greater importance over the next few years. The tradeoff of dielectric constant and thermal conductivity will have to be met by compromises between materials and physical design. Application of fluid heat-exchange media will also increase, but the cost of this option is high, therefore, integration of this approach into physical design is essential. Thermoelectric cooling offers an alternative to thermal conductivity, a technology that has been applied to some commercial circuits.

This report begins with a discussion of system trends and needs (Chapter 2), followed by a description of approaches that have been employed for packaging and an indication of current trends (Chapter 3). Chapter 4 discusses materials issues, and Chapter 5 gives more specific information and perspective on plastic and ceramic encapsulants, ceramic substrates, and organic printed circuit structures. Chapter 6 presents an analysis of material sources, current trends, and the importance of the field in the context of international competitiveness. These discussions lay the groundwork for the recommendations for future actions in terms of specific technical development and research, and the organizational and political factors that distinguish the United States from other countries.

About this PDF file: This new digital representation of the original work has been recomposed from XML files created from the original paper book, not from the original typesetting files. Page breaks are true to the original; line lengths, word breaks, heading styles, and other typesetting-specific formatting, however, cannot be retained, and some typographic errors may have been accidentally inserted. Please use the print version of this publication as the authoritative version for attribution.

# **Chapter 2**

# Microelectronic System Trends and Packaging Needs

Electronic systems needed in the next few years will require unprecedented packaging technology. In this chapter, the demands placed on the packages by anticipated chip technologies are discussed. In particular, the approach is to list requirements that, if met, will ensure that the inherent performance capabilities of the chips can be achieved and will not be degraded by the package. Some of these requirements deal with the interfacing of individual chips, whereas others deal with the interconnecting of groups of chips. In today's technology, these two functions are most often fulfilled by first-level packages, such as dual in-line packages, and by second-level packaging, such as printed-circuit boards, respectively.

Packaging requirements for the mid-1990s are of interest here. It is important to avoid any implicit assumption that the packages, appropriate at that time, can be categorized in the same way they are now. Indeed, there is already strong evidence that combining traditional packaging levels can lead to improved performance. For example, the IBM "thermal conduction" module eliminates one level of packaging by combining two levels into a single structure. In this chapter, those requirements that deal with interfacing individual chips are covered, as are those that deal with interconnecting several chips; the terms first-level and second-level packaging are not used. For interfacing to a single chip, the following additional requirements are important:

- · die attachment

- · chip pinout

- · pinout configuration

- · heat removal

- · signal rise time

- power lead inductance

- power supply current

- interline coupling

- protection from the environment

true Please This new digital representation of the original work has been recomposed from XML files created from the original paper book, not from the original typesetting files. Page breaks are errors may have been accidentally inserted. and some typographic be retained, cannot and other typesetting-specific formatting, however, use the print version of this publication as the authoritative version for attribution to the original; line lengths, word breaks, heading styles, About this PDF file:

For connecting two or more chips, the following additional requirements are important:

- wiring configuration

- · propagation delay

- signal rise time

Each of these requirements must be satisfied at acceptable cost and reliability, without adversely affecting the other requirements. It is assumed in this chapter that the signal-interconnection techniques do not employ multiplexing or optics, so there is exactly one electrical connection per signal (plus, perhaps, multiple ground and power pins).

It is possible to estimate many of these requirements rather accurately by extrapolating past characteristics of chips and systems, using *scaling theory* as a guide. The various types of chip scaling and the related theories are discussed in the next section. Scaling theory alone is not sufficient because different chips will be built using different architectural styles. An empirical relationship between pinout and circuit complexity, known as *Rent's rule*, can be used to characterize architectural style with sufficient accuracy for this discussion. Rent's rule and related items are also discussed in a later section.

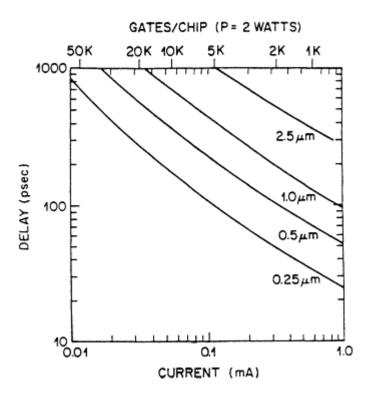

Three principal system types have been identified, each of which appears to make different demands on packaging: low-end digital, high-end digital, and high-speed. Low-end digital systems typically use silicon MOS circuits packaged separately, with printed wiring boards (PWB) for chip interconnection. High-end digital systems typically use silicon bipolar technology, often with packages in modules that carry many chips. The advent of bipolar complementary (BiCMOS) technology will blur the distinction between the two digital system types in the future, but for the purposes of this study it is assumed that **BiCMOS** will have interconnection requirements similar to **CMOS** and power requirements intermediate between CMOS and bipolar. High-speed circuits typically use gallium arsenide (GaAs) chips. The assumptions about the chip technologies are presented in later sections in this chapter. The requirements listed above are qualified, where possible, for each of the system types.

## SCALING THEORY

Scaling theory is important in understanding the driving forces that affect the trends of integrated circuit chips. The semiconductor industry learned, more than 20 years ago, that shrinking the photolithographic dimensions on the wafer and increasing the chip and wafer size increased the productivity of the semiconductor plant. The benefit to the user was lower cost per circuit, more functions per chip, and higher performance. The end result has been a quadrupling of the level of integration every 3 years. This section draws on scaling theory to permit a projection of the performance

true Please from XML files created from the original paper book, not from the original typesetting files. Page breaks are inserted. errors may have been accidentally some typographic and be retained, cannot and other typesetting-specific formatting, however, the original work has been recomposed use the print version of this publication as the authoritative version for attribution to the original; line lengths, word breaks, heading styles, This new digital representation of file: About this PDF

trends of bipolar and MOS integrated circuit chips and of generic module and board configurations. The intent is to understand the evolutionary trends and try to determine the material properties that may limit or even deadend those trends.

# Lithography

Lithography is of fundamental importance in semiconductor fabrication, and, therefore, a look at lithography is needed to get a feel for the future direction of the semiconductor industry. A key parameter is the minimum feature size that a given lithographic technology is capable of patterning on a chip at a given point in time. Minimum feature size has a first-order bearing on both circuit performance on a chip as well as the circuit density. To predict future packaging needs in the mid-1990s, it is important to have some feeling for what minimum feature size can be patterned in production in that time frame.

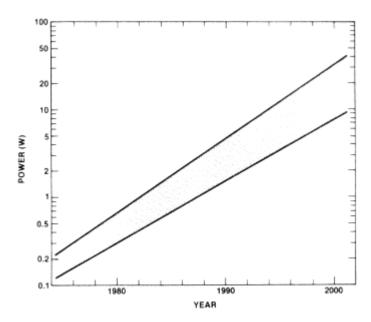

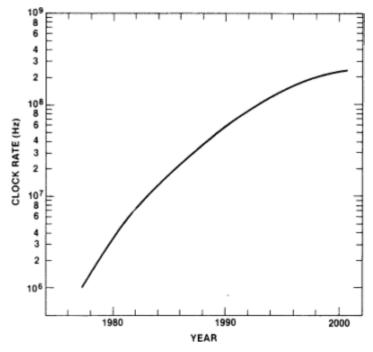

Bakoglu (1986) points out that between 1959 and 1983 the minimum feature size shrank at an average rate of 11 percent per year. Assuming that in 1988 the minimum feature size being patterned in production is about 1.0 μm, then by mid-1995, or seven years later, the minimum feature size will be about 0.5 μm. This assumes that the feature size will shrink about 10 percent per year. This is optimistic, since this dimension is near what is generally agreed to be the limit for optical lithography. It is an accepted fact that the rate of progress decreases as the limit of the technology is approached.