# Process Challenges in Compound Semiconductors (1988)

Pages 160

Size 8.5 x 10

ISBN

0309320054

Committee on Process Challenges in Compound Semiconductors; National Materials Advisory Board; Commission on Engineering and Technical Systems; National Research Council

## Visit the National Academies Press online and register for...

- ✓ Instant access to free PDF downloads of titles from the

- NATIONAL ACADEMY OF SCIENCES

- NATIONAL ACADEMY OF ENGINEERING

- INSTITUTE OF MEDICINE

- NATIONAL RESEARCH COUNCIL

- √ 10% off print titles

- Custom notification of new releases in your field of interest

- ✓ Special offers and discounts

Distribution, posting, or copying of this PDF is strictly prohibited without written permission of the National Academies Press. Unless otherwise indicated, all materials in this PDF are copyrighted by the National Academy of Sciences.

To request permission to reprint or otherwise distribute portions of this publication contact our Customer Service Department at 800-624-6242.

## NATIONAL RESEARCH COUNCIL COMMISSION ON ENGINEERING AND TECHNICAL SYSTEMS

#### NATIONAL MATERIALS ADVISORY BOARD

The purpose of the National Materials Advisory Board is the advancement of materials science and engineering in the national interest.

### **CHAIRMAN**

Dr. Bernard H. Kear Chairman, Dept. of Mechanics and Materials Science Dir., Center for Materials Synthesis College of Engineering Rutgers University P.O. Box 909 Piscataway, NJ 08854

### **PAST CHAIRMAN**

Dr. Arden L. Bement, Jr. Vice President, Technical Resources Science and Technology Dept. TRW, Inc. 1900 Richmond Road Cleveland, OH 44124

### **MEMBERS**

Dr. Norbert S. Baer Hagop Kevorkian Professor of Conservation New York University Conservation Center of the Institute of Fine Arts 14 East 78th Street New York, NY 10021

Dr. Frank W. Crossman Manager, Mechanics and Materials Engineering Lockheed Palo Alto Research Laboratory 3251 Hanover Street Palo Alto, CA 94304

Mr. Edward J. Dulis President Crucible Research Center Crucible Materials Corporation P.O. Box 88 Pittsburgh, PA 15230

Dr. James Economy Manager, Organic Polymer Research IBM Almaden Research Center 650 Harry Road San Jose, CA 95120-6099

Dr. Merton C. Flemings Professor and Chairman Department of Materials Science and Engineering Massachusetts Institute of Technology 77 Massachusetts Avenue Cambridge, MA 02139

Dr. James A. Ford Vice President, Technology SELEE Corporation P.O. Box 747 Hendersonville, NC 28739

Dr. John K. Hulm **Chief Scientist** Westinghouse Research Laboratories 1310 Beulah Road Pittsburgh, PA 15235

Dr. Melvin F. Kanninen Institute Scientist Southwest Research Institute P.O. Drawer 28510 San Antonio, TX 78284

Dr. Robert A. Laudise Director, Physical and Inorganic Chemistry Research Laboratory, Room 1A-264 AT&T Bell Laboratories Murray Hill, NJ 07974

Dr. David L. Morrison President **IIT Research Institute** 10 West 35th Street Chicago, IL 60616

Dr. Donald R. Paul Melvin H. Gertz Regents Chair in Chemical Engineering Director, Center for Polymer Research University of Texas Austin, TX 78712

Dr. Joseph L. Pentecost Professor School of Materials Engineering

Georgia Institute of Technology Atlanta, GA 30332

Dr. John P. Riggs Vice President, R&D Research Division Managing Director, Mitchell Technical Center Hoechst Celanese Corp. 86 Morris Avenue Summit, NJ 07901

Dr. Maxine L. Savitz Director Garrett Ceramic Components Division 19800 South Van Ness Ave. Torrence, CA 90509

Dr. William P. Slichter AT&T Bell Laboratories (Retired) 55 Van Doren Avenue Chatham, NJ 07928

Dr. Dale F. Stein President Michigan Technological University Houghton, MI 49931

Dr. John E. Tilton Coulter Professor Department of Mineral Economics Colorado School of Mines Golden, CO 80401

Mr. James R. Weir, Jr. Associate Director Metals & Ceramics Division Oak Ridge National Laboratory P.O. Box X Oak Ridge, TN 37830

Dr. Robert M. White Vice President, Research & Engineering

Control Data Corporation 8100 34th Avenue South Minneapolis, MN 55440

Dr. James C. Williams

Dean, Carnegie Institute of

Technology

Carnegie Mellon University

Schenley Park

Pittsburgh, PA 15213

#### NMAB STAFF

K.M. Zwilsky, Director S.M. Barkin, Assoc. Director Mary Brittain, Adm. Officer 2101 Constitution Ave., NW Washington, DC 20418

Unclassified

DO FORM 1473, 54 MAR

| SECURITY CLA             | SSIFICATION O    | F THIS PAGE                           |                                   |                                         |                                           |                       |                            |

|--------------------------|------------------|---------------------------------------|-----------------------------------|-----------------------------------------|-------------------------------------------|-----------------------|----------------------------|

|                          |                  | ·                                     | REPORT DOCUM                      | MENTATION                               | PAGE                                      |                       |                            |

| 1a. REPORT SE            | CURITY CLASS     | IFICATION                             |                                   | 16. RESTRICTIVE                         | MARKINGS                                  |                       |                            |

| Un                       | classifie        | d                                     |                                   | None                                    |                                           |                       |                            |

| 2a. SECURITY             | CLÁSSIFICATIO    | N AUTHORITY                           |                                   | 3. DISTRIBUTION                         | AVAILABILITY OF                           | FREPORT               |                            |

| 26. DECLASSIF            | CATION / DOV     | YNGRADING SCHEDU                      | LE                                | Unlimi                                  | ted                                       |                       |                            |

| 4. PERFORMIN             | G ORGANIZAT      | ION REPORT NUMBE                      | R(S)                              | 5 MONITORING                            | ORGANIZATION R                            | EPORT NUMBER          | S)                         |

| NM                       | IAB-446          | · · · · · · · · · · · · · · · · · · · |                                   |                                         |                                           |                       |                            |

|                          |                  | ORGANIZATION<br>Advisory Boat         | 6b OFFICE SYMBOL d (# applicable) | 7a. NAME OF MO<br>Department            | ONITORING ORGA<br>of Defense              | NIZATION              |                            |

| National                 | Research         | Council                               | NMA.B                             |                                         | ronautics &                               | Space Admi            | nistration                 |

| 6c ADDRESS (             | (City, State, an | d ZiP Code)                           |                                   | 7b. ADDRESS (Cit                        | y, State, and ZIP                         | Code)                 |                            |

|                          |                  | Avenue, NW                            |                                   |                                         |                                           |                       |                            |

| Washingt                 | on, D.C.         | 20418                                 |                                   | Washi                                   | ngton, DC                                 |                       |                            |

| 80. NAME OF<br>ORGANIZA  | FUNDING/SPO      | INSORING                              | 8b. OFFICE SYMBOL (If applicable) | 9. PROCUREMENT                          | T INSTRUMENT ID                           | ENTIFICATION N        | JMBER                      |

| Departme                 | nt of Def        | ense                                  | DOD/NASA                          | MDA903-86-                              |                                           |                       |                            |

| & ADDRESS (              | City, State, and | ZIP Code)                             |                                   |                                         | UNDING NUMBER                             | 15                    |                            |

| Washingt                 | on. DC           |                                       |                                   | PROGRAM<br>ELEMENT NO.                  | PROJECT<br>NO.                            | TASK<br>NO.           | WORK UNIT<br>ACCESSION NO. |

|                          | lude Security C  | 10-161-01-1                           |                                   | <u> </u>                                | <u> </u>                                  |                       | <u> </u>                   |

|                          | _                |                                       | Semiconductors                    |                                         |                                           |                       |                            |

| 12. PERSONAL<br>Committe | AUTHOR(S)        | ess Challenges                        | in Compound Se                    | miconductors                            | ······································    |                       |                            |

| 13a. TYPE OF<br>Final    |                  | 13b. TIME C                           |                                   | 14. DATE OF REPO                        | RT (Year, Month,                          |                       | COUNT<br>150               |

|                          | NTARY NOTA       |                                       |                                   | AGEGS                                   | 700                                       | <u> </u>              | 130                        |

|                          | _                |                                       |                                   |                                         |                                           |                       |                            |

|                          |                  |                                       | T                                 |                                         |                                           | <del> </del>          |                            |

| 17.                      | COSATI           | <del></del>                           | 18. SUBJECT TERMS (C              | <b>Continue on revers</b><br>Conductors | e <i>if necessary and</i>                 | l identify by blo     | ck number)                 |

| FIELD                    | GROUP            | SUB-GROUP                             | Compound semic<br>Gallum Arsenid  | e<br>1 1 1 1                            | Revice fab                                | rication              | TIIR                       |

|                          | <del></del>      | <u> </u>                              | Mercury cadmiu<br>Indium phosphi  | m telluride<br>de                       | Device fabr<br>Process tec<br>Process mod | cnnologies<br>delling | (over)                     |

| 19. ABSTRACT             | (Continue on     | reverse if necessary                  | and identify by block n           | umber)                                  |                                           |                       |                            |

| C                        | Compound s       | emiconductors                         | , such as GaAs,                   | InP, and HgC                            | dTe. are es                               | sential com           | ponents                    |

|                          | -                |                                       | electronics tec                   |                                         | -                                         |                       | -                          |

|                          | -                |                                       | ogies, attention                  | _                                       |                                           |                       |                            |

|                          |                  |                                       | se materials. T                   |                                         |                                           |                       |                            |

|                          |                  |                                       | ssing technology                  |                                         |                                           |                       |                            |

| _                        |                  |                                       | d electronic and                  |                                         |                                           |                       |                            |

|                          |                  |                                       | erm devices, but                  |                                         |                                           |                       |                            |

| generi                   | c to futu        | re components                         | and systems bas                   | ed on these                             | materials,                                |                       |                            |

|                          |                  |                                       |                                   |                                         |                                           |                       |                            |

|                          | •                | •                                     |                                   |                                         |                                           |                       |                            |

|                          |                  |                                       |                                   |                                         |                                           |                       | •                          |

| 1                        |                  |                                       |                                   |                                         |                                           |                       |                            |

| SA DETENDIN              | TYPAL / AVAIL AS | ILITY OF ABSTRACT                     |                                   | 21 ARSTRACT SE                          | CURITY CLASSIFIC                          | ATION                 |                            |

| _                        |                  | TED SAME AS                           | RPT. DTIC USERS                   |                                         |                                           |                       |                            |

|                          | F RESPONSIBLE    |                                       |                                   | <u> </u>                                | (include Area Code                        | ) 22c. OFFICE S       | YMBÓL                      |

| Jer<br>Jer               | ome Persh        |                                       |                                   | (202) 695-0                             |                                           | OUSDR&E/              |                            |

83 APR edition may be used until exhausted. All other editions are obsolete.

SECURITY CLASSIFICATION OF THIS PAGE

## Continuation of

## 18. Subject Terms

Substrates Transistor structures Interconnections Crystal growth Epitaxial structures

Epitaxial growth

Etching

Lithography

Ion implantation Dielectrics Process diagnostics Process environment

# PROCESS CHALLENGES IN COMPOUND SEMICONDUCTORS

Report of the Committee on Process Challenges in Compound Semiconductors

NATIONAL MATERIALS ADVISORY BOARD

COMMISSION ON ENGINEERING AND TECHNICAL SYSTEMS

NATIONAL RESEARCH COUNCIL

# PROPERTY OF NRC LIBRARY

OCT 0 6 1988

NMAB-446 National Academy Press Washington, D.C. 1988 Order from

National Technical

Information Service,

Springfield, Va.

22161

Order No.

Process Challenges in Compound Semiconductors http://www.nap.edu/catalog.php?record\_id=19158

1044 1037 1988

NOTICE: The project that is the subject of this report was approved by the Governing Board of the National Research Council, whose members are drawn from the councils of the National Academy of Sciences, the National Academy of Engineering, and the Institute of Medicine. The members of the committee responsible for the report were chosen for their special competences and with regard for appropriate balance.

This report has been reviewed by a group other than the authors according to procedures approved by a Report Review Committee consisting of members of the National Academy of Sciences, the National Academy of Engineering, and the Institute of Medicine.

The National Academy of Sciences is a private, nonprofit, self-perpetuating society of distinguished scholars engaged in scientific and engineering research, dedicated to the furtherance of science and technology and to their use for the general welfare. Upon the authority of the charter granted to it by the Congress in 1863, the Academy has a mandate that requires it to advise the federal government on scientific and technical matters. Dr. Frank Press is president of the National Academy of Sciences.

The National Academy of Engineering was established in 1964, under the charter of the National Academy of Sciences, as a parallel organization of outstanding engineers. It is autonomous in its administration and in the selection of its members, sharing with the National Academy of Sciences the responsibility for advising the federal government. The National Academy of Engineering also sponsors engineering programs aimed at meeting national needs, encourages education and research, and recognizes the superior achievements of engineers. Dr. Robert M. White is president of the National Academy of Engineering.

The Institute of Medicine was established in 1970 by the National Academy of Sciences to secure the services of eminent members of appropriate professions in the examination of policy matters pertaining to the health of the public. The Institute acts under the responsibility given to the National Academy of Sciences by its congressional charter to be an advisor to the federal government and, upon its own initiative, to identify issues of medical care, research, and education. Dr. Samuel O. Thier is president of the Institute of Medicine.

The National Research Council was organized by the National Academy of Sciences in 1916 to associate the broad community of science and technology with the Academy's purposes of furthering knowledge and advising the federal government. Functioning in accordance with general policies determined by the Academy, the Council has become the principal operating agency of both the National Academy of Sciences and the National Academy of Engineering in providing services to the government, the public, and the scientific and engineering communities. The Council is administered jointly by both Academies and the Institute of Medicine. Dr. Frank Press and Dr. Robert M. White are chairman and vice chairman, respectively, of the National Research Council.

This study by the National Materials Advisory Board was conducted under Contract No. MDA 903-86-K-0220 with the U.S. Department of Defense and the National Aeronautics and Space Administration.

This report is available from the Defense Technical Information Center, Cameron Station, Alexandria, VA 22304-6145.

Printed in the United States of America

### **ABSTRACT**

Compound semiconductors, such as GaAs, InP, and HgCdTe, are essential components in future photonics and microelectronics technologies. If the United States is to be competitive in these technologies, attention must be directed to the reproducible and affordable processing of these materials. This report assesses the current status of compound semiconductor processing technology and identifies factors that limit the ability to fabricate advanced electronic and optoelectronic devices. Emphasis is placed on current and near-term devices, but the process technologies discussed are generic to future components and systems based on these materials.

## **PREFACE**

Compound semiconductors offer properties and performance characteristics not readily available in silicon, the mainstay of the semiconductor industry. In particular, the development and production of optoelectronic devices and ultrahigh-speed and high-frequency devices depend on compound semiconductors such as gallium arsenide (GaAs), indium phosphide (InP), mercury cadmium telluride (HgCdTe), and related compounds.

There is considerable interest today in advancing the technology for producing these materials, and extensive dedicated effort is directed to this end by industry, government, and university laboratories. Complex structures for new applications require special processing and process control procedures. These are the limiting factors that need to be overcome, particularly in an industrial environment, if the United States is to fully realize the potential for improved technology and to maintain a competitive position in future high technology.

Specific processes sometimes are applicable to a particular material, so discussion of some processes often may involve that material only. This report is heavily biased toward GaAs and its processing because of the wide attention it is receiving today as a next-generation semiconductor material. Needless to say, other compound semiconductor materials also have important applications (e.g., InP and HgCdTe). They are addressed to show where similar problems and limitations exist in their preparation and which processing steps differ from those for GaAs.

The committee members from industry and academia represented a balance of knowledge and experience in chemistry, electronics, electrical engineering, process modeling, and materials science. In areas where gaps in members' backgrounds and experience were evident, experts outside of the committee were invited to give presentations and supply written documents on specialized topics of concern to the committee. (The guests and their areas of discussion are listed in the Acknowledgments.) This permitted the committee to fulfill its charge, which was to make an assessment of the state of the art of processing, including foreign developments in compound semiconductors; provide a discussion of new and

novel processing techniques applicable to compound semiconductor preparation; identify the of factors that today limit the effective use of these processing techniques; examine the applicability of modeling techniques to the understanding and control of processing steps, with possible prediction of materials, device, and circuit properties; and make recommendations for R&D efforts aimed at understanding the processing that could lead to improvement or elimination of existing deficiencies that limit the ability to fabricate complex structures with these materials.

This examination deals heavily with processing and the eventual control of crucial processing steps. To this end, the committee strives to direct the attention of research and production personnel, in both the military and the commercial communities, to where a concerted effort is needed to advance the present state of the art that will increase device yield and decrease production costs. The committee feels strongly that the commercial community, in particular, must be involved as a major performer in this program; but government leadership is essential to provide funding incentives and to coordinate the development of a technology base. Industry awareness of the contents of this report is essential to properly direct current and future commercial development efforts.

A. M. Glass Chairman

#### **ACKNOWLEDGMENTS**

The committee is grateful to the following individuals for their presentations to the committee and their submission of written documents for use by the committee in preparing its report: James M. Ballingall, of General Electric Company's Electronics Laboratory, who discussed commercial needs in molecular beam epitaxy; Clive A. Collins, of IBM Corporation, who discussed the role of GaAs in high-end computers; Robert Dutton, of Stanford University, who discussed modeling devices and processes; Jai K. Hakhu, of Rockwell International Corporation, who discussed how past developments in silicon technology relate to future GaAs production; William G. Howard, of Motorola, who discussed economic analysis of compound semiconductors; Kheldun R. Kahn, of BIS Mackintosh Ltd. (U.K.), who discussed market trends in compound semiconductors; Conilee G. Kirkpatrick, formerly of Rockwell International Corporation, who discussed GaAs pilot-line status and problems; Mike Malbon, of AVANTEK Inc., who discussed processing challenges in III-V process controls; Tsuneo Nakahara, of Sumitomo Electric Industries (Japan), who discussed the future of compound semiconductors in Japan; Norman E. Schumaker, of EMCORE Inc., who discussed metallo-organic chemical vapor deposition equipment; Gary Troeger, of McDonnell Douglas Microelectronics Center, who discussed GaAs pilot-line status and problems; and Robert K. Willardson, formerly of Cryscon Technologies, who discussed a supplier's view of substrates, needs, and feedback.

The government liaison representatives are thanked for participating in committee discussions and providing valuable support materials and data for committee use. They were most helpful in assisting the committee in defining the scope of the study and offering needed guidance during the development of the committee's report drafts. Special thanks go to Julian G. Blake and Harvey C. Nathanson, who, as technical advisors, made notable contributions to the report and assisted the committee in various areas of its assessment.

The chairman of the committee thanks the members for their dedication and for the patience shown during the numerous iterations and revisions of

report drafts. Particular thanks go to the committee members who served as chapter or section coordinators to assemble pertinent facts for various parts of the report and who presented the data in a timely open-minded and professional manner.

Finally, the committee gratefully acknowledges the untiring support of Dr. George Economos, the senior program officer of the National Materials Advisory Board, and his secretary, Ms. Aida Neel, in all stages of report preparation.

## COMMITTEE ON PROCESS CHALLENGES IN COMPOUND SEMICONDUCTORS

## Chairman

ALASTAIR M. GLASS, AT&T Bell Laboratories, Murray Hill, New Jersey

## Members

ROBERT A. BURMEISTER, Hewlett-Packard Laboratories, Palo Alto, California

PETER P. CHOW, Perkin Elmer Corporation, Eden Prairie, Minnesota

LESTER F. EASTMAN, Cornell University, Ithaca, New York

HARRY C. GATOS, Massachusetts Institute of Technology, Cambridge

JAMES S. HARRIS, JR., Stanford University, Stanford, California

ELLIOTT PHILOFSKY, Tegal Corporation, Novato, California

FRANZ ROSENBERGER, University of Alabama, Huntsville

WALTER M. SCOTT, Litton Electron Device Division, Tempe, Arizona

DON W. SHAW, Texas Instruments, Inc., Dallas, Texas

GREGORY E. STILLMAN, University of Illinois, Urbana-Champaign

GERALD B. STRINGFELLOW, University of Utah, Salt Lake City

WILLIAM R. WILCOX, Clarkson University, Potsdam, New York

JERRY M. WOODALL, IBM Corporation, Yorktown Heights, New York

## Technical Advisors

JULIAN G. BLAKE, Eaton Corporation, Danvers, Massachusetts

HARVEY C. NATHANSON, Westinghouse Electric Corporation, Pittsburgh, Pennsylvania

## Liaison Representatives

- THOMAS R. AuCOIN, U.S. Army Electronics Technology and Device Laboratory, Fort Monmouth, New Jersey

- JEFFREY FREY, (formerly National Science Foundation, Washington, D.C.) University of Maryland, College Park, Maryland.

- HOWARD LESSOFF, Naval Research Laboratory, Washington, D.C.

- JOSEPH P. LORENZO, Rome Air Development Center, Hanscom AFB, Massachusetts

- JEROME PERSH, Office of the Undersecretary of Defense for Research and Engineering, Washington, D.C.

- RICHARD A. REYNOLDS, Defense Advanced Research Projects Agency, Arlington, Virginia

- GERALD L. WITT, Air Force Office of Scientific Research, Bolling AFB, D.C.

## NMAB STAFF

GEORGE ECONOMOS, Senior Program Officer AIDA C. NEEL, Senior Secretary

## CONTENTS

|    |                                        | Page |

|----|----------------------------------------|------|

|    | EXECUTIVE SUMMARY                      | 1    |

| 1. | CONCLUSIONS AND RECOMMENDATIONS        | 5    |

| 2. | INTRODUCTION                           | 9    |

|    | Study Motivation                       | 9    |

|    | Why Compound Semiconductors?           | 10   |

|    | The Importance of Materials Processing | 11   |

|    | Markets                                | 12   |

|    | U.S. Competitive Position              | 16   |

|    | Proposed Solutions                     | 17   |

|    | Processing Challenges in the 1990s     | 19   |

|    | References                             | 19   |

| 3. | DEVICE ISSUES                          | 21   |

|    | Principal Recommendations              | 21   |

|    | Introduction                           | 22   |

|    | Discrete Devices                       | 25   |

|    | Size Scaling Issues                    | 35   |

|    | Device and Circuit Modeling            | 36   |

|    | Integration of Devices                 | 36   |

|    | Interconnections                       | 38   |

|    | Processing Requirements                | 38   |

|    | References                             | 40   |

| 4. | BULK SINGLE CRYSTALS AND SUBSTRATES    | 41   |

|    | Principal Recommendations              | 41   |

|    | Bulk Crystal Growth                    | 41   |

|    | Crystal Growth in Microgravity         | 46   |

|    | Substrate Quality                      | 47   |

|    | References                             | 54   |

| 5. | MODELING OF BULK CRYSTAL GROWTH        | 57   |

|    | Principal Recommendations              | 57   |

|    | Modeling Bulk Crystal Growth           | 57   |

|    | General References                     | 61   |

| 6.  | EPITAXY                                                        | 63       |

|-----|----------------------------------------------------------------|----------|

|     | Principal Recommendations                                      | 63       |

|     | Critical Role of Epitaxy for Next-Generation Devices           | 64       |

|     | Liquid Phase Epitaxy                                           | 65       |

|     | Chloride and Hydride Vapor Phase Epitaxy                       | 65       |

|     | Organometallic Vapor Phase Epitaxy                             | 67       |

|     | Molecular Beam Epitaxy                                         | 72       |

|     | Gas-Source MBE (Chemical Beam Epitaxy)                         | 77       |

|     | Growth-Related Diagnostics                                     | 78       |

|     | In Situ Processing                                             | 79       |

|     | Critical Production Issues                                     | 79       |

|     | Competitive Position References                                | 80<br>81 |

| 7.  | ETCHING AND LITHOGRAPHY                                        | 87       |

| •   | Eloning and Limodranii                                         | 0,       |

|     | Principal Recommendations                                      | 87       |

|     | Etching                                                        | 88       |

|     | Lithography                                                    | 93       |

|     | References                                                     | 95       |

| 8.  | ION IMPLANTATION AND ACTIVATION                                | 97       |

|     | Principal Recommendations                                      | 97       |

|     | Introduction                                                   | 97       |

|     | Ion Implantation                                               | 98       |

|     | Implant Activation                                             | 99       |

|     | Focused Ion Implantation                                       | 100      |

|     | Future Possibilities                                           | 101      |

|     | References                                                     | 101      |

| 9.  | DIELECTRICS AND METAL CONTACTS FOR GROUP III-V SEMICONDUCTORS  | 103      |

|     | Principal Recommendations                                      | 103      |

|     | Introduction                                                   | 104      |

|     | The Interface Problem                                          | 104      |

|     | Highlights of the Current State of the Art                     | 106      |

|     | Recent U.S. Research                                           | 109      |

|     | References                                                     | 111      |

| 10. | SPECIAL CONSIDERATIONS FOR GROUP II-VI COMPOUND SEMICONDUCTORS | 115      |

|     | Principal Recommendations .                                    | 115      |

|     | Introduction                                                   | 116      |

|     | HgCdTe Device Issues                                           | 117      |

|     | Substrate Technology                                           | 119      |

|     | Epitaxial Growth                                               | 122      |

## **EXECUTIVE SUMMARY**

The rapid decline of the U.S. semiconductor industry in global markets has received national attention. In an attempt to halt this decline, a number of collaborative initiatives have been established that combine the resources of industry, universities, and the government. These include the Semiconductor Research Corporation (SRC), the Microelectronics and Computer Corporation (MCC), and the Semiconductor Industries Association consortium known as SEMATECH. All of these major initiatives address only silicon technology, a technology with substantial existing commercial markets.

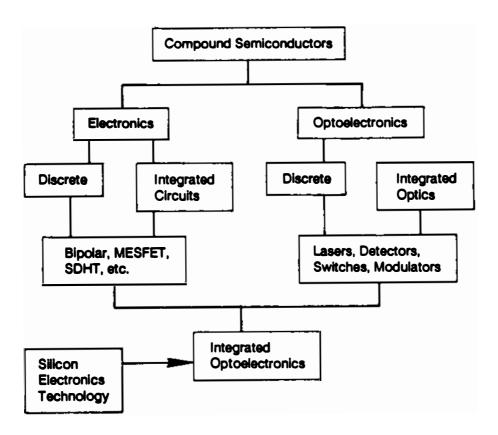

The next generation of advanced microelectronics and optoelectronics technology will use compound semiconductors such as gallium arsenide, indium phosphide, and mercury cadmium telluride. For these semiconductors, the current markets are small and are driven primarily by military requirements; the manufacturing technologies are only in early stages of development. Yet compound semiconductors have unique capabilities, not achievable with silicon, that will be vital for the next generation of ultrahigh-speed computers, microwave generation, and optical communication. Integrated optoelectronic devices for high-speed switching and information processing are now emerging from research laboratories, but the processing science and technologies necessary to manufacture such devices are in their infancy.

To avoid loss of these technologies to overseas competitors, proper attention must be given to these advanced technologies <u>now</u>. A coordinated national strategy must be formulated that makes the best use of existing resources to establish the technology base necessary to capitalize on the opportunities presented by these materials.

The Committee on Process Challenges in Compound Semiconductors was established to examine the current status of compound semiconductor processing technology and to identify factors that currently limit the ability to fabricate advanced electronic and optoelectronic devices. These factors include limitations in fundamental understanding of materials and processes, and processing equipment. In addition, the committee was asked to make a comparative assessment of foreign developments in this field.

Processing of compound semiconductors is not a straightforward extension of silicon technology. Factors such as lattice mismatch, surface passivation, vapor pressure differences of the constituent elements, and stoichiometric defects all add to the complexity of material preparation and device fabrication. Opportunities presented by composite, artificially-structured materials, which permit the design of specific optical and electronic properties, need special attention. The report addresses only those issues specific to compound semiconductors that cannot be directly transferred from silicon technology. These include issues such as substrate growth and preparation, epitaxy, etching, lithography, dielectric films, and metallization.

It became evident during this examination that a major obstacle to the affordable, high-yield manufacture of compound semiconductors is the serious lack of understanding of relationships among the materials properties, the various processing parameters, and the eventual device yield and performance. Improved understanding requires coordinated interdisciplinary research and development, including disciplines of chemistry, physics, surface science, chemical, mechanical and electrical engineering, together with parallel theoretical modeling of the equipment and processes used in compound semiconductor device production. A number of uncoordinated subcritical research and development efforts are currently funded in the United States that have overlapping programs and are generally not close enough to the device manufacturing line to optimize process technology for improving device yield. The throughput of commercial device lines is often too small to establish proper process control. Communication of processing technology between R&D centers is poor. A better coordination of these programs is essential to the advancement of the technology.

Because of these factors, the committee believes that the federal government must play a leadership role in partnership with the private sector and academia. Although defense needs currently account for the major market share of U.S. compound semiconductor materials and devices, the potential exists for large commercial markets in the future. The fabrication of low cost, high yield, high stability devices and circuits is an essential prerequisite to expanding commercial markets for compound semiconductors. In the nearer term (within 5 years), these markets will include high speed electronic circuits for computations and information processing, satellite communications, and wide bandwidth circuits, also components for optical communications. In the longer term (5 years and beyond), it is anticipated that photonic and electronic devices will become mutually compatible components of integrated optoelectronic systems for ultrahigh throughput information processing. Just as the growth of high technology over the last two decades has been closely linked to advances in silicon materials processing technology, so will future progress be closely dependent on compound semiconductor processing technology. A long-term focused U.S. commitment to this technology is required to avoid total dependence on overseas technology.

Research and development <u>coordination</u> and close coupling feedback of the materials research with the processing and device communities are the most important components in helping correct the domestic industry's decline. This includes coordinating the activities of the university research centers with those of the government and industrial centers. In addition, focus of the research effort must be directed toward a commercial technology base, since this is the essential link for establishing and maintaining a viable defense industrial base.

Administering and staffing of new technology centers is an area needing further assessment; a MITI-style approach of sharing staff between such centers has not been tested in the United States and, with some modifications, this approach may find productive application in these centers.

#### CHAPTER 1

### CONCLUSIONS AND RECOMMENDATIONS

The advantages of compound semiconductors, such as gallium arsenide (GaAs), indium phosphide (InP), and mercury cadmium telluride (HgCdTe) for use in optoelectronic devices and in ultrahigh-speed or high-frequency electronic devices, are well established. In these areas, compound semiconductor devices provide unique performance enhancements over the capabilities of silicon devices. Components based on these materials will be vital elements in commercial and military electronic systems. Realization of the enhanced performance of compound semiconductors has, however, been greatly hampered by difficulties in developing the appropriate process technology base to achieve the high yield, high performance, and high reliability necessary for these materials to take a place alongside silicon.

Major research advances in recent years have demonstrated new physical phenomena, improved materials, and new device concepts. Many of these involve the fabrication of multilayer structures for quantum well lasers and detectors, high-electron-mobility devices, and nonlinear optical switching devices. Equipment has been developed for the fabrication of such exploratory devices, but these are generally customized instruments for the research laboratory and are not well suited to the manufacturing environment.

In contrast to the dramatic progress in the research arena, the development of the process-technology base has been slow, and thus commercial exploitation of the science base is lagging. There is currently little firm understanding of the relationships among material parameters, process parameters, and device performance. Consequently, there is little standardization of procedures for fabricating even the simplest devices, including the initial step of substrate specification and certification. The size of the current market for compound semiconductor devices, particularly electronic devices, is not sufficiently attractive to sustain the necessary large-scale investment

NOTE: A Glossary is appended at the end of this report that explains many of the acronyms and abbreviations contained in the text.

and development efforts--especially in the small companies that dominate this field. Unless the present U.S. government support structure is modified, the committee does not see any significant near-term prospects for closing the ever-widening gap between research and manufacture.

This is not the case in Japan. The Japanese electronics industry has targeted compound semiconductor technology with the intent of gaining a large market share of future products and systems that use this technology. This is a long-term goal, with government-coordinated research and development that began in the late 1970s and was not tied to short-term deliverables. Japan increased its share of world silicon-based semiconductor markets from a small fraction 10 years ago to over 50 percent today. The fraction is estimated to be greater than 75 percent in the new compound semiconductor-based markets. Because of its emphasis on manufacturing technology, Japan is better poised than the United States to take advantage of new market developments, as they did a few years ago in the case of GaAs lasers for compact disk recorders and InGaAsP lasers for lightwave communication. Current Japanese dominance in compound semiconductor technology will contribute substantially to Japan's dominance of high-technology telecommunications and computer systems of the future. If corrective action is not taken, the equivalent U.S. materials, components, and systems businesses will not grow or even survive.

It is imperative that programs be directed toward advancing the state of the art of compound semiconductor processing technology and attaining the proper degree of process control necessary to reliably and reproducibly manufacture structures on a commercial scale. Processes developed for one compound semiconductor such as GaAs are often directly applicable to others--InP, InGaAs, and CdTe--with only minor modifications. Furthermore, processes developed for current technology are prerequisites for the more complex device structures of the future.

In this report, recommendations specific to individual processes are listed at the beginning of each chapter. These recommendations are directed to industrial R&D management as well as to government funding agencies. However, the following general technical recommendations set forth by the committee represent a first priority to achieve an effective technology and competitive international position in compound semiconductor manufacture:

- Establish programs to clarify the relationships between the crystal growth and subsequent processing procedures and the device yield and performance. Close interaction and feedback between each step of semiconductor fabrication is vital to understanding how each processing step is affected by the preceding process history.

- Establish detailed specifications for individual materials, processes, and equipment. This includes specifications for substrates,

epitaxial layers, etchants, lithographic processes, ion implantation, and metallization, as outlined in individual chapters that follow.

- Develop equipment and processes suitable for the manufacturing environment for the low-cost, high-yield fabrication of compound semiconductor devices.

- Develop techniques for in situ and in-process control. This must include intelligent control systems and theoretical modeling of the processes as well as a broad range of experimental diagnostics.

These technical issues require the integration of efforts of equipment manufacturers, materials suppliers, research and development organizations, and semiconductor fabrication lines. While market forces drive development of 1- to 2-year deliverables, 2- to 5-year development is not adequately supported, either by the private sector or by the government. Long-term commitment to product development is essential for success. Government incentives are particularly appropriate, since defense needs today account for the major market share of GaAs and virtually all II-VI materials and devices. Significantly greater coordination among U.S. participants in the compound semiconductor area is strongly recommended. In this respect, the federal government must play a leadership role but in partnership with private-sector industry and academia. The committee therefore believes that the following actions are appropriate to optimize the use of national resources:

- Establish a prestigious national review panel consisting of industrial, university, and government engineers and scientists to (a) develop a national compound semiconductor strategy, (b) coordinate activities and funding, and (c) make appropriate recommendations for R&D. The present procedure of overlapping programs, often poorly coordinated and too often tied to narrow and short-term interests of specific industries or government agencies, should be eliminated.

- Establish critically funded technology centers with joint industry and university participation. Successful operation of such centers depends heavily on the selection and coordination of projects and on the level of funding. This, in turn, will influence the level of industrial commitment.

The committee endorses the 1987 proposal of the Defense Science Board and IEEE/DARPA Strategic Materials Initiative for centers of this kind. Such centers for the expansion of the national technology base are analogous to existing national centers for the advancement of basic science. It is proposed that

• University engineering research centers, such as the NSF-ERC programs, be coordinated with the technology centers suggested earlier and with existing DOD ManTech centers. Academic programs at the B.S. level as

well as the Ph.D. level in materials processing and manufacturing sciences are necessary to increase the availability of appropriately qualified students.

• Greater emphasis be placed on using the existing government-funded pilot lines as a national facility to solve the technical issues outlined earlier.

Industry-government partnership is essential. Military requirements often are aimed at high-performance specialized products with little regard for cost. The United States cannot sustain a vigorous defense industry without a healthy commercial industry. It is therefore vital that future emphasis be placed on cost, yield, and manufacturability of compound semiconductors.

## CHAPTER 2

## INTRODUCTION

Compound semiconductors will be essential elements in electronics areas of ultrahigh-frequency computation, microwave generation, and optical transmission. The future potential of novel structures for integrated optoelectronic devices for high-speed switching and information processing has just begun to be realized in the research laboratory. Unless substantial changes occur very soon in the way products are identified and brought from the research laboratory to the marketplace, control of these technologies is destined to move offshore during the 1990s. The loss of this critical technology will adversely affect U.S. competitiveness in avionics, computers, and information systems.

Current commercial markets for these products are small. Leadership by the federal government is required for developing the necessary technology base to produce high-yield, low-cost devices. In this report, the committee makes a critical assessment of compound semiconductor processing technology and identifies technical factors that limit our ability to manufacture low-cost, high-yield devices and circuits. In addition, the committee proposes a "recovery" plan of cooperative research that includes (a) the establishment of a national review panel to coordinate R&D in compound semiconductors, (b) the establishment of national technology centers, and (c) the establishment of university engineering centers to train students at all levels in this key area.

## STUDY MOTIVATION

A number of reports have been published recently that address the status of U.S. microelectronics research and development [Office of Technology Assessment, 1986], the competitive position of the U.S. semiconductor industry [National Materials Advisory Board, 1986; Federation of Materials Societies, 1986; JTECH, 1985], the impact of cooperative research in Japan on its microelectronics industry [Merz, 1986], a possible approach to cooperative research in the United States [McLoughlin and Miller, 1987], the benefits and risks associated with federal funding of a consortium of electronics industries [Congressional Budget Office, 1987], and an examination of the roles that the National Laboratories may play to reverse the current decline of the U.S.

semiconductor industry [National Materials Advisory Board and Manufacturing Studies Board, 1987].

This report differs from these others in that it addresses the current state of the art of the processing of compound semiconductors and identifies factors that limit the ability to fabricate reproducible, low-cost devices. It also assesses the present scientific status of U.S. and foreign compound semiconductor materials and the processes used to fabricate devices. It is evident, however, that, to make significant advances in compound semiconductor technology, it is not sufficient to identify deficiencies in U.S. scientific knowledge and technical capabilites; it is also necessary to consider improvements in the way research and development is done. The committee makes some recommendations on future research and development as well as on how to make better use of U.S. national resources.

## WHY COMPOUND SEMICONDUCTORS?

Current electronics technology is dominated by the elemental semiconductor, silicon. However, with the ever-increasing need for devices with higher speeds and higher levels of integration, the limitations of entirely silicon-based electronics are becoming evident. Compound semiconductors will become increasingly important in advanced technologies because of their intrinsically higher speeds, lower power requirements, optoelectronic capabilities, and greater resistance to high-energy radiation. The higher electron velocity in compound semiconductors translates directly into greater operating frequencies and greater computation speeds using the same design rules as silicon. For high-speed computational and microwave devices, GaAs is currently the material of choice. The band structure of GaAs, InP, and related binary, ternary, and quaternary compound semiconductors permits the fabrication of efficient light-emitting structures (lasers and light-emitting diodes) of current importance for optical communication, optical interconnection of electronic chips, and consumer products such as compact disk players.

Beyond current technology, compound semiconductors offer a wide variety of new and versatile devices for future systems. By growing multilayer structures of alternating composition on the scale of a hundred angstroms (10 nm), entirely new material properties can be designed for use in optical and electronic devices. The electronic band structure of such composite materials can be tailored to meet specific requirements such as wavelength of operation or ultrahigh-speed electron transport, properties that are not attainable with an individual semiconductor. Optoelectronic circuits can be designed in which optical and electrical components are integrated on a semiconductor chip to fully capitalize on the advantages of each technology. These are areas of great potential that will evolve from current compound semiconductor technology, and they represent an exciting window on future high-performance electronic and photonic systems.

Compound semiconductor technology today is handicapped by the absence of a commercial market to provide the driving force for upgrading domestic device processing capabilities. Silicon processing technology does not generally apply to the fabrication of compound semiconductor devices. Factors that do not arise in silicon technology, such as lattice mismatch, surface passivation, vapor pressure differences of the constituent elements, and stoichiometry-related defects, in compound semiconductor technology require special crystal growth methods, processing procedures, and process control. Many of these processes need further development, and the currently limiting factors of process control must be overcome. This is particularly true in the manufacturing environment, where cost-sensitive issues such as device yield determine product viability.

Since GaAs is the most important of the compound semiconductors in terms of current market needs, emphasis is placed on that material system in this report. However, InP and InGaAsP alloys are currently of primary importance for optical communication devices, and HgCdTe alloys are the semiconductor systems of choice for infrared imaging devices. Many of the processing challenges confronting GaAs manufacture apply equally well to these other compound semiconductors. Where there are significantly different problems for different materials systems, these are addressed individually. As compound semiconductor technology advances, these newer technologies will play an increasingly important role in the total picture. At present, these other materials are much less mature in their development than GaAs, and their full potential cannot be readily assessed.

## THE IMPORTANCE OF MATERIALS PROCESSING

The fabrication of compound semiconductors involves a large number of processing steps starting with the growth and preparation of substrates upon which devices and circuits are constructed. Subsequent processing steps may include the epitaxial growth of thin semiconductor layers, etching and lithography to define two-dimensional features on the semiconductor surface, ion implantation to create the appropriate electrical activity in the semiconductor, and the deposition of metallic conductors or dielectric insulators. Each of these processes must be precisely controlled to achieve reproducible characteristics.

Silicon processing technology generally cannot be applied to the fabrication of compound semiconductor devices. Factors that do not arise in silicon technology, such as lattice mismatch, surface passivation, vapor pressure differences of the constituent elements, and stoichiometry-related defects in compound semiconductor technology, require special crystal growth methods, processing procedures, and process control. However, one of the most serious issues in process control is the lack of understanding of the manner in which one processing step can influence subsequent steps and the eventual device yield. For instance,

the electrical characteristics of devices can be affected by strains and compositional uniformities that may be introduced during substrate growth and preparation, epitaxy, ion implantation, or metallization. The activity and distribution of implanted dopants are likewise influenced by stress, composition, thermal history, and the properties of dielectric encapsulants.

The cost of semiconductor devices is largely determined by the eventual yield of devices and circuits. For new devices, yields may be only a few percent. Since hundreds of devices are typically fabricated on a single wafer, material or dimensional non-uniformities can critically affect device yield.

As devices become more complex, as the number of processing steps increases, and as the size of substrates increases, precise control of each process becomes even more critical. At the present time, many of the processes need further development and the currently limiting factors of process control must be overcome. These controls are in the manufacturing environment where device yield and volume determine product availability.

## **MARKETS**

Current markets for GaAs and growth projections into the 1990s are given in Table 2.1. The table was derived from Sumitomo Electric Industries data, and is largely consistent with data derived from other U.S. and European sources. At present, the largest market is in optoelectronic devices for communication systems and consumer markets (e.g., display and compact disk). While GaAs-based products are the largest volume markets, higher priced InP/GaAs products account for a significant fraction of the dollar amount. The worldwide market for lightwave components in 1986 was about \$1 billion--about one-third being for long-haul transmission, one-half for short-haul (e.g., local area network, loop, computer network, and metropolitan area transmission), and less than 20 percent for the military. By 1992, the market in compound semiconductor optoelectronic devices is expected to increase to more than \$4 billion, and lightwave systems, dependent on these devices, will be considerably greater than that figure.

The current GaAs integrated circuit market, in contrast, is largely driven by military needs. In 1985, over 75 percent of the \$1.2 billion (\$900 million) GaAs-IC market was military (20 percent digital, 80 percent analogue microwave). At present, most U.S. military electronics and systems companies are deeply involved in in-house efforts to demonstrate the applicability of GaAs systems by the late 1990s. Because of its ability to generate high-power, low-noise microwave signals in the 10 to 100 GHz spectrum, GaAs promises to revolutionize electronic warfare, space and terrestrial communication systems, phased array radar, commercial high-resolution television, and satellite communication.

TABLE 2.1 Worldwide Merchant Market Projections for Some Compound Semiconductor Devices (\$ Million/Year)

| 1985 | 1990        | 1995                  |

|------|-------------|-----------------------|

| 1400 | 3800        | 8200                  |

| 300  | 1200        | 4100                  |

| 1100 | 2600        | 4100                  |

|      | 1400<br>300 | 1400 3800<br>300 1200 |

Source: Private communication to the committee by T. Nakahara, Sumitomo Electric Industries, Ltd. (Japan), January 1987.

Estimating the growth of the GaAs-IC market is difficult. Market research has resulted in figures of \$3.8 billion in 1990 and projected to be greater than \$8 billion in 1995, but extrapolations of this magnitude are inevitably subject to huge errors. Market research places the majority of this growth anticipated in digital ICs (about 50 percent of the GaAs-IC market by 1990), with the military share falling to less than 30 percent. Such projections appear to be an optimistic assessment of market parameters.

The importance of these data lies in the fact that defense is currently, and will continue to be, an important driving force of the GaAs-IC technology--much larger than the 5 percent defense-related portion of the silicon market that occurred during the 1960 to 1985 period of explosive growth in the silicon industry. Thus, a significantly higher percentage of government participation in the development of GaAs technology is required. Civilian markets for GaAs-ICs are now very small and insufficient to support the large long-term investment required for development and manufacture of GaAs-ICs. A large generic market is needed and must be created to drive the required industrial investment. The cost of a GaAs chip can be as much as 10 to 20 times that of a silicon chip. Silicon bipolar technology continues to advance, and it is not yet clear how effectively the speed advantage of GaAs devices can be used in applications such as high-end computers, where interconnection delays are as important as device delays in current circuit architectures. As architectures are modified to make use of optical interconnections, the advantages of the higher intrinsic speed of GaAs will become increasingly evident in digital systems. In the long term, it can be anticipated that photonic and electronic devices will become mutually compatible components in fully integrated optoelectronic circuits and systems.

Compound semiconductor substrate market projections from 1985 to 1995 are given in Table 2.2. The table shows that the total market is quite small and insufficient to sustain the large number of materials suppliers. Today, there are 15 U.S. companies and 11 overseas companies selling GaAs wafers. In the United States, these are mostly small companies, whereas in Japan they are large companies with a majority of the market share. Currently the largest market (about 80 percent) is for optical devices that use horizontal Bridgman-grown (HB) GaAs. Liquid-encapsulated Czochralski-grown (LEC) GaAs accounts for only about 25 percent of the current GaAs market, but the growth of the market for LEC material is expected to expand much more rapidly than that for HB wafers.

The market for LEC InP for optical devices is relatively small and is expected to grow from \$10 million in 1985 to \$50 million in 1990. Indium phosphide research has shown impressive progress in millimeter wave devices as well as in lightwave devices; however, the long-term growth of the market compared to GaAs cannot be reliably assessed. At present, there is only one small U.S. commercial supplier of InP.

TABLE 2.2 Worldwide Merchant Market Projections for III-V Semiconductor Materials (\$ Million/Year)

| Category    | 1985 | 1990 | 1995 |

|-------------|------|------|------|

| Total III-V | 120  | 420  | 920  |

| GaAs        | 70   | 300  | 660  |

| GaP         | 40   | 70   | 150  |

| InP         | 10   | 50   | 110  |

Source: Private communication to the committee by T. Nakahara, Sumitomo Electric Industries, Ltd. (Japan), January 1987.

### U.S. COMPETITIVE POSITION

There have been many studies of the U.S. competitive position in compound semiconductors and the electronic industry in general. All of these reflect U.S. concerns about the increasing Japanese presence in this industry [National Materials Advisory Board, 1986; Federation of Materials Societies, 1986; JTECH, 1985]. A common conclusion of each study is that in the past 5 years Japan has greatly increased its share of the compound semiconductor market and is beginning to dominate the technology in several key areas. The Japanese have targeted optoelectronics as a key technology, and their long-term objective is to claim a large market share.

One principal problem facing the United States in the GaAs arena is the need to establish manufacturing resources and the needed production experience that will significantly lower the cost of GaAs components. Although GaAs chips presently may have better performance than silicon, their cost can be as much as 10 to 20 times greater than that of a similar silicon chip. In some highly specialized, critical applications, cost is a minor limitation, and the material of choice depends on achieving exceptional performance. For most commercial applications, however, cost is a success-determining factor. Either the performance must be increased to justify the current price or the cost must be reduced to a level consistent with alternative technologies and with market demands for the available performance enhancements.

In a climate driven by profit, U.S. manufacturers are generally unwilling to invest large sums in manufacturing plants until a large generic market develops. Unfortunately, until a truly generic area that has very large volume potential is identified (either digital or linear), the costs per unit for GaAs parts will remain high. High-volume U.S. customers are rare today, so the economy of high production is absent, causing prices to remain high, which limits applicability, and so on.

In contrast, the Japanese have made a long-term, strategic commitment to compound semiconductor technology. As early as 1985, companies like Sumitomo Electric Industries and Dowa Mining Co. were already producing 10,000 2-inch GaAs wafers per month. Furukawa Mining Ltd., Iwaki Semiconductor, Mitsubishi Metal, and again Sumitomo Electric are all now shipping 3-inch wafers and targeted 4-inch material production for early 1987 (private communication to the committee by T. Nakahara, January 1987). In the area of devices, the Japanese are widening the gap with the United States in device manufacturability of complex parts. Examples are the NTT distributed feedback laser, the Oki Electric 8x8-bit multiplier, the NTT 16K static RAM, or the Fujitsu high-electron-mobility 16K memory operating at room temperature (four times faster than the equivalent 16K silicon part).

One key to Japanese pre-eminence in this field is dedication to manufacturability issues, where they are focusing on the design of cleanrooms, the right level of (robotic) automation, the use of on-line control and process feedback, and, perhaps most importantly, the proper level of investment in equipment development. The ability to make the proper long-range investment in equipment, processes, and people--whether it is in crystal growth, epitaxial growth, or strategically pure starting materials--is a true Japanese strength.

The committee estimates that the United States is well behind Japan in the optoelectonic sector and the digital logic sector of GaAs technology. In the field of linear, monolithic microwave ICs, there is approximate parity [Defense Science Board, 1987]. In the development of many of the processing technologies discussed in this report, the United States is trailing, and the gap is widening. It can be anticipated that, without any U.S. corrective action, Japanese superiority in compound semiconductor devices will mean eventual Japanese superiority in electronic and optoelectronic systems. Action is necessary to coordinate U.S. government, industrial, and academic resources in such a way as to reverse this erosion quickly and definitively.

### PROPOSED SOLUTIONS

The committee feels that a strong U.S. position in compound semiconductor manufacturing technology is essential for future economic health in high technology. In the long term, compound semiconductors will clearly perform a critical complementary role to silicon technology. It is particularly dangerous to ignore the smaller near-term markets and permit overseas dominance. This will inevitably lead to U.S. inability to compete in large future systems markets. However, U.S. industry finds it difficult to make the necessary long-term investments. As a result, solutions will require government leadership.

In the committee's opinion, the following action warrant service consideration to strengthen U.S. competitiveness in the field of compound semiconductors:

- Establishment of a national review panel on compound semiconductors, consisting of members from industry, universities, and government. The functions of the panel should include (a) the formulation of a national strategy for compound semiconductors, (b) the coordination of research and development activities and funding, and (c) presenting recommendations for research and development actions. This panel should increase government agency, industrial, and academic cooperation in targeting and accomplishing significant goals, while eliminating duplicative programs.

- Establishment of a federal-commercial compound semiconductor technology center, funded at a sufficiently high level to attract

industrial participation. Its purpose would be to establish a common technology for the manufacture of compound semiconductor materials and devices for commercial and military use.

■ Establishment of university research centers to train bachelor's, master's, and doctoral students in manufacturing technology. Such programs could include personnel and information exchange agreements with other technology centers.

These recommendations are essentially similar to those forwarded to solve the problems of the silicon industry, which indeed suffers from similar problems [McLoughlin and Miller, 1987]. However, the absence of a large existing market for compound semiconductor devices and the vital importance of these materials to future technology makes the case for federal support of compound semiconductor technology even stronger than that for silicon. Thus, all of the advantages considered in the proposed federal support of the SEMATECH proposal [Congressional Budget Office, 1987], such as overcoming the semiconductor industry's shortcomings in manufacturing technology and creating public benefits both in national security and commercial competitiveness, are especially applicable to compound semiconductors. At the same time the risks related to special advantages derived by member companies would appear to be reduced because of the immature state of the technology under development.

Federally administered centers concentrating on improving the U.S. innovative and manufacturing position in compound semiconductors also have been proposed in an IEEE and DARPA Strategic Materials Initiative and discussed in the recent Defense Science Board report on semiconductor dependency [Defense Science Board, 1987]. Legislation has already been introduced into Congress concerned with semiconductor manufacturing. Such legislation is viewed as an important first step toward strengthening the U.S. semiconductor industry. For compound semiconductors, this is particularly necessary, since the defense industry is currently the largest consumer of compound semiconductor electronic devices.

In the implementation of these recommendations, a most important component must be the <u>coordination</u> of research and development and the close coupling and feedback of the materials research with the processing and device fabrication communities. University research centers must be closely coordinated with the government and industrial centers. It is essential that these industry-university-government partnerships be selective, consistent, and planned with appropriate lifetimes to see the projects through from the start-up to a timely phase-out. It is also vital that the focus of the research be directed toward a commercial technology base, since this also is considered essential for a viable defense industry. The administration and staffing of new technology centers is an important issue requiring further study. The MITI-style approach [Merz, 1986] to sharing staff between such centers and industry has not been tested in the United States, where wide geographical differences exist.

#### PROCESSING CHALLENGES IN THE 1990s

In the following chapters of this report, the technical issues involved in the fabrication, reliability, and manufacturability of compound semiconductors are discussed. The chapters that follow begin with a discussion of device issues and then describes typical devices of current interest to provide an insight into the importance of each of the processing technologies, as well as an understanding of the unique advantages of compound semiconductors. The state of the art of each process technology is assessed, with emphasis on materials of greatest importance to the commercial development of future electronic and optoelectronic systems--namely, GaAs, GaAlAs, InP, InGaAsP, and HgCdTe.

Each of the processes of importance for device fabrication is discussed individually in succeeding chapters. Because of their great significance, separate discussions are devoted to issues of process control and the process environment, to interactions between the various processing steps, and to eventual device yield and performance.

In each case, current problems that need to be solved over the next few years are considered, and areas where fundamental understanding is deficient are identified. Attempts are made to identify the relationships between the material properties (defects, etc.) and processing procedures and the device performance and yield. Progress in this area of processing science will have immediate impact on manufacturing technology.

## **REFERENCES**

- Congressional Budget Office. 1987. The Benefits and Risks of Federal Funding for <u>Sematech</u>. U.S. Congress, Congressional Budget Office, Washington, D.C., September.

- Defense Science Board. 1987. Defense Semiconductor Dependency. Washington, D.C., February.

- Federation of Materials Societies. 1986. Electronic Materials: A Key to U.S. Competitiveness. Workshop Summary of the Federation of Materials Societies, Washington, D.C., 2/26/86.

- JTECH. 1985. Panel Report on Opto and Microelectronics. Scientific Application International Corp., La Jolla, California, JTECH-TAR 8403.

- McLoughlin, G. S., and N. M. Miller. 1987. The U.S. Semiconductor Industry and the <u>Sematech</u> Proposal. Congressional Research Service, Library of Congress, 87-354 SPR, Washington, D.C., April.

- Merz, J. L. 1986. The opto-electronics joint research laboratory: Light shed on cooperative research in Japan. Scientific Bulletin (Office of Naval Research Far East Office) 11(4[Oct.-Dec.]):1-30.

- National Materials Advisory Board. 1986. Advanced Processing of Electronic Materials in the United States and Japan. National Academy of Sciences State-of-the-Art Review. Washington, D.C.: National Academy Press.

- National Materials Advisory Board and Manufacturing Studies Board. 1987.

The Semiconductor Industry and the National Laboratories. Washington,

D.C.: National Academy Press.

- Office of Technology Assessment. 1986. Microelectronics Research and Development--A Background Paper. U.S. Congress, Office of Technology Assessment, OTA-BP-CIT-40, Washington, D.C.

## CHAPTER 3

### **DEVICE ISSUES**

#### PRINCIPAL RECOMMENDATIONS

Typical optical and electronic device structures of importance in compound semiconductor technology are described in this chapter, with particular emphasis on the processing issues that are critical to optimum device performance. It is vital that the device community fully recognize the importance of materials processing and testing for successful fabrication and operation of future high-performance electronic and optoelectronic devices.

Although most current commercial compound semiconductor devices are either discrete components or are used in relatively low levels of integration, the ultimate goal of compound semiconductor technology is the full integration of both photonics and electronics technologies for high-speed information processing and transmission. To achieve this goal, full control over the processing of discrete optical and electronic devices is an essential prerequisite. This chapter provides insight into why precise control of materials and process parameters is vital to the advancement of compound semiconductor technology.

The combination of different compound semiconductors in heterojunctions and small dimensions, where quantum effects dominate, has already led to a number of conceptual breakthroughs for new devices and circuits. Such breakthroughs are expected to continue. However, the ability to capitalize on new opportunities and make them a practical reality is severely restricted by current limitations in materials processing technology.